CMOS low-power consumption, low offset voltage, low return-stroke noise comparator

A technology with offset voltage and low power consumption, which is applied in the field of wireless communication systems, can solve the problems of complex control clock phase, difficulty in obtaining conversion speed, and increased clock cost, so as to optimize the design of transistor size, eliminate slew rate restrictions, reduce The effect of small overdrive recovery time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

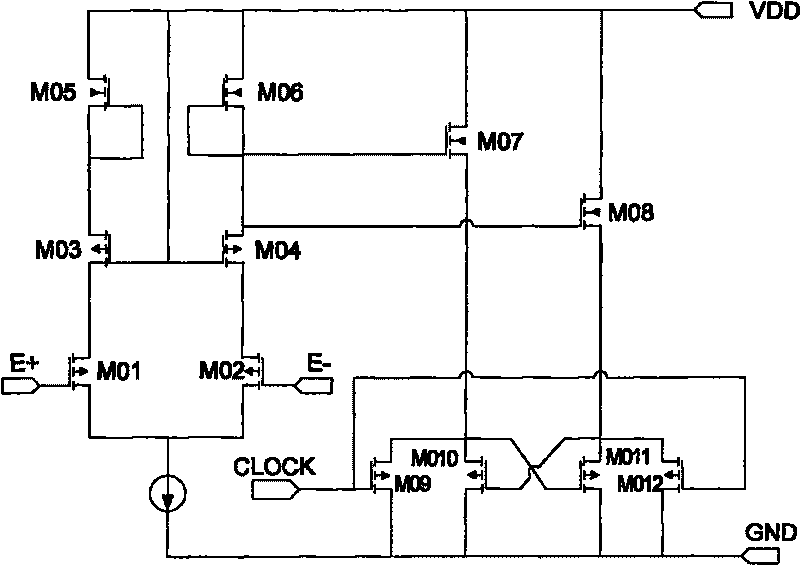

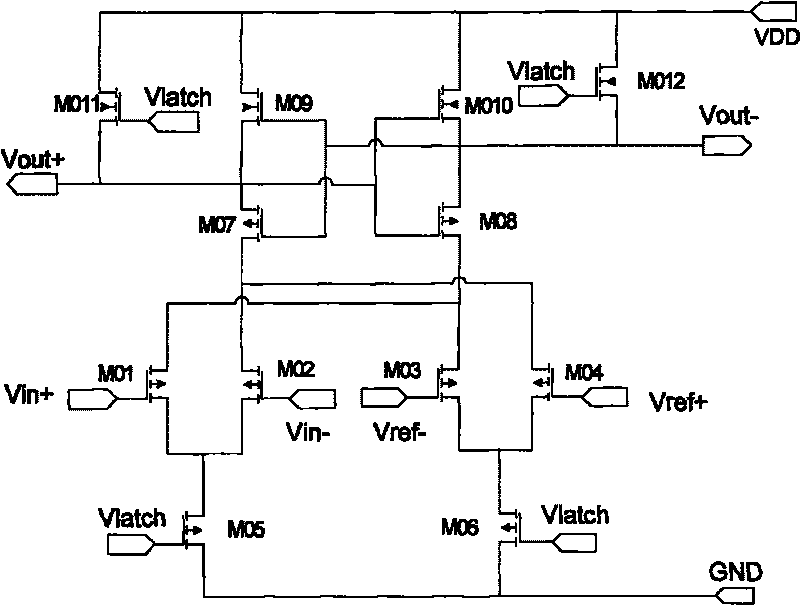

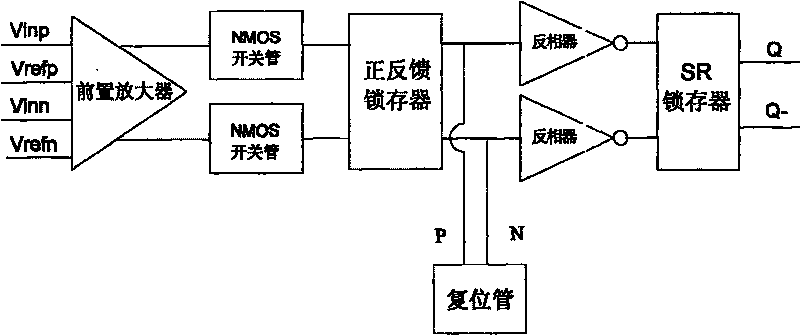

[0034] The principle block diagram of the CMOS low power consumption, low offset voltage, low backhaul noise comparator of the present invention is as image 3As shown, it includes a preamplifier, a pair of NMOS switches, a positive feedback latch, two CMOS inverters and an SR latch. The preamplifier uses PMOS double differential pair tubes as the input differential pair, a pair of diode-connected NMOS tubes and a pair of positive feedback connected NMOS tubes are connected in parallel as the active load circuit structure, and the input end of the PMOS double differential pair tubes Connect Vinp and Vinn terminals, Vrefp and Vrefn terminals respectively, connect a pair of NMOS switch tubes between the preamplifier and the positive feedback latch, connect a reset tube between the two output regeneration nodes P and N o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More