Low-power-consumption constant conduction time timing circuit design method and timing circuit

A technology with constant on-time and design methods, applied in computer-aided design, high-efficiency power electronic conversion, multiple input and output pulse circuits, etc., can solve the problems of large static power consumption of EA, difficult filtering, low light load efficiency, etc. , to achieve the effect of eliminating static power consumption, simple circuit structure and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0026] Any feature disclosed in this specification (including the abstract and drawings), unless specifically stated, can be replaced by other equivalent or similar purpose alternative features. That is, unless expressly stated otherwise, each feature is one example only of a series of equivalent or similar features.

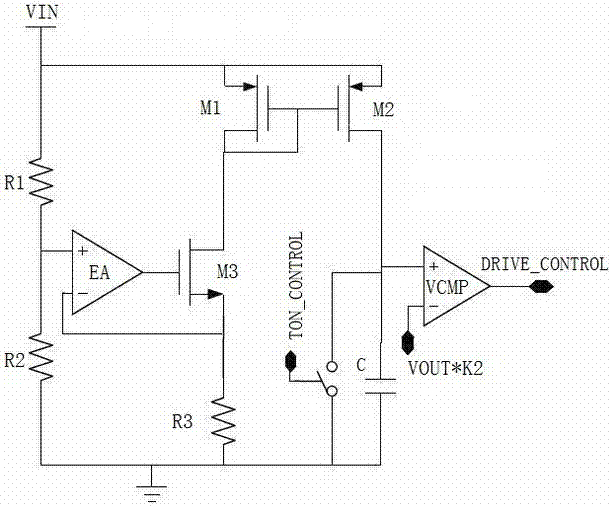

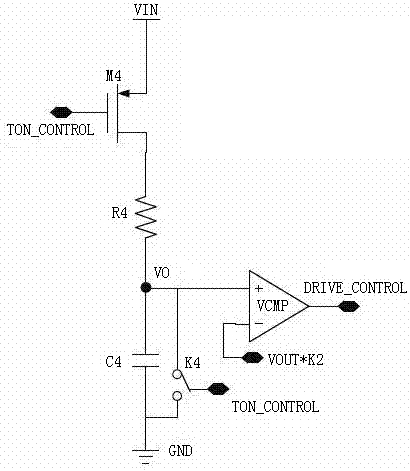

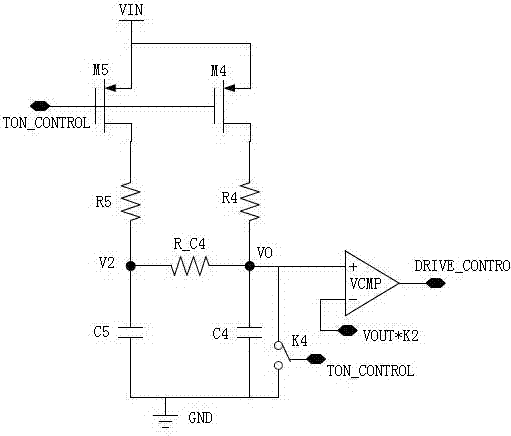

[0027] For the low power consumption constant on-time timing circuit design method, the specific method of the core idea of the present invention is: use RC circuit for timing, and eliminate the static power consumption of the timer. The low-power timer uses an RC circuit for timi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More