Manufacturing method of metal wafer level etching surface acoustic filter chip packaging structure

A filter chip and packaging structure technology, applied in waveguide-type devices, circuits, electrical components, etc., can solve the problems of long process, high cost, large structure size, etc., and achieve the effect of simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

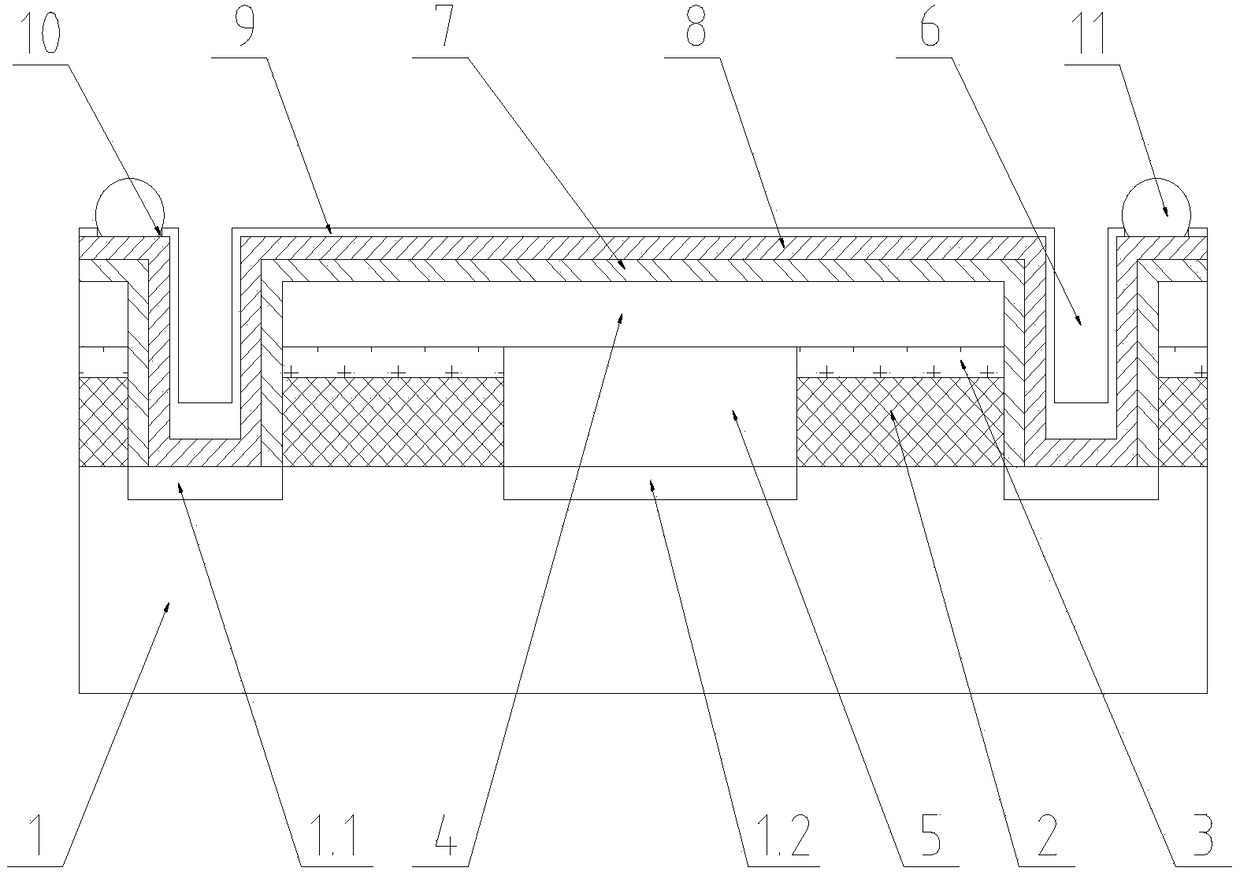

[0065] A method for manufacturing a metal wafer-level etching type surface acoustic filter chip packaging structure, which includes the following process steps:

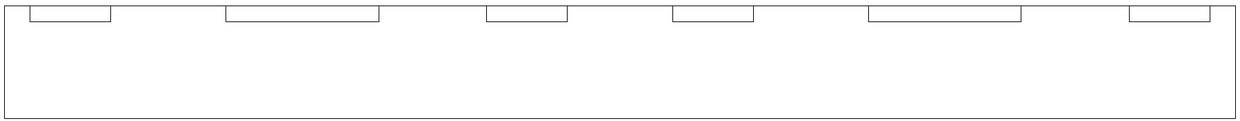

[0066] Step 1, see figure 2 , take a surface acoustic filter chip wafer;

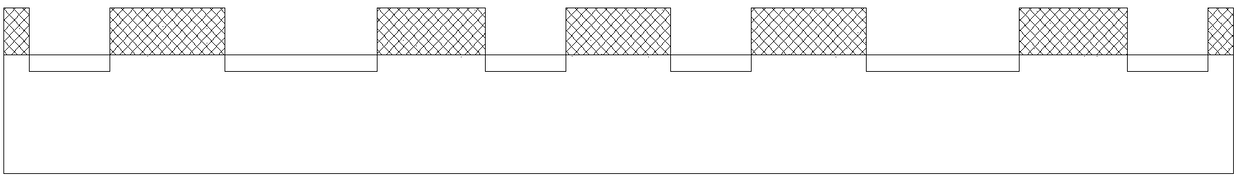

[0067] Step 2. Prepare the first insulating layer

[0068] see image 3 , apply a certain thickness of insulating glue on the surface acoustic filter chip wafer with the glue coating process, such as PI (polyimide), PA (nylon, polyamide), and use photolithography and development to seal the electrode area and Removal of the insulating glue at the sensing area of the chip;

[0069] Step 3. Full etching and bonding of wafers and bonding

[0070] see Figure 4 , take a bonded wafer, first perform full etching on the position above the subsequent electrode area of the bonded wafer, and then bond the bonded wafer that has been fully etched on the first insulating layer through an adhesive, so that the A cavity is formed above the sensing...

Embodiment 2

[0084] A method for manufacturing a metal wafer-level etching type surface acoustic filter chip packaging structure, which includes the following process steps:

[0085] Step 1, see Figure 10 , take a surface acoustic filter chip wafer;

[0086] Step 2. Prepare the first insulating layer

[0087] see Figure 11 1. Apply a certain thickness of insulating glue on the surface acoustic filter chip wafer by glue coating process, such as PI (polyimide), PA (nylon, polyamide), and use photolithography and development to seal the electrode area and Removal of the insulating glue at the sensing area of the chip;

[0088] Step 3: Half-etch and bond the wafers and bond them

[0089] see Figure 12 , take a bonded wafer, first half-etch the position above the subsequent electrode area of the bonded wafer, and then bond the bonded wafer that has been half-etched to the first insulating layer through an adhesive, so that the A cavity is formed above the sensing area of the chip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More