High efficiency video coding adder tree parallel implementation method

A high-efficiency video coding and implementation method technology, applied in the field of integer pixel motion estimation and high-efficiency video coding, can solve the problems of hardware area increase, etc., and achieve the effect of accelerating calculation speed, improving calculation efficiency, and improving operation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

[0049] The following embodiments provide a new and efficient method for implementing an addition tree based on a two-dimensional array processor,

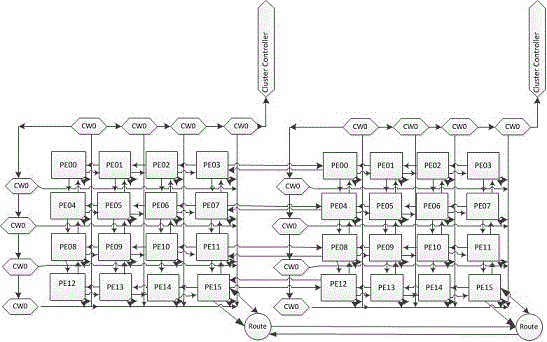

[0050] figure 1 is a schematic diagram of PE adjacency interconnection, and the addition tree is realized on the two-dimensional adjacency interconnection PE array;

[0051] figure 2 It is a schematic diagram of the addition tree array and buffer area distribution. The gray part is the buffer area module (the leftmost column is buffer area 1, the rightmost column is buffer area 2, and the bottom row is buffer area 3), and the middle 16×16 PEs are addition tree module. A total of 18×17 PEs are used;

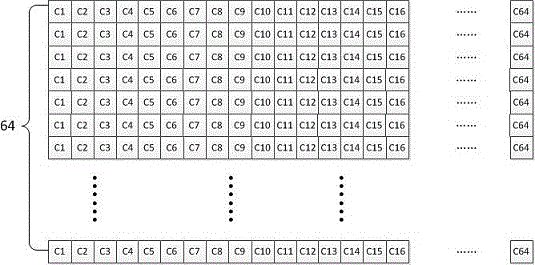

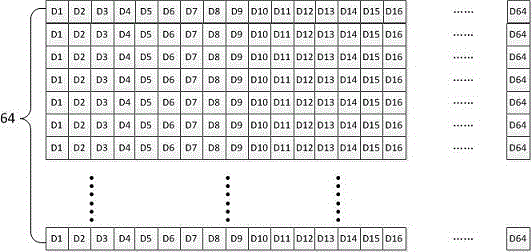

[0052] Step 1: Read the 64×64 brightness block into the additive tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More