Power chip testing device and method

A power chip and test device technology, applied in the field of power chip test devices, can solve problems such as low test efficiency, achieve the effects of simplifying workload, improving test efficiency, and solving complex and time-consuming manual operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] Reference will now be made in detail to the exemplary embodiments, examples of which are illustrated in the accompanying drawings. When the following description refers to the accompanying drawings, the same numerals in different drawings refer to the same or similar elements unless otherwise indicated. The implementations described in the following exemplary examples do not represent all implementations consistent with the present invention. Rather, they are merely examples of apparatuses and methods consistent with aspects of the invention as recited in the appended claims.

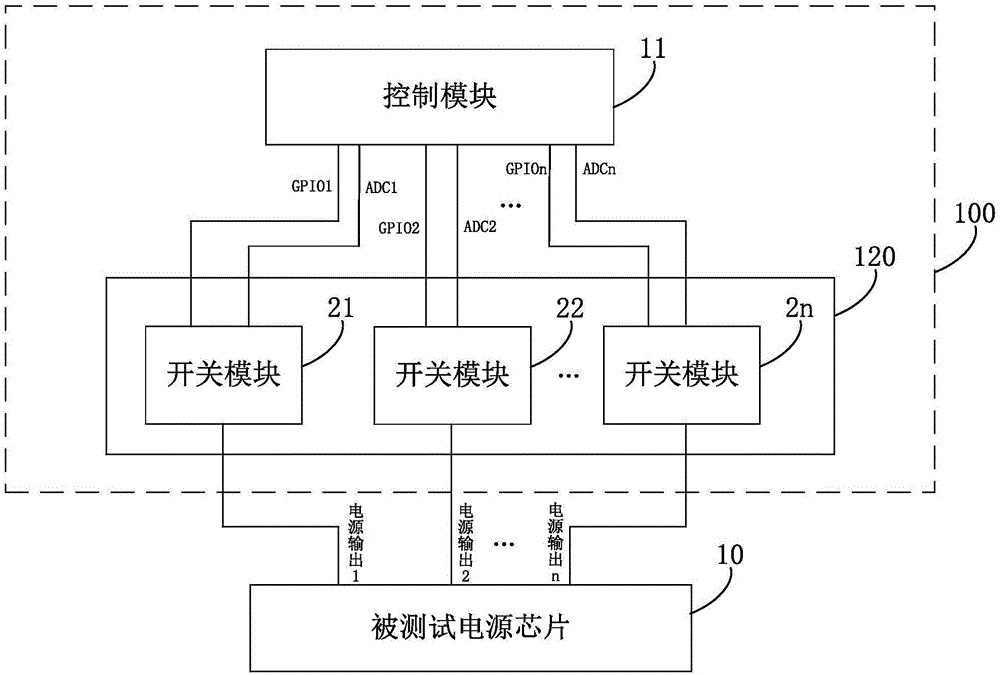

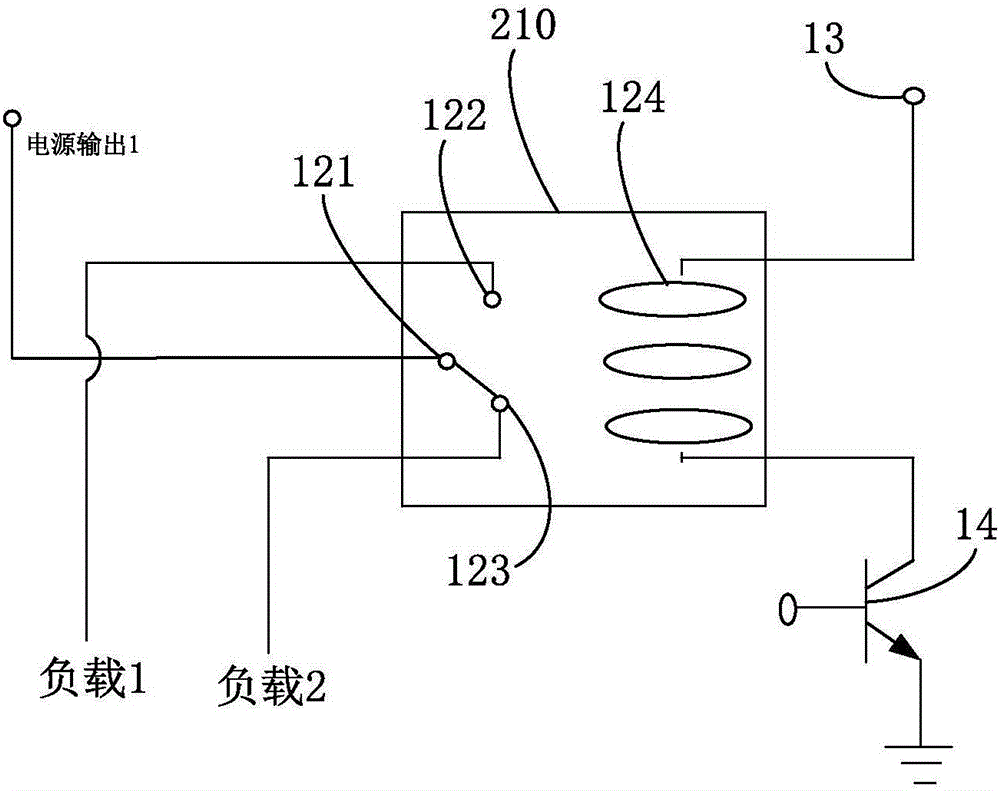

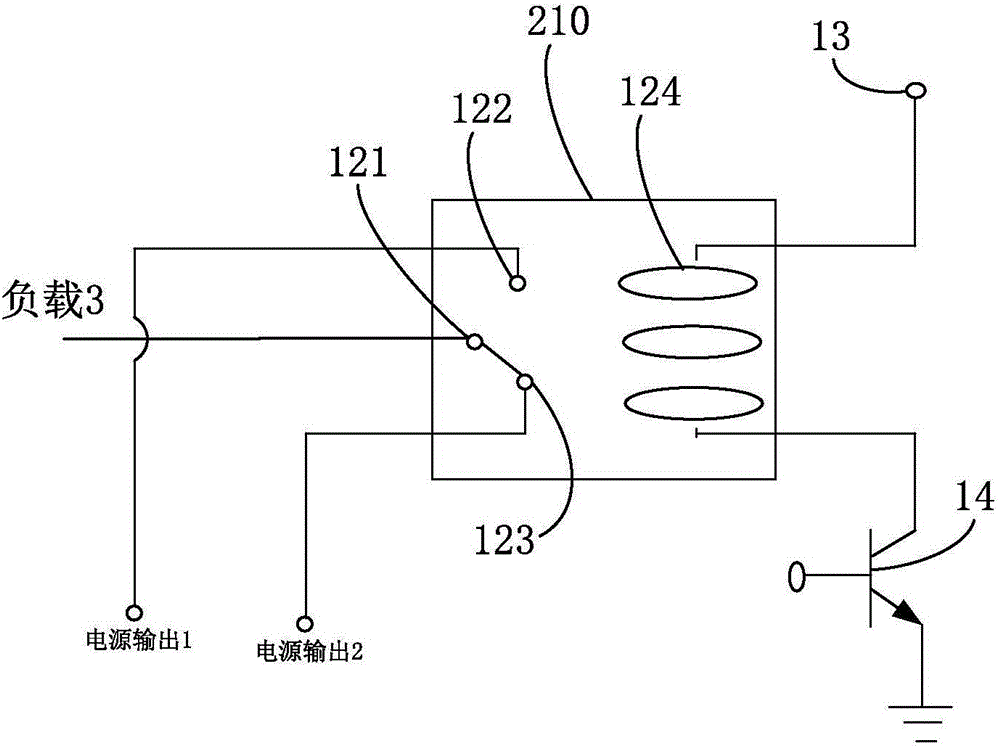

[0043] Figure 1A is a schematic structural diagram of a testing device for a power chip according to an exemplary embodiment, Figure 1B is one of the schematic diagrams showing the connection relationship between the switch and the load according to an exemplary embodiment, Figure 1C is the second schematic diagram of the connection relationship between the switch and the load shown accordin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com