ESD protection circuit

An ESD protection and circuit technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of small circuit area, high ESD trigger voltage, avoid device breakdown, reduce NMOS and PMOS area, and enhance ESD performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

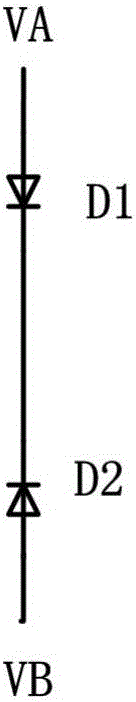

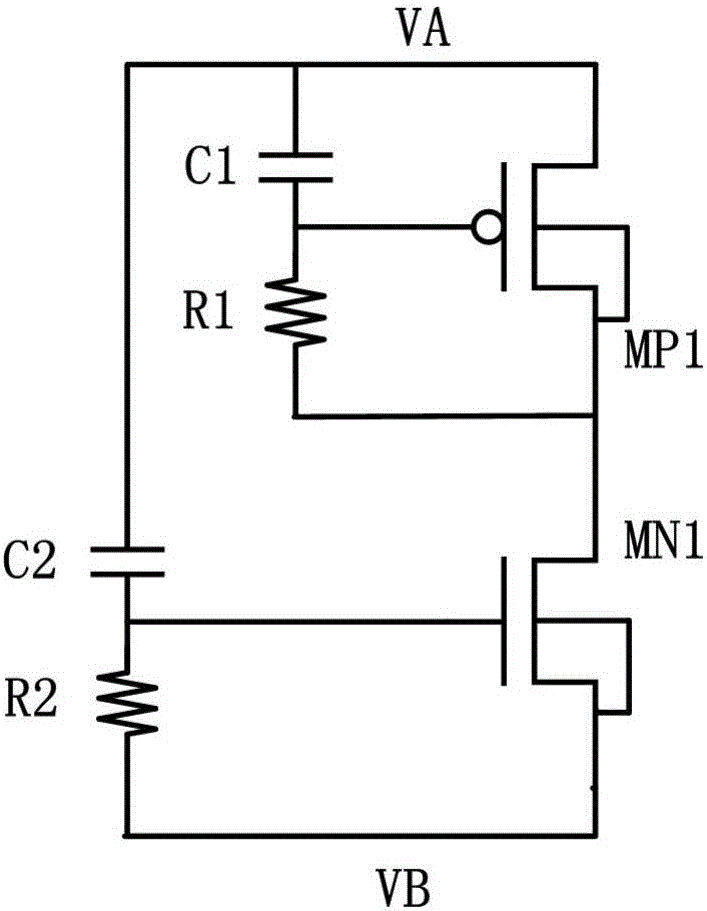

[0018] Such as figure 2 As shown, the ESD protection circuit realized by the present invention includes: a resistor R, a capacitor C, a large-size NMOS, and a large-size PMOS. Resistor R and capacitor C form a detection circuit capable of detecting ESD events. Large-size NMOS or large-size PMOS, in the ESD event, is in the conduction state, avoiding device breakdown, the trigger voltage is very low, and the static electricity is released in time and effectively, which greatly enhances the ESD performance of the circuit; compared with conventional methods, To achieve the same ESD level, the requi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com