IO circuit used for enhancing ESD performance

An ESD protection and circuit technology, applied in the direction of logic circuit coupling/interface, circuit, logic circuit connection/interface layout using field effect transistors, etc., can solve the problem of large area occupied by ESD protection devices, limited ESD level, and increased circuit area and other problems, to achieve the effect of improving ESD level, avoiding device breakdown, and reducing circuit area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

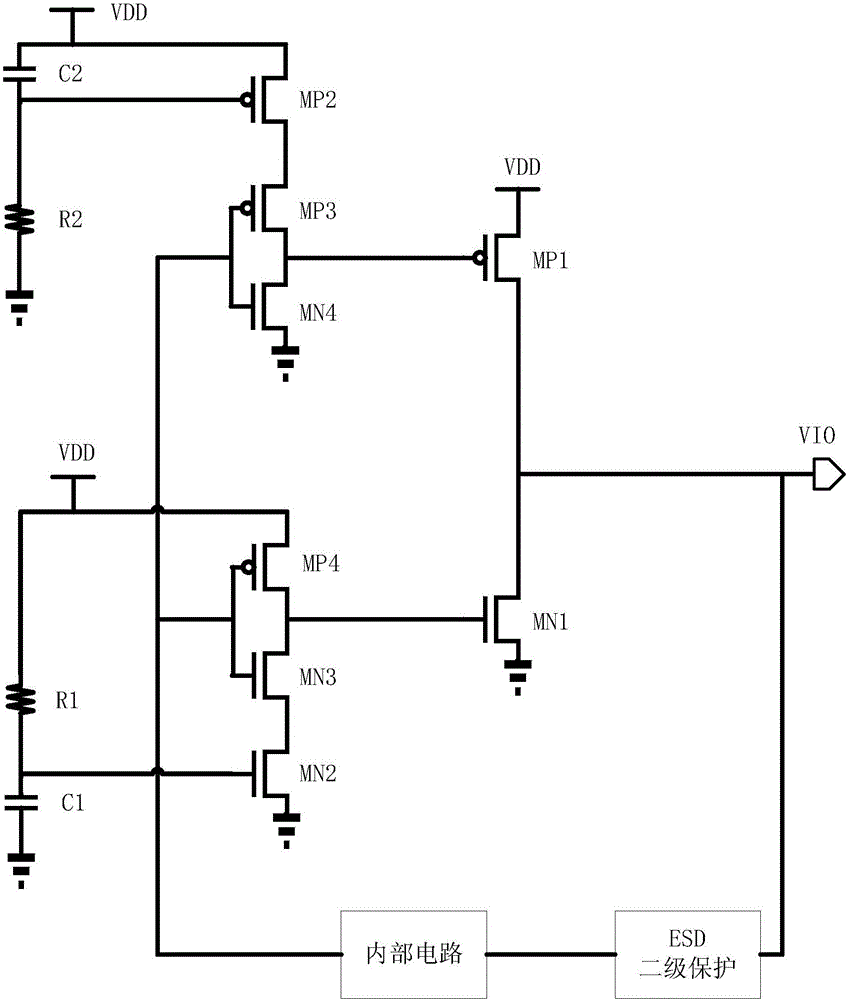

[0018] Please refer to figure 1 As shown, the IO circuit realized by the present invention is as figure 1 As shown, the IO circuit includes: resistor R, capacitor C, pre-stage drive circuit, large-size NMOS, and large-size PMOS. If necessary, an ESD secondary protection circuit can be added, and the ESD secondary protection circuit is set between the internal circuit and the external pin VIO for output.

[0019] The internal circuit in the figure is the internal circuit of the existing IO circuit, and will not be described again.

[0020] Wherein, the resistor R and the capacitor C constitute a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More