Memory cell device and manufacturing method thereof

A technology for memory cells and devices, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve problems such as leakage, large voltage difference, and easy generation of drain interference.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

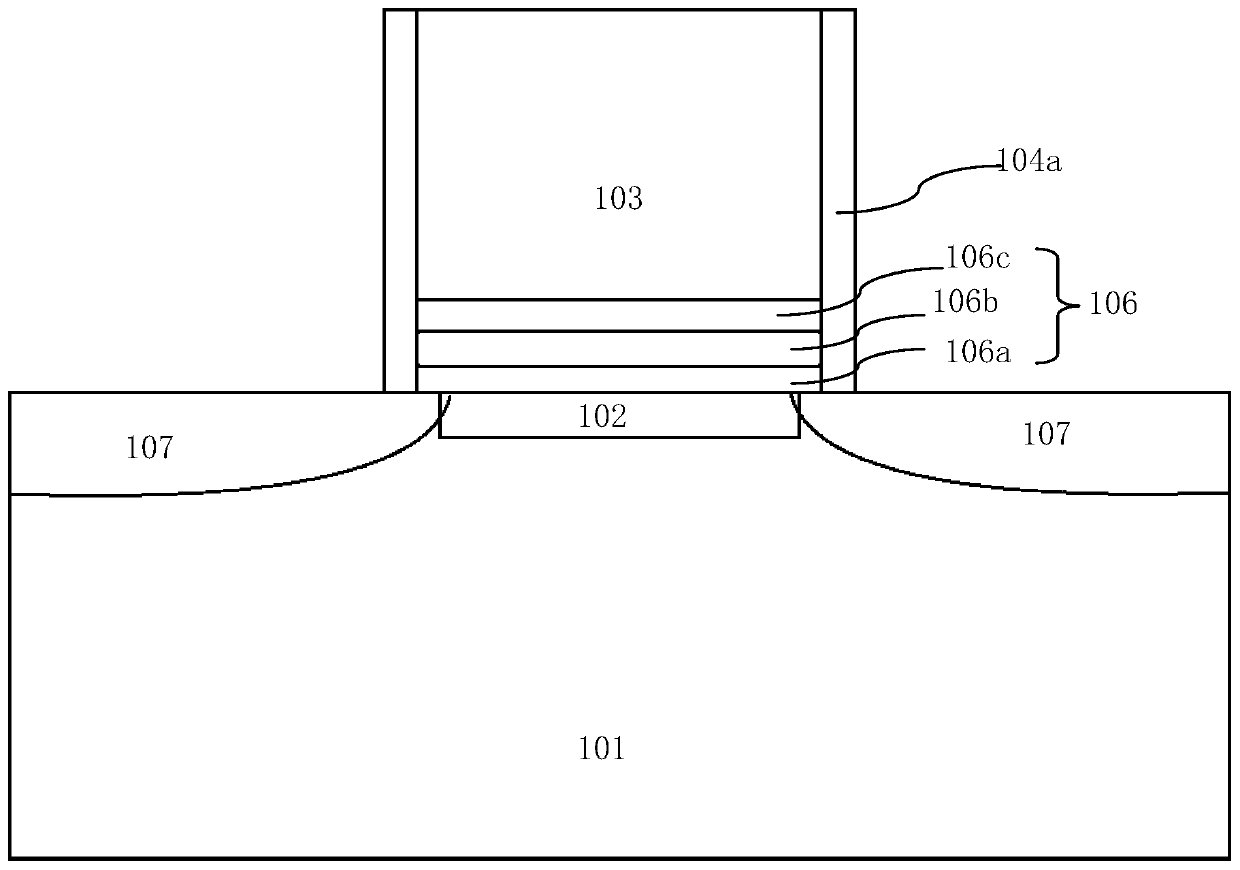

[0066] The polysilicon gate of the existing memory cell device overlaps with the source and drain regions on both sides, such as Figure 2A to Figure 2D Shown is a schematic structural view of each step in the manufacturing method of the existing memory unit device; the manufacturing method of the existing memory unit device includes the following steps:

[0067] Step 1. Firstly, conventional well implantation is performed to form a well region on the surface of a semiconductor substrate such as a silicon substrate 101 . Such as Figure 2A As shown, a channel implant (Channel Implant) or a depletion implant (Depletion Implant) is then performed to form a channel region 102 on the surface of the semiconductor substrate.

[0068] Step two, such as Figure 2B As shown, a gate structure formed by overlapping the gate ONO layer 106 and the polysilicon gate 103 is sequentially formed on the surface of the semiconductor substrate 101 . The gate structure needs to be formed by depo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More