SEU fault tolerance technology applied to FPGA

A fault-tolerant technology and a fault-based technology, applied in the direction of error detection/correction, instrumentation, electrical digital data processing, etc., can solve problems such as system failure, wrong data information, etc., to reduce hardware scale, improve reliability, and reduce the scope of reconstruction Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be described in detail below in conjunction with the accompanying drawings.

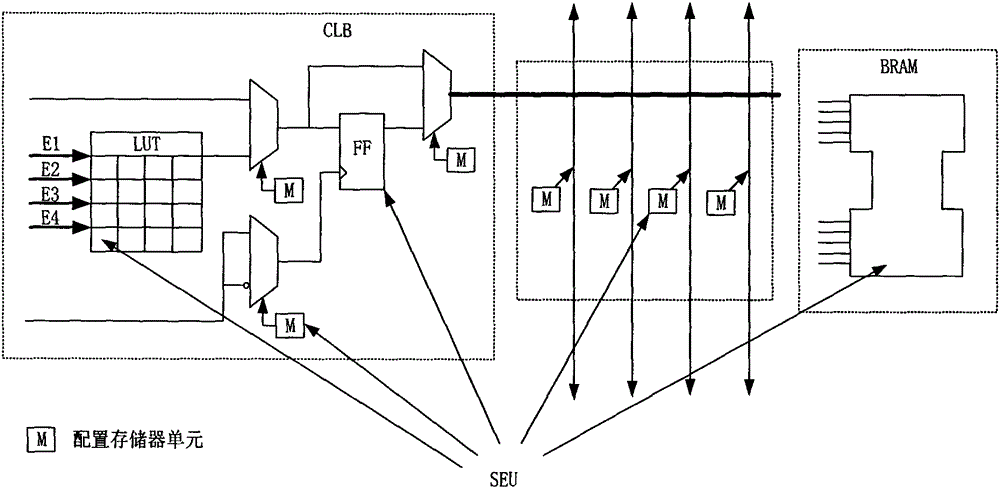

[0016] figure 1 Shown is the structure of the bottom layer of SRAM FPGA. The leftmost dashed box in the figure is the CLB programmable logic block. For Virtex-5 series FPGAs, each CLB consists of two Slices, and each Slice contains 4 LUTs and 4 flip-flops. According to the user's design, the CLB can be configured as the corresponding combinatorial logic or sequential logic, and it can also be configured as distributed RAM or distributed ROM for use. The LUT in the CLB is mainly used to realize the combinatorial logic, and the trigger is mainly used for It is used to realize the intermediate results of sequential logic and storage circuit operation. BRAM is an on-chip storage resource used to implement various storage functions and improve the overall operating efficiency of the FPGA. M is a configuration memory unit, which is used to store configuration data of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More