Least switching loss implementation method of three-level inverter

A three-level inverter, switching loss technology, applied in the field of power electronics, can solve problems such as unsatisfactory results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0104] For the convenience of description, the relevant technical terms appearing in the specific implementation are explained first:

[0105] PWM (Pulse Width Modulation): pulse width modulation;

[0106] IGBT (Insulated Gate Bipolar Transistor): insulated gate bipolar transistor;

[0107] figure 1 It is a block diagram of a method for realizing the minimum switching loss of a three-level inverter in the present invention.

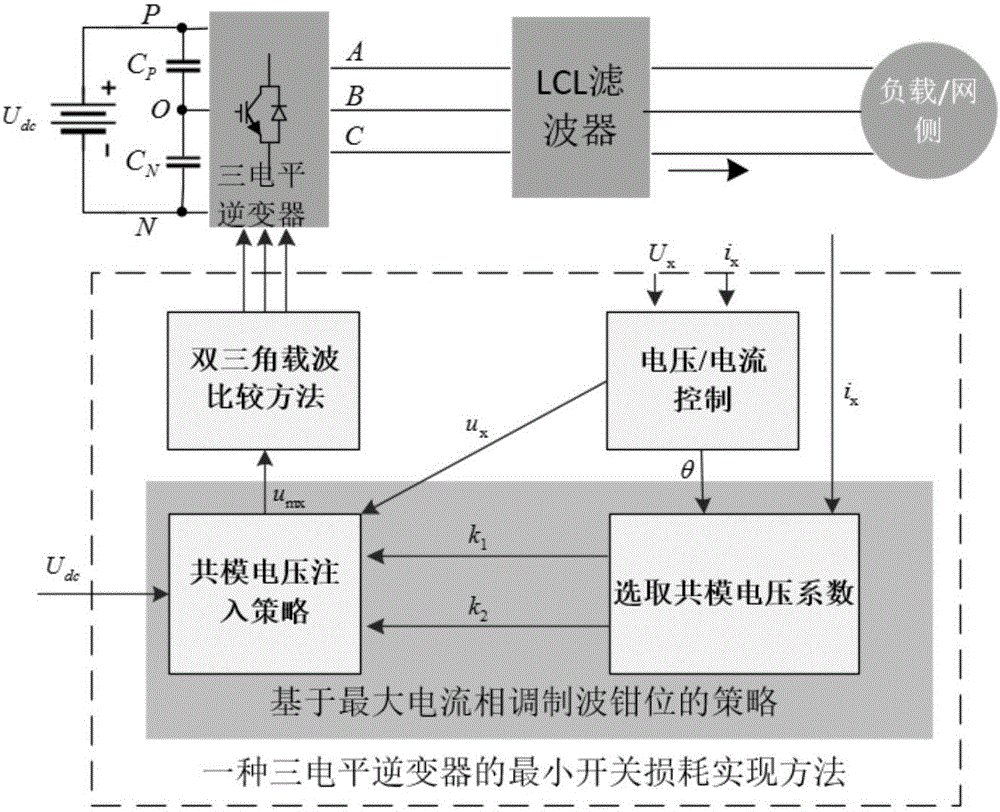

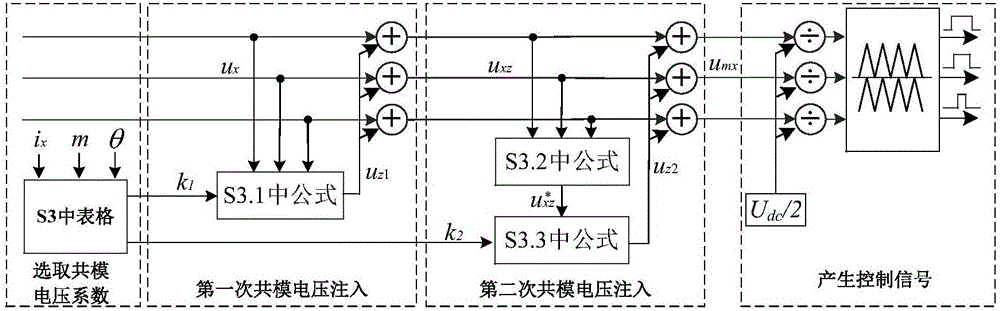

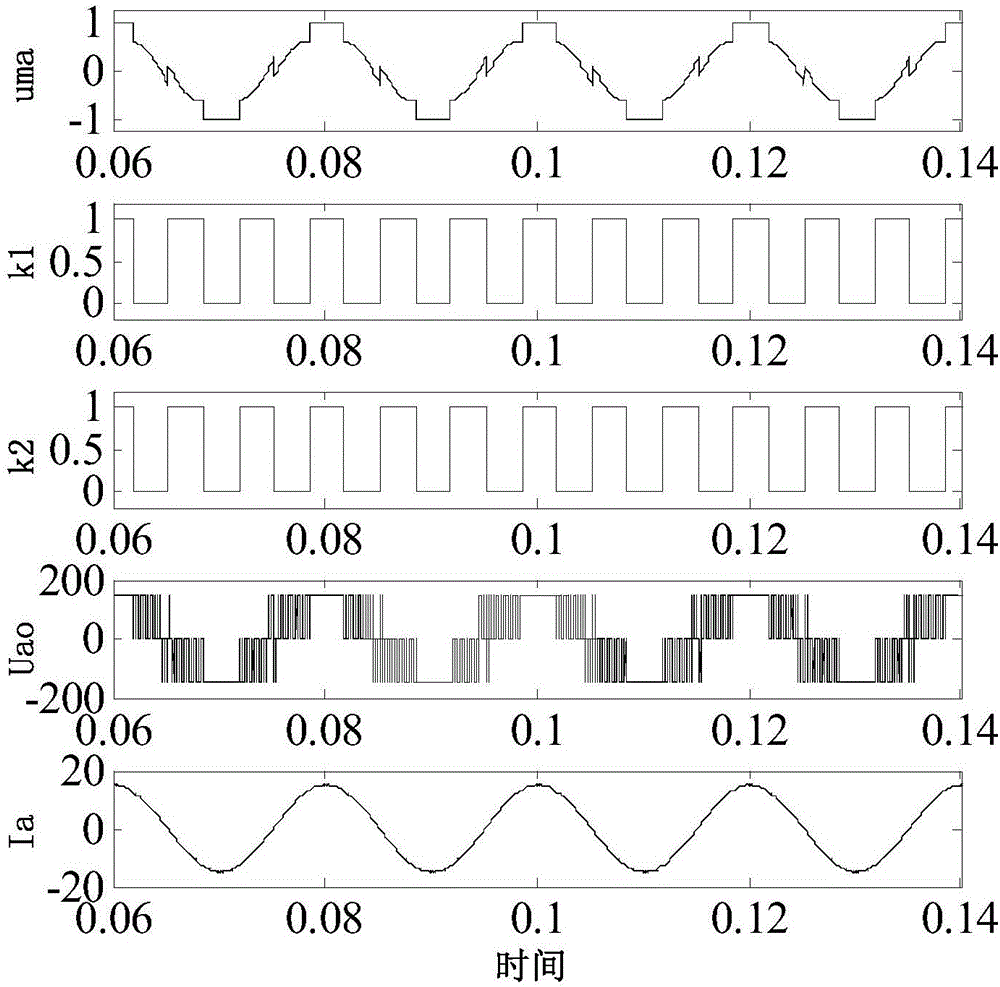

[0108] In this example, combined with figure 1 The block diagram of a minimum switching loss realization method of a three-level inverter is shown, and the three-level minimum switching loss method is described in detail, including the following steps:

[0109] S1. Obtain the AC side voltage U through the voltage and current sensor x (x=a,b,c), AC side current i x (x=a,b,c), total DC side voltage U dc real-time data.

[0110] S2, combined with AC side current i x , AC side voltage U x Get the three-phase voltage control signal u through voltage a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More