A Method to Accelerate the Incremental Layout Rationalization of Standard Cells

A standard cell and layout technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as time-consuming and design rule violations in complex systems, and achieve the effect of improving efficiency and shortening time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

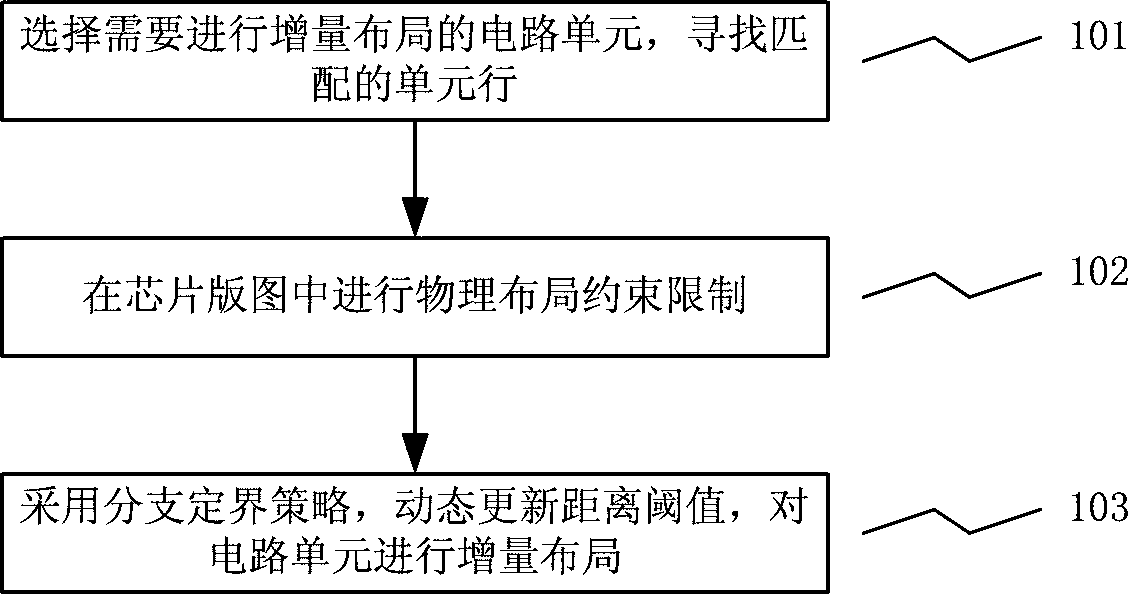

[0029] figure 1 For the method flow chart of accelerating standard cell incremental layout rationalization according to the present invention, reference will be made below figure 1 , to describe in detail the method for accelerating the rationalization of incremental layout of standard cells of the present invention.

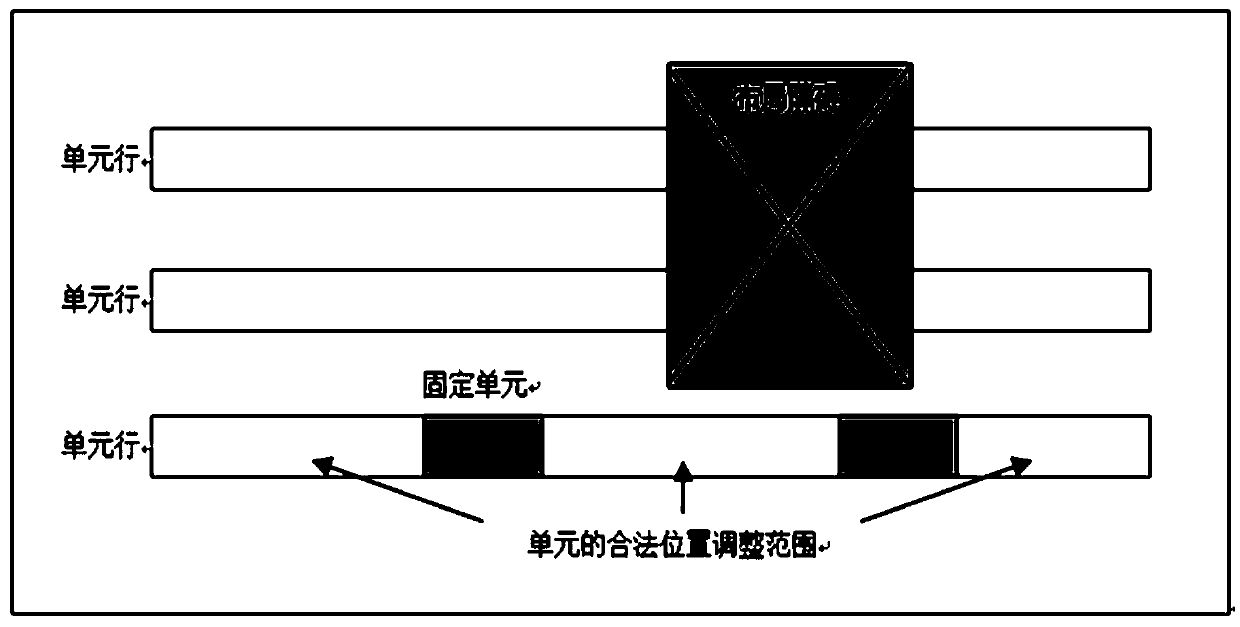

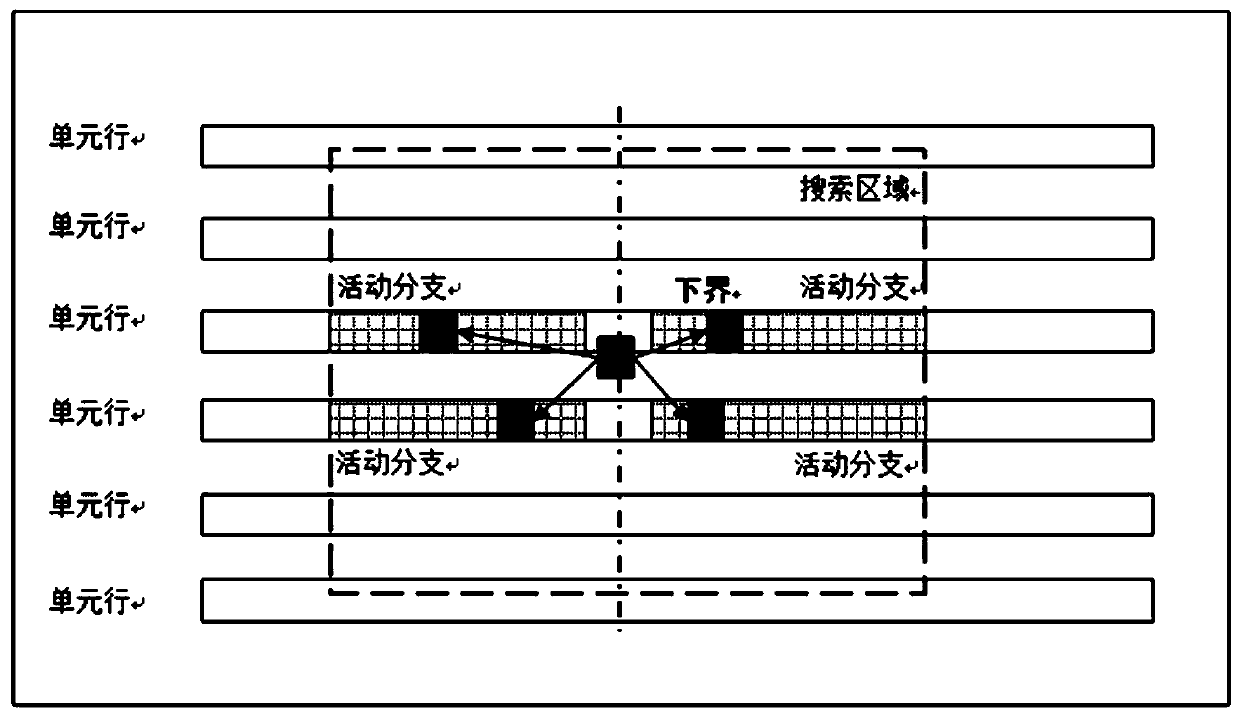

[0030] First, in step 101, read in the physical information of the chip layout, locate the position and size of the cell row placed in the chip; read in the physical position information of each unit contained in the circuit, and determine the legal position available in the cell row; Select a certain circuit unit that needs to be incrementally laid ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More