Array substrate gate driving circuit, driving method thereof, and display device

A technology for gate drive circuits and array substrates, applied in static indicators, digital memory information, instruments, etc., can solve problems that are not conducive to the design of narrow borders of display panels, and achieve the effects of simple timing control and low circuit cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

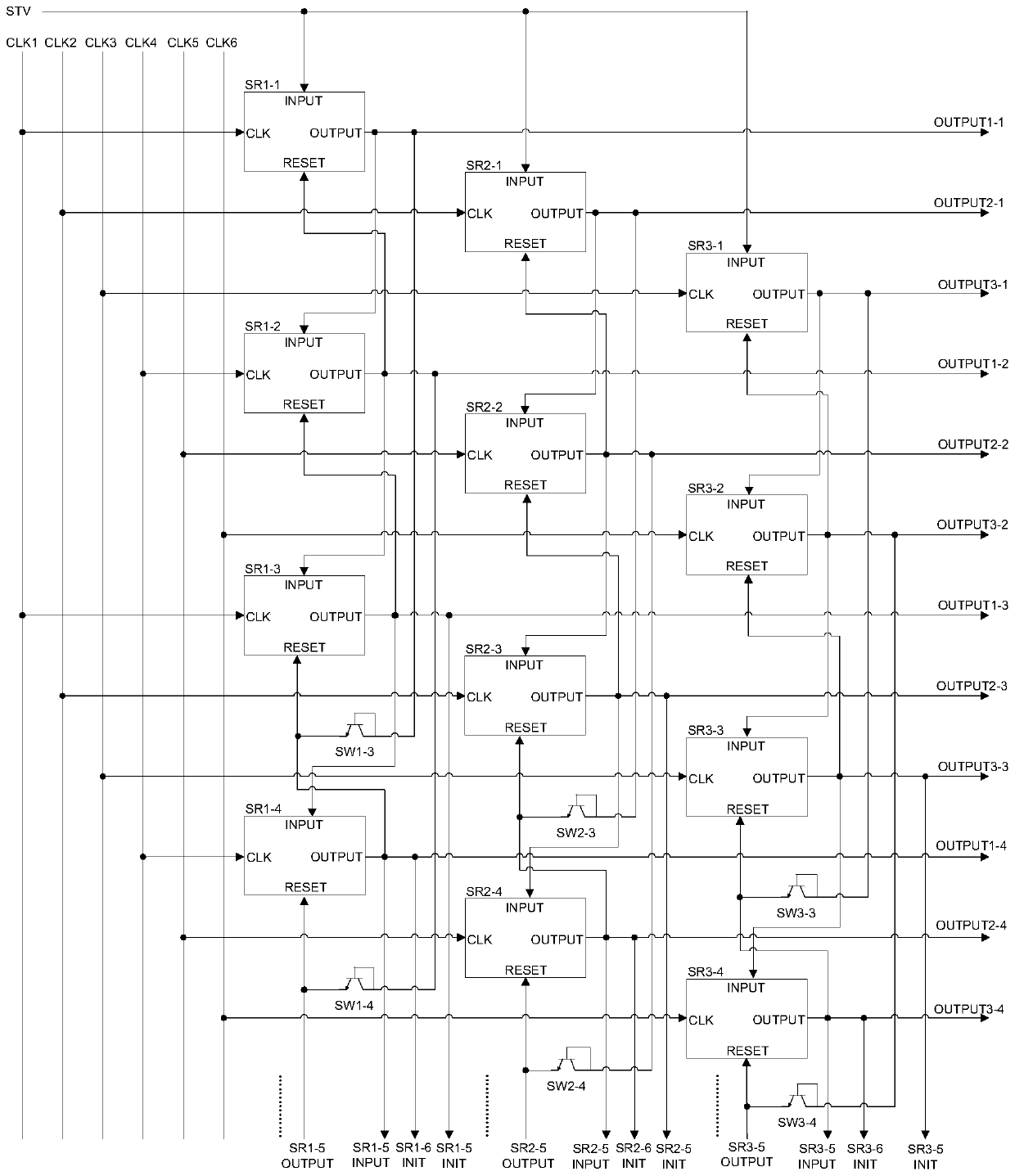

[0038] figure 1 The shown array substrate gate driving circuit includes at least one shift register group, and each shift register group includes a plurality of shift registers. In each shift register group, make the input end of the shift register located in the first stage receive the STV signal, and make the input ends of other stages of shift registers other than the first stage be connected to the one before the shift register. The output terminal of the shift register of the stage to receive the gate drive signal output from the shift register of the previous stage as the input signal, thereby cascading multiple shift registers in each shift register group together . For the convenience of expression, in this paper, "SRi-j" is used to represent the shift register cascaded at the jth level in the i-th shift register group, where the shift register SRi-j is located in the shift register SRi- The upper stage of (j+1), the shift register SRi-(j+1) is located in the lower s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More