Patents

Literature

33results about How to "Simple timing control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

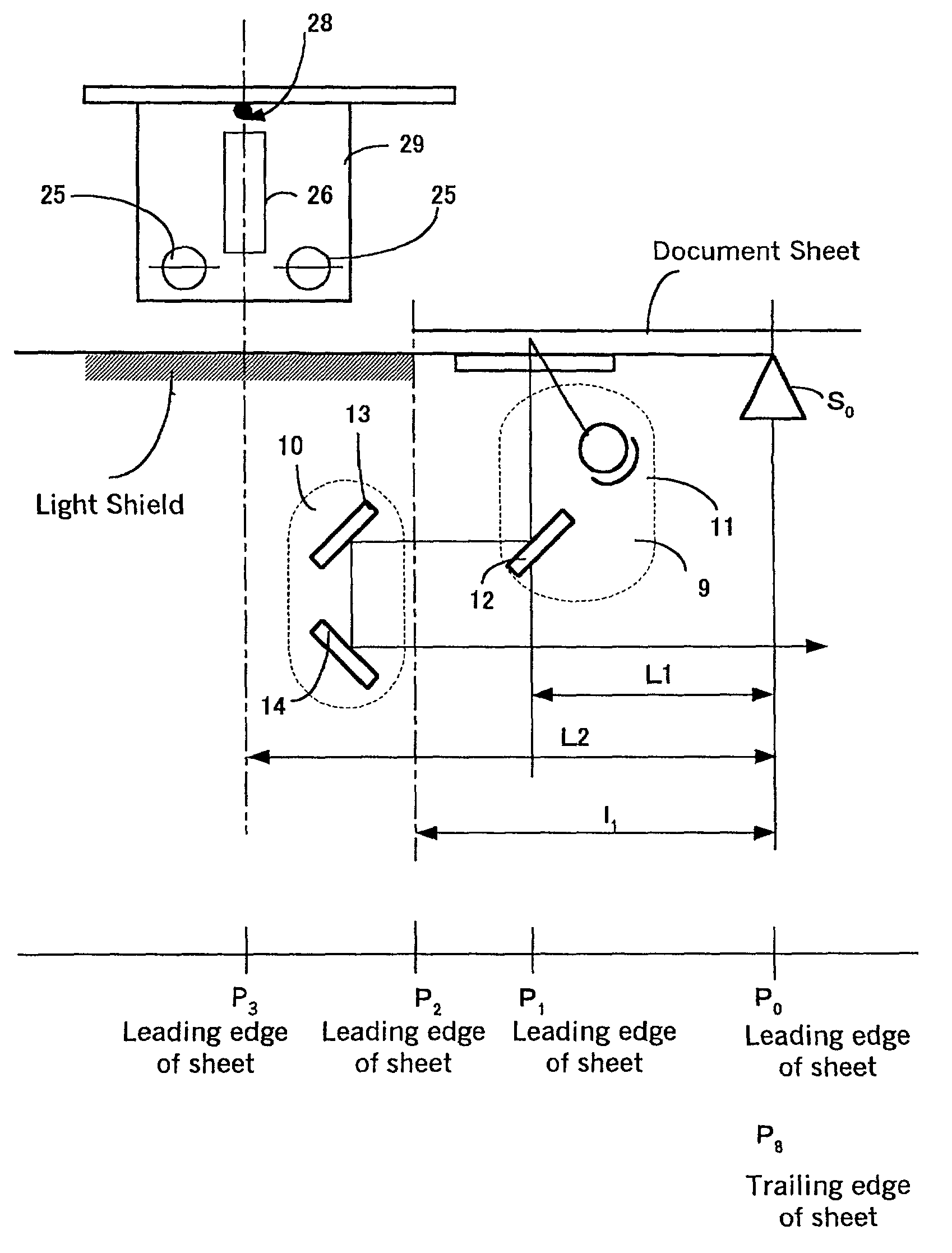

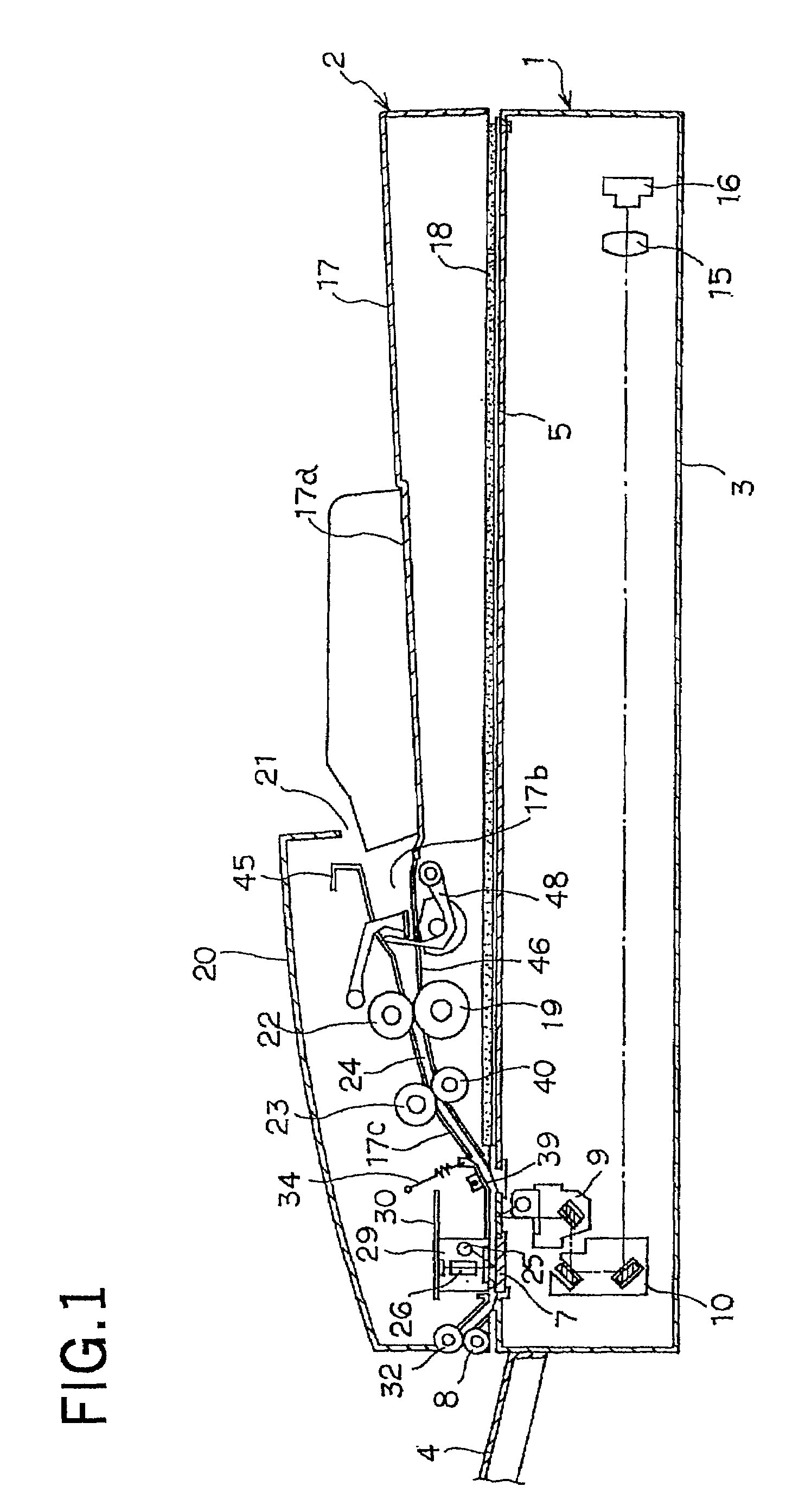

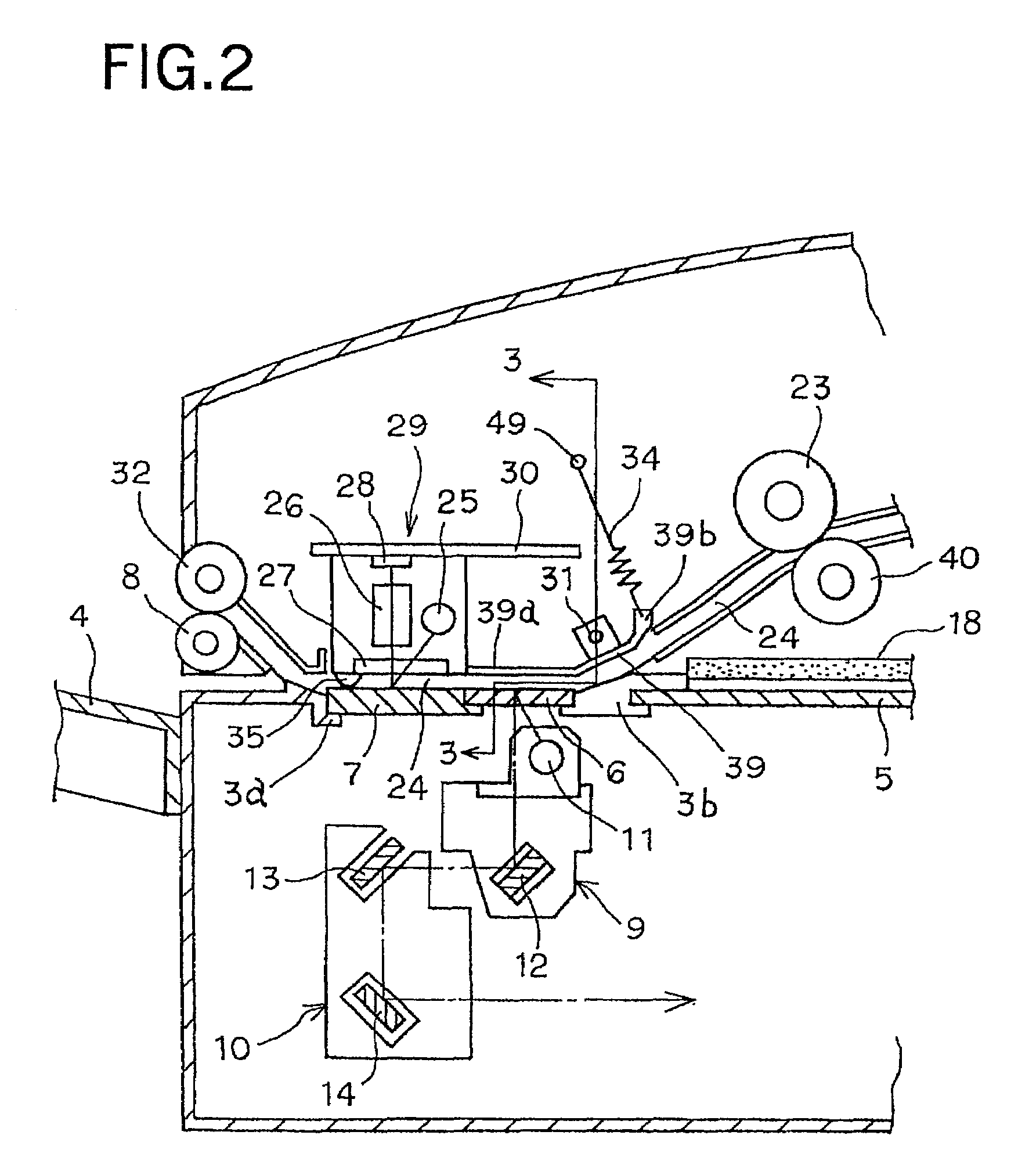

Image reading apparatus and image reading method

ActiveUS7027194B2Simple timing controlReduce noiseElectrographic process apparatusImage data processing detailsLeading edgeComputer science

An image reading apparatus for reading indicia on the front and back surfaces of a document using two image sensors includes a document detection sensor to detect the document, a first image sensor for reading an image on one surface of the document, a second image sensor for reading an image on the other surface of the document, and a controller. The controller starts to read the image data from the first and second image sensors when prescribed amounts of time have passed after the document detection sensor detects the leading edge of the document, and stops the reading of the image data from the image sensors. The structure provides a lightweight and compact apparatus while reducing image noise caused by the mutual interferences of the light sources in reading the image data.

Owner:NISCA KK

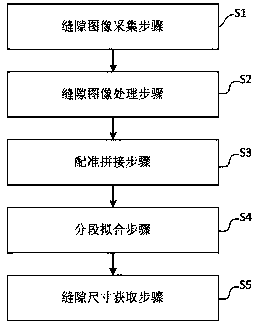

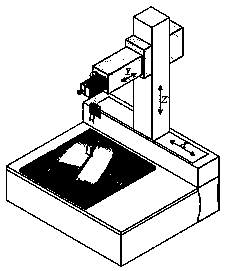

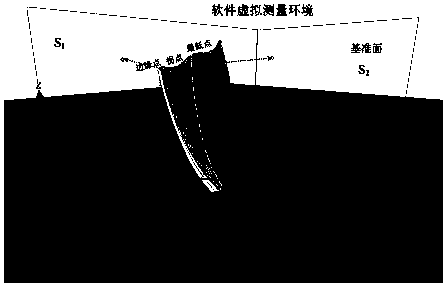

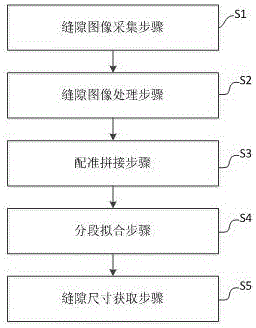

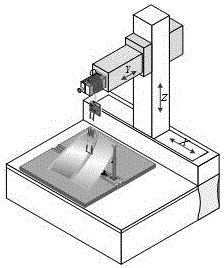

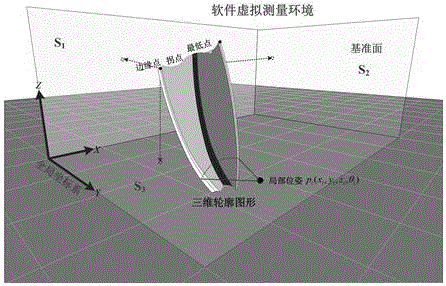

Geometric size measuring method and device for slit inside free-form surface

ActiveCN106705847AReduce demandEasy to operateImage analysisGeometric image transformationImage processingImage acquisition

The invention discloses a geometric size measuring method and a device for a slit inside free-form surface. The geometric size measuring method for the slit inside free-form surface comprises the steps of acquiring a slit image: conducting the segmented acquisition of the slit image of a to-be-measured free-form surface product; processing the slit image: processing each segment of the acquired slit image so as to obtain a slit cross-sectional profile, and positioning the edge feature points of each segment of the slit profile, the inflection point of the slit profile, the highest point of the slit profile and the lowest point of the slit profile; conducting the registering and splicing operation: registering and splicing all segments of the processed slit profile; conducting the segmented fitting operation: conducting the segmented fitting for the feature points of the slit profile after the registering and splicing operation so as to obtain an overall slit profile containing the lowest-point curve, the edge curve and the highest-point curve of a slit; and acquiring the geometric size of the slit: according to the fitted curve, acquiring the depth, the length and the width of the slit.

Owner:CHONGQING ACAD OF METROLOGY & QUALITY INST

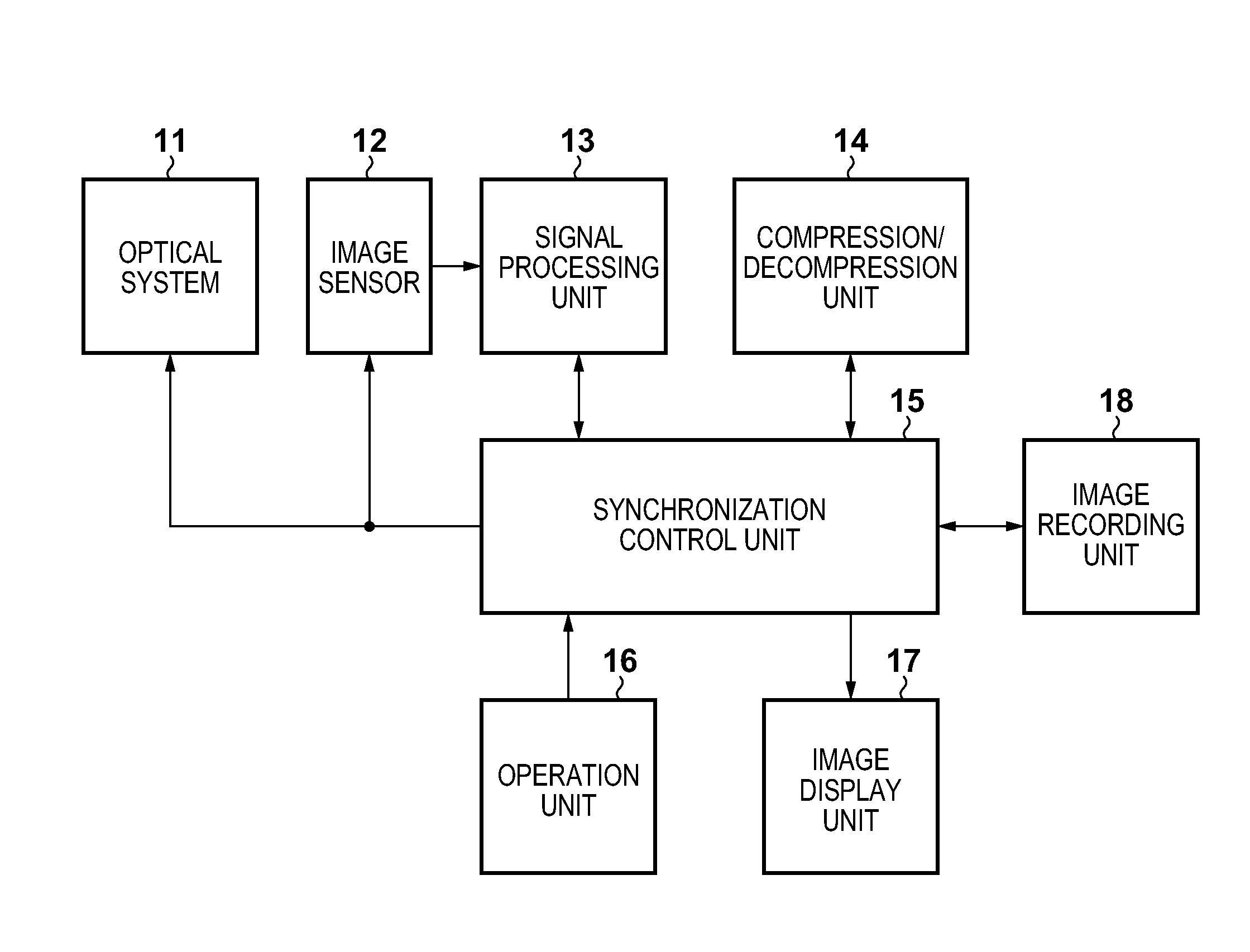

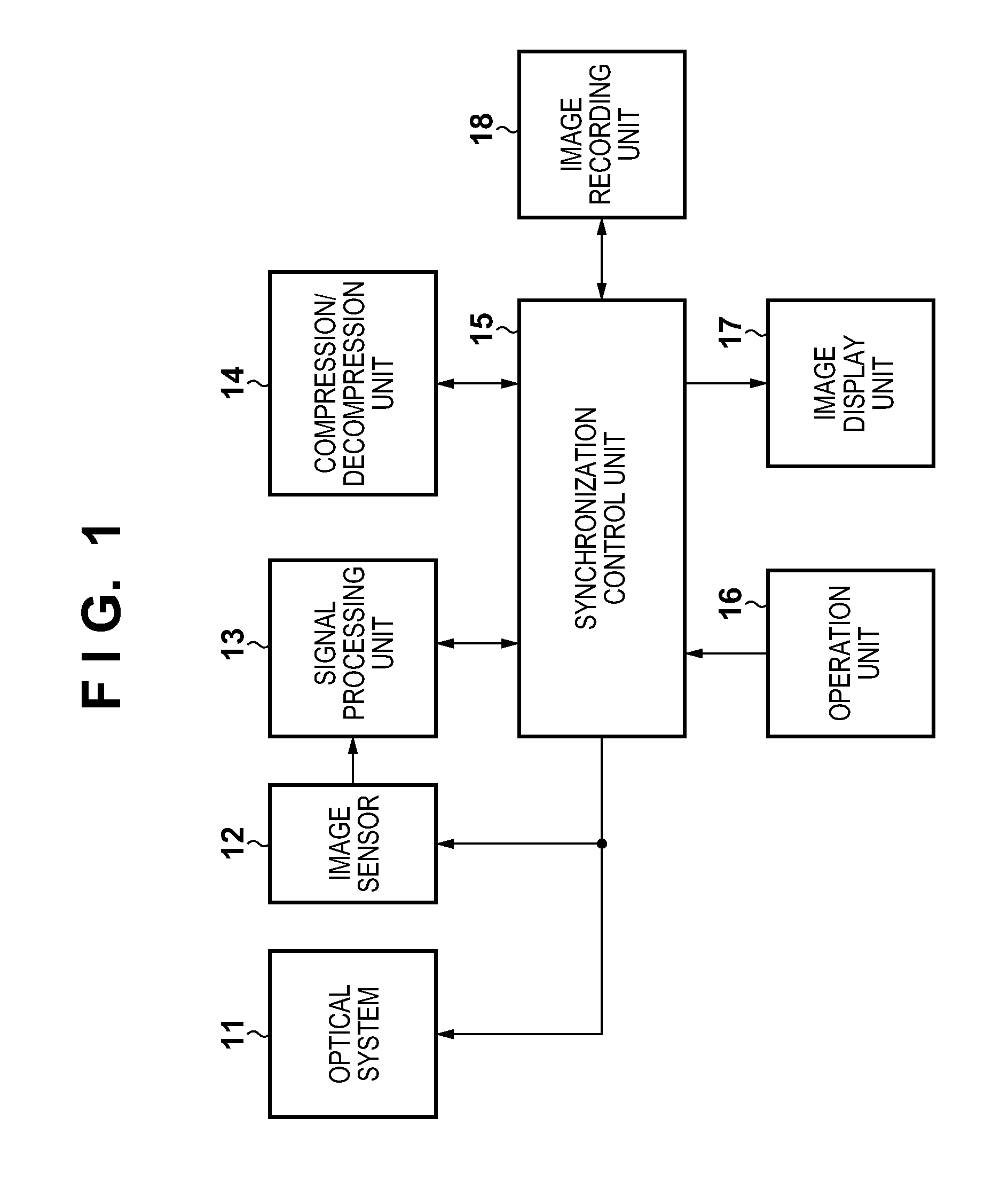

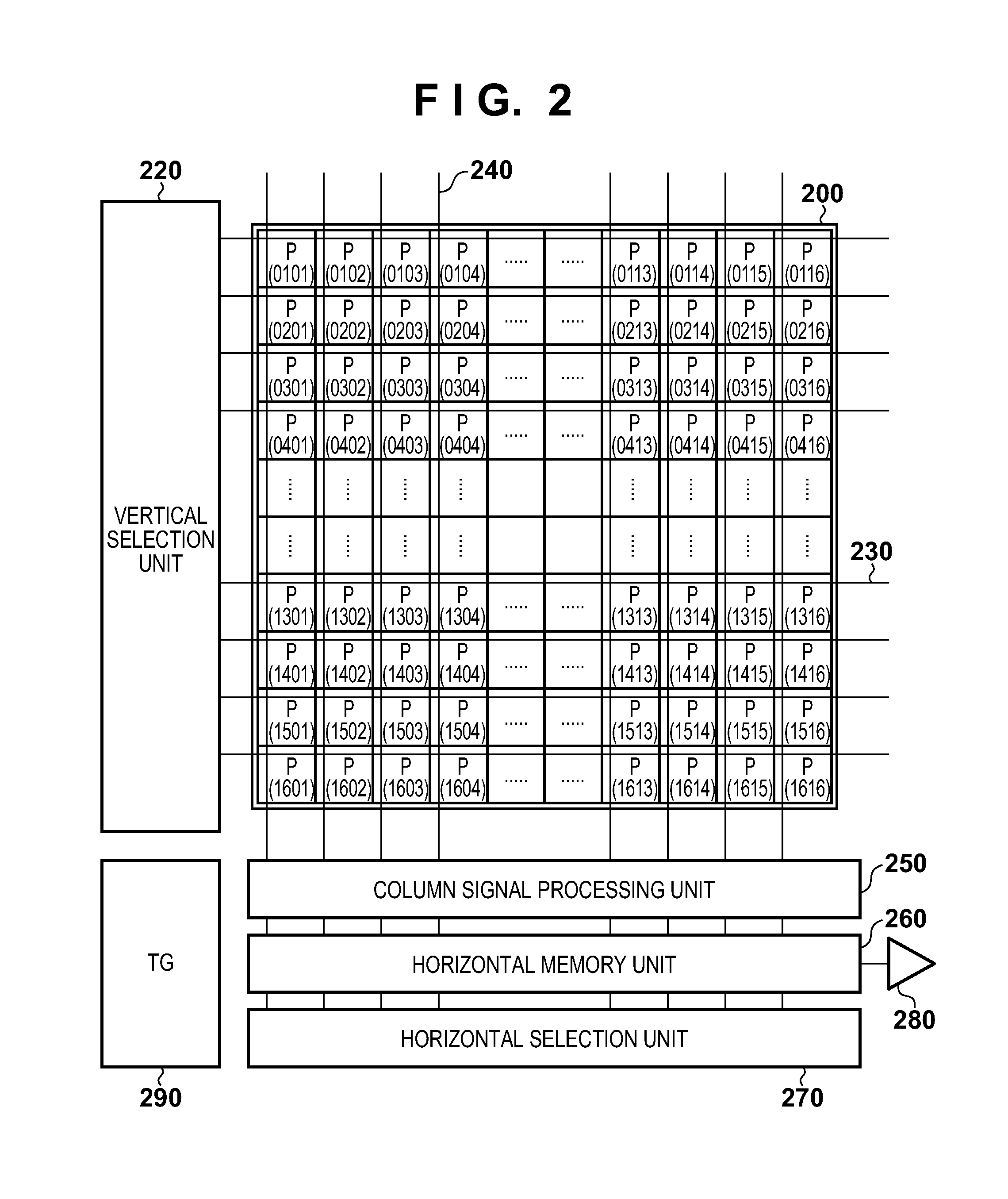

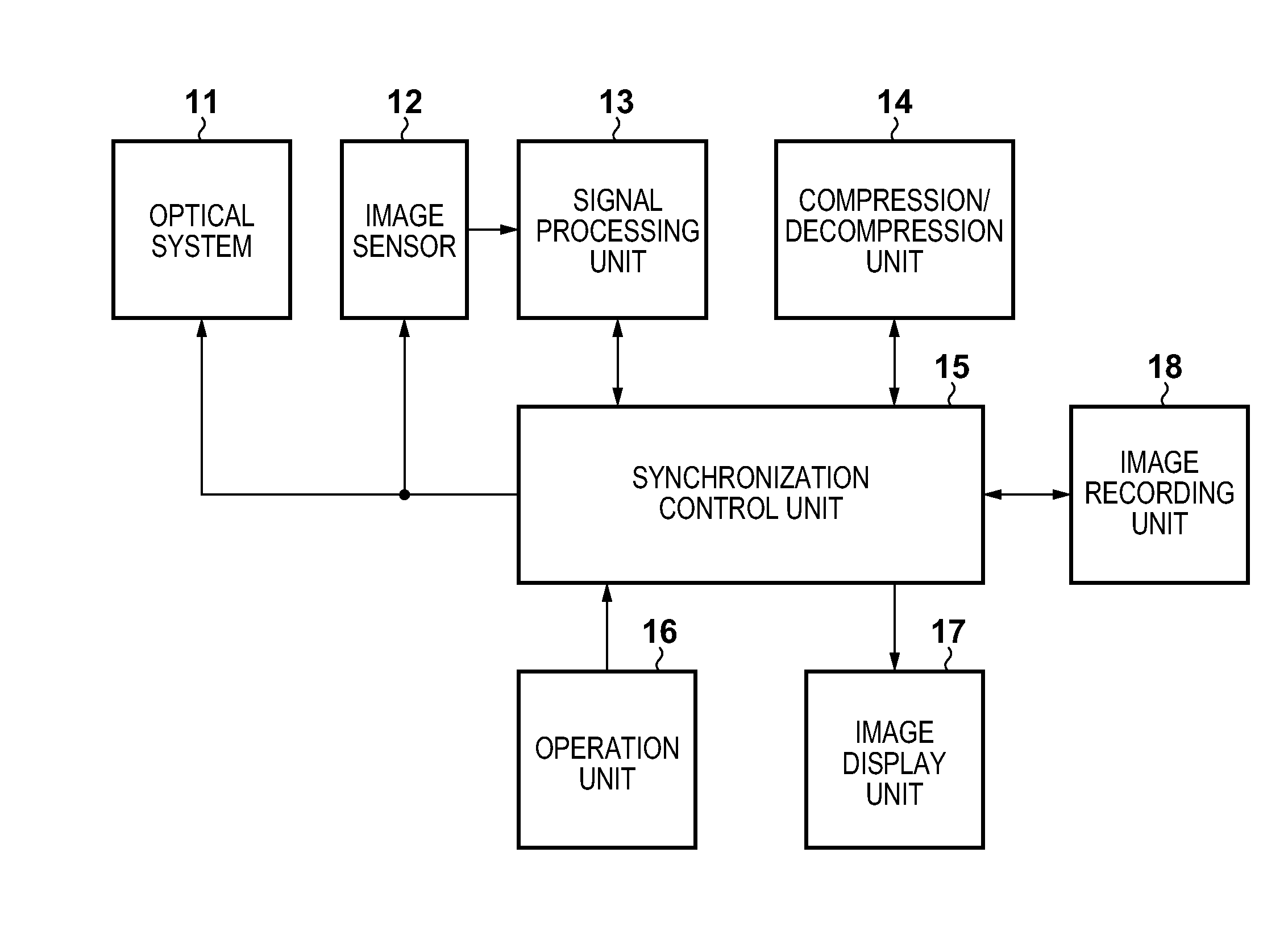

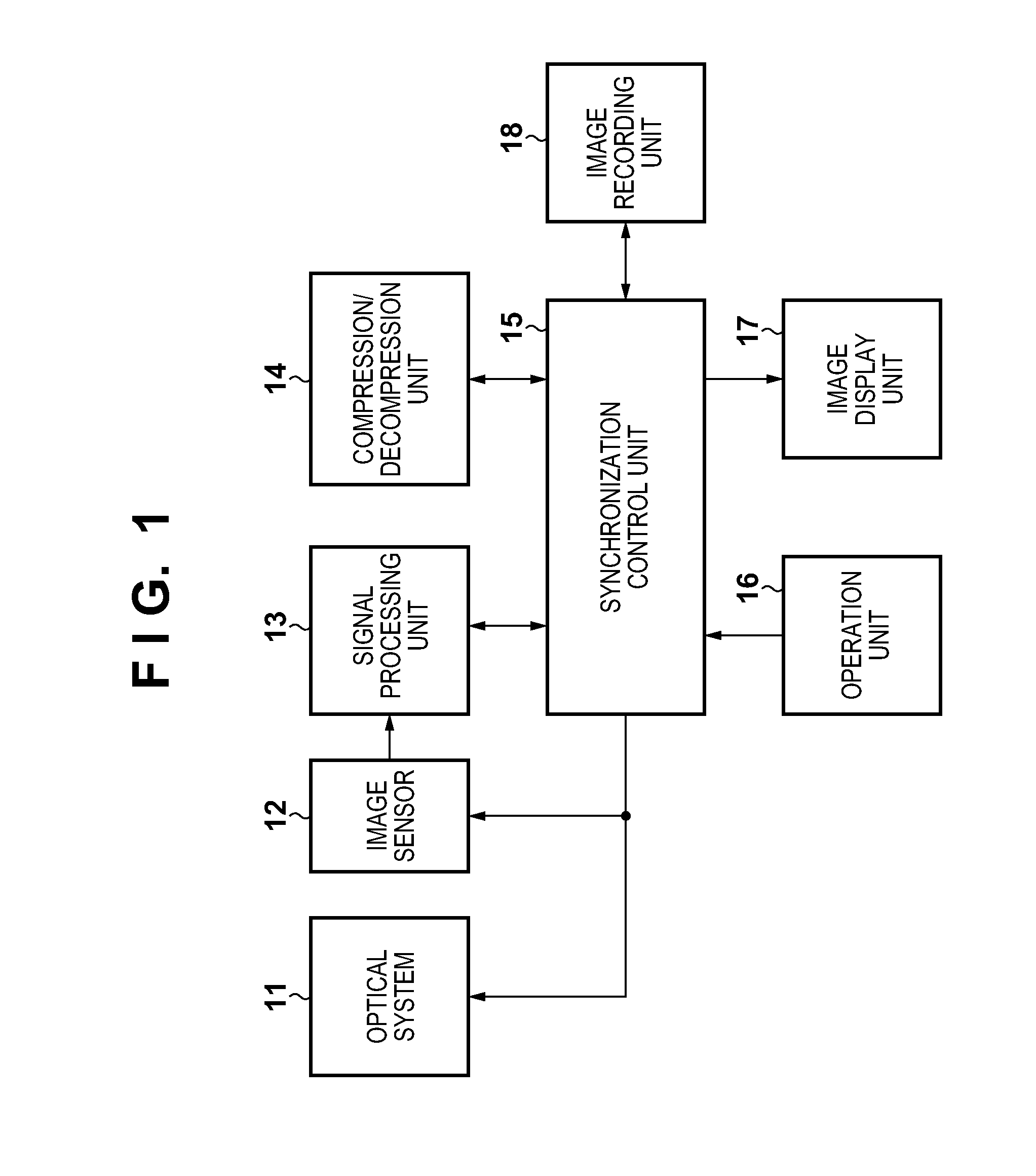

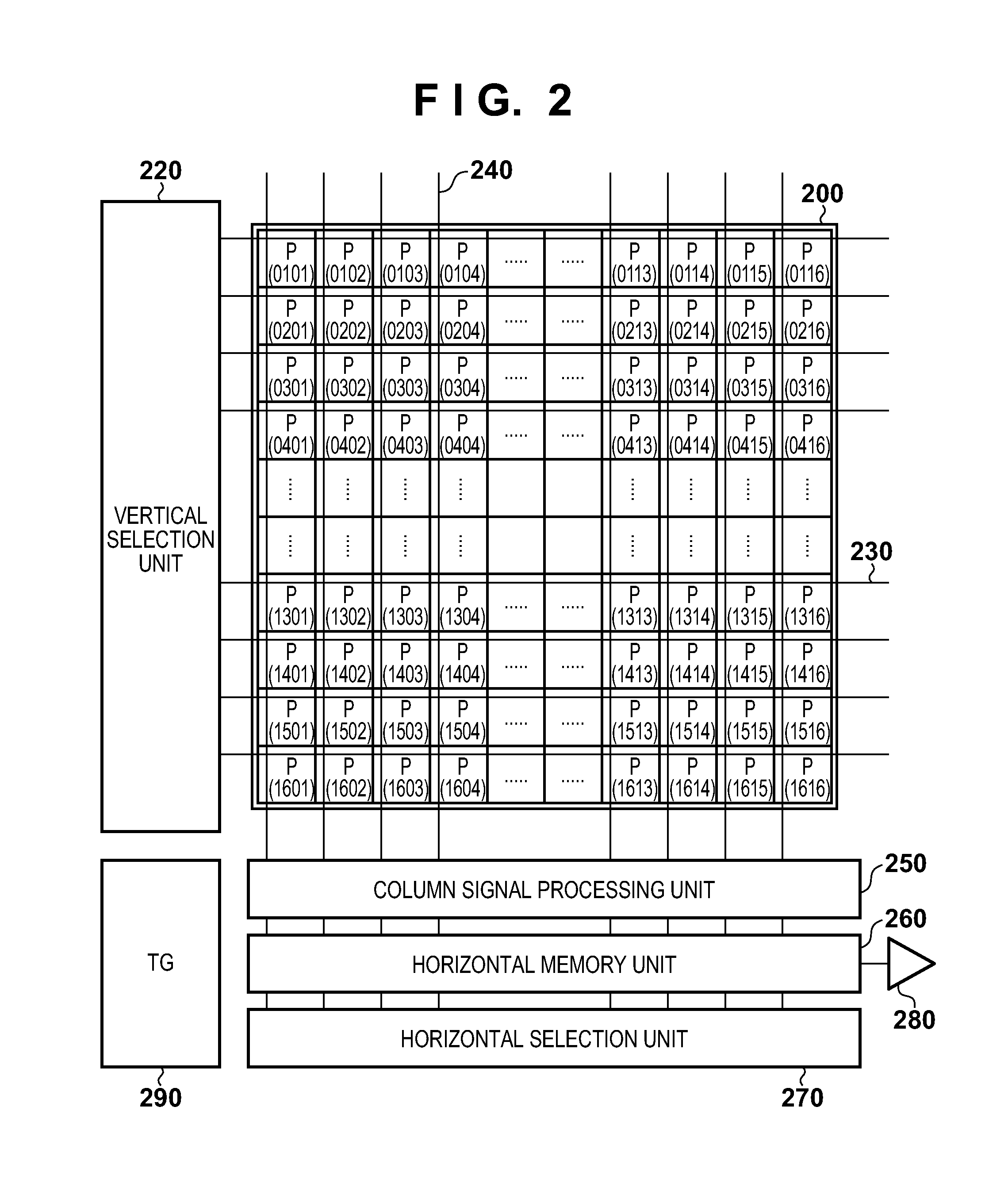

Image capturing apparatus and control method thereof

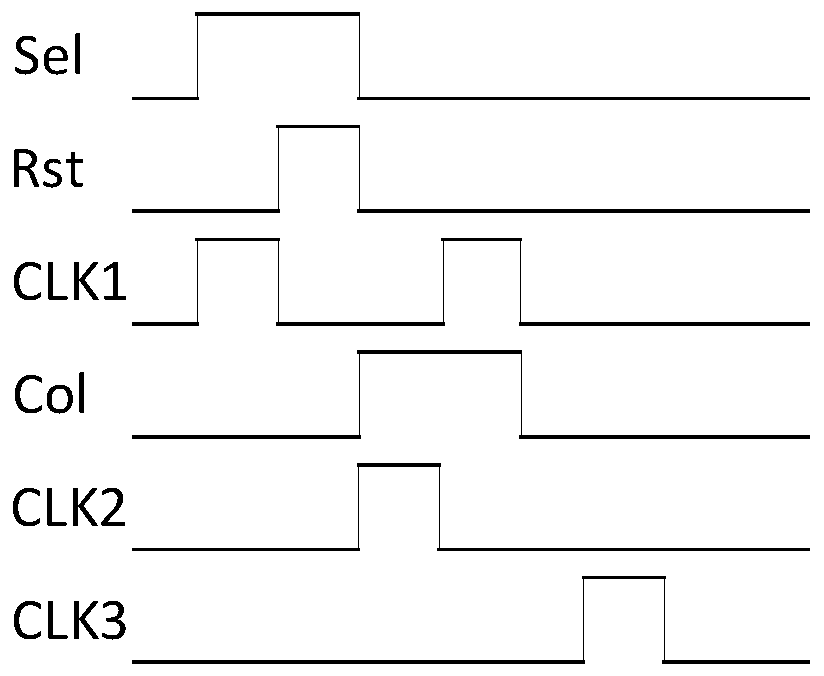

InactiveUS20140218575A1Simple timing controlTelevision system detailsTelevision system scanning detailsTelecommunicationsExposure control

An image capturing apparatus is provided. A synchronizing signal generation unit generates a short-term vertical synchronizing signal VDS and a long-term vertical synchronizing signal VDL, one cycle of which is equal to N cycles of VDS. An exposure control unit performs short-term exposure and long-term exposure for the predetermined number of lines of an image sensor according to VDS and VDL. The exposure control unit starts a read operation of pixel signals for a long-term exposure line in synchronism with VDL, and starts a read operation of pixel signals for a short-term exposure line in synchronism with VDS, which does not overlap a read period Fr_L Readout of pixel signals of a long-term exposure line.

Owner:CANON KK

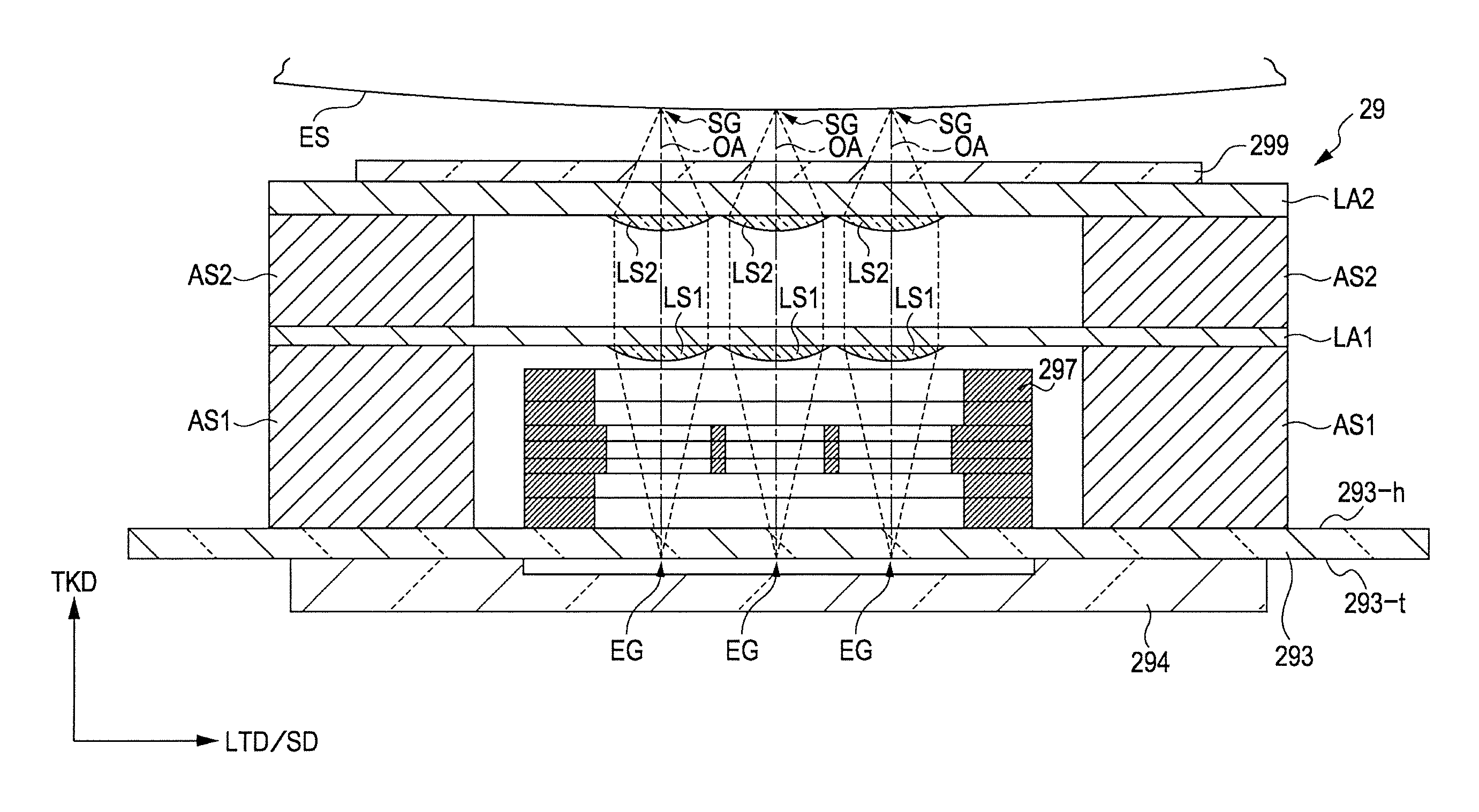

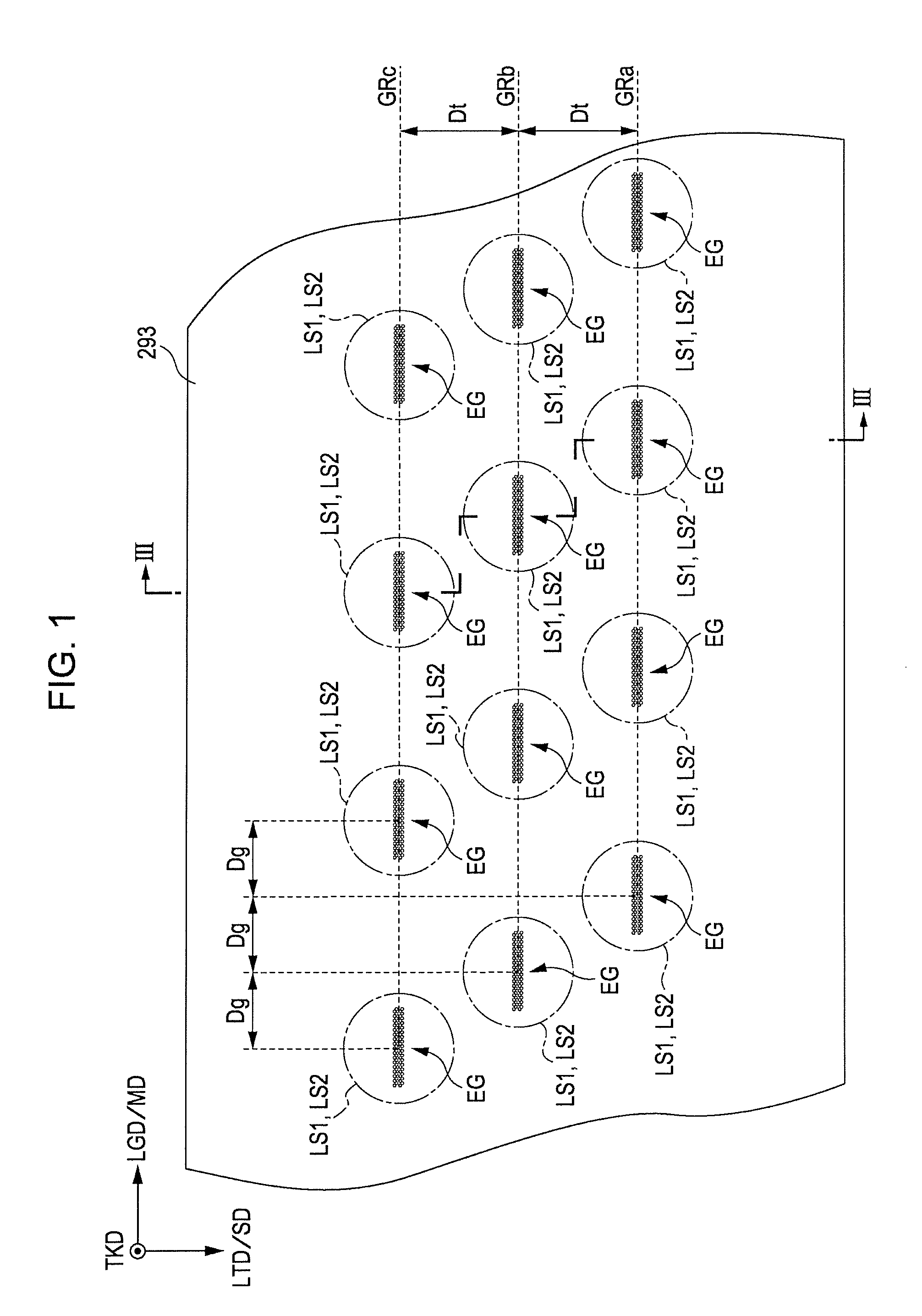

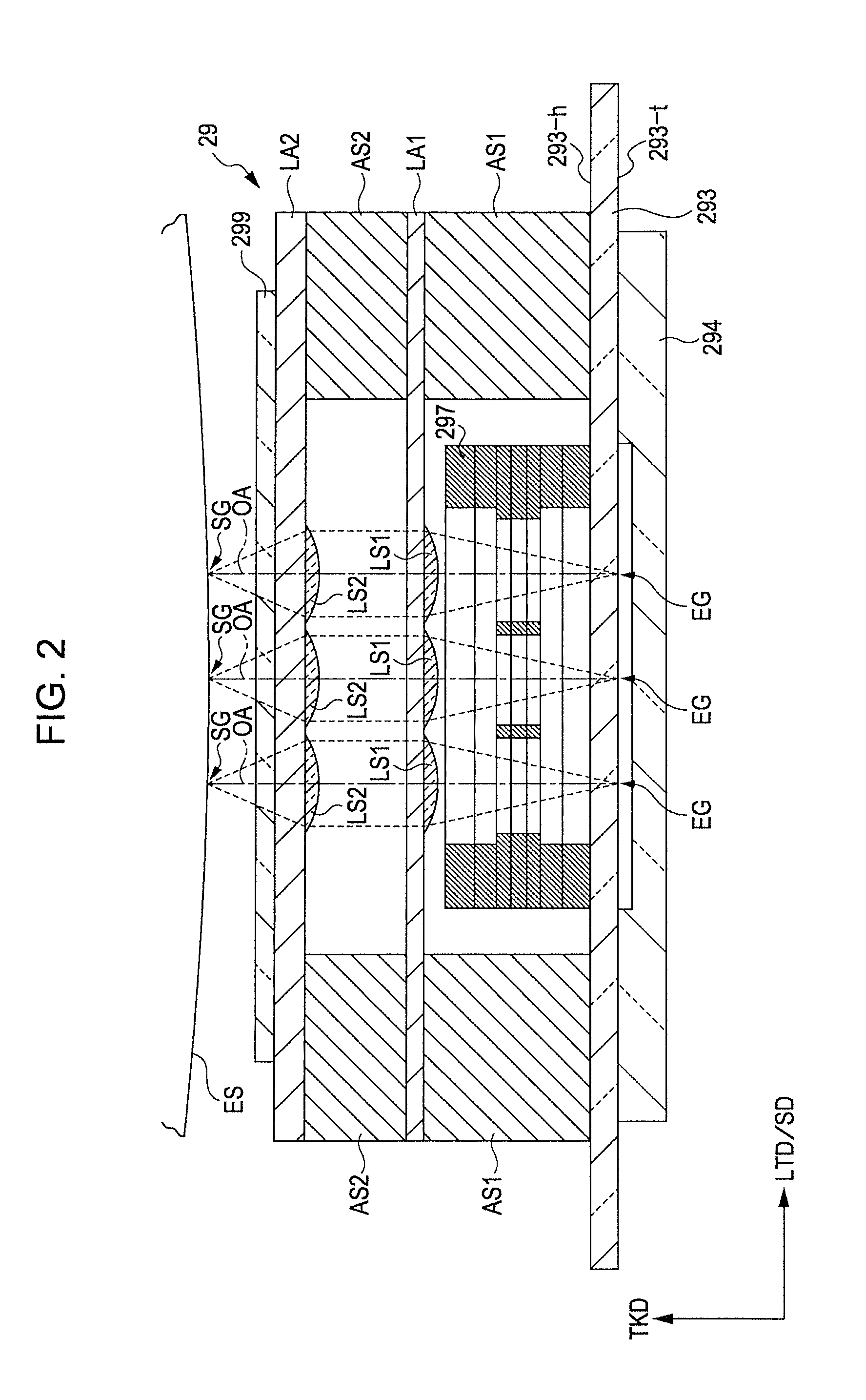

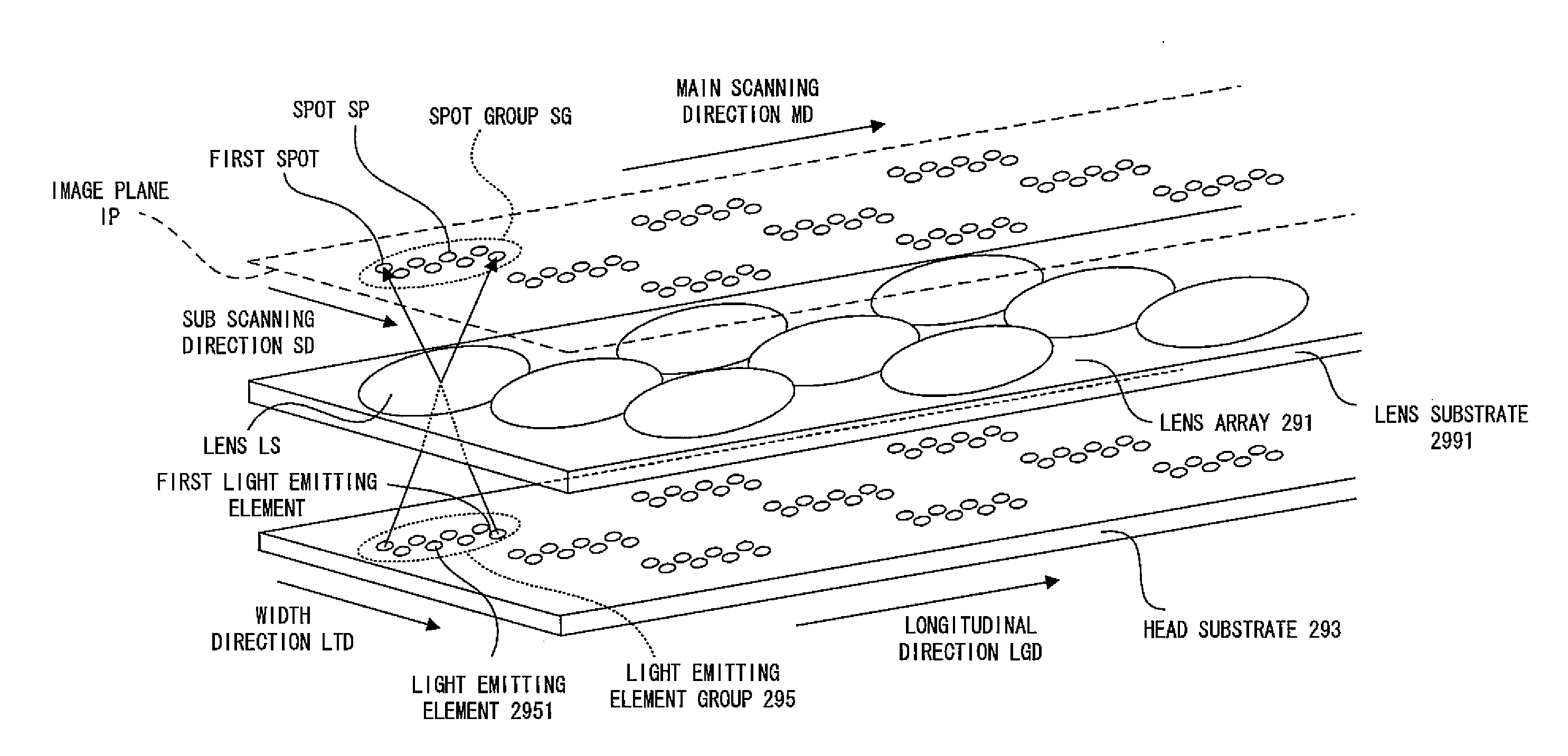

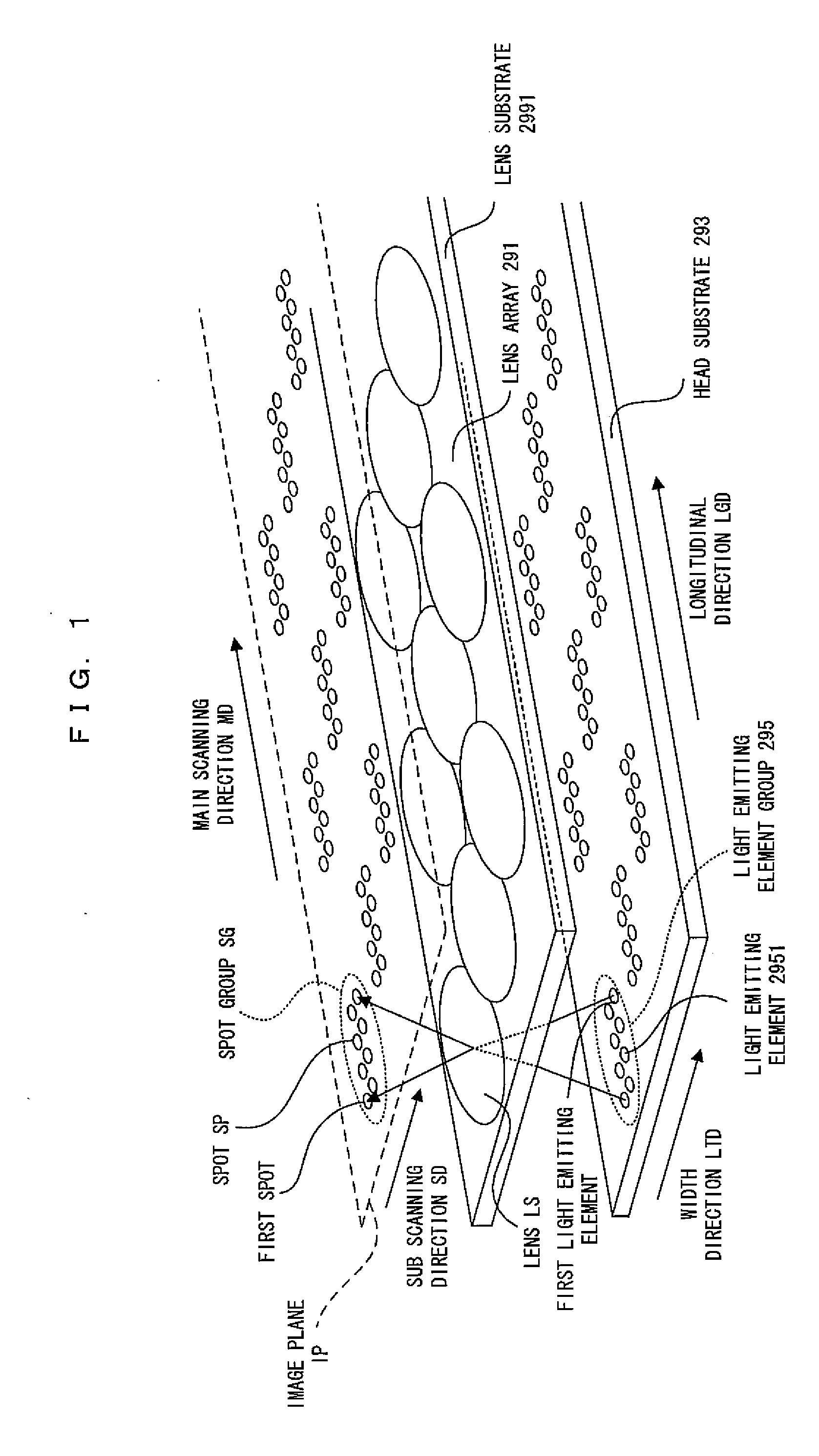

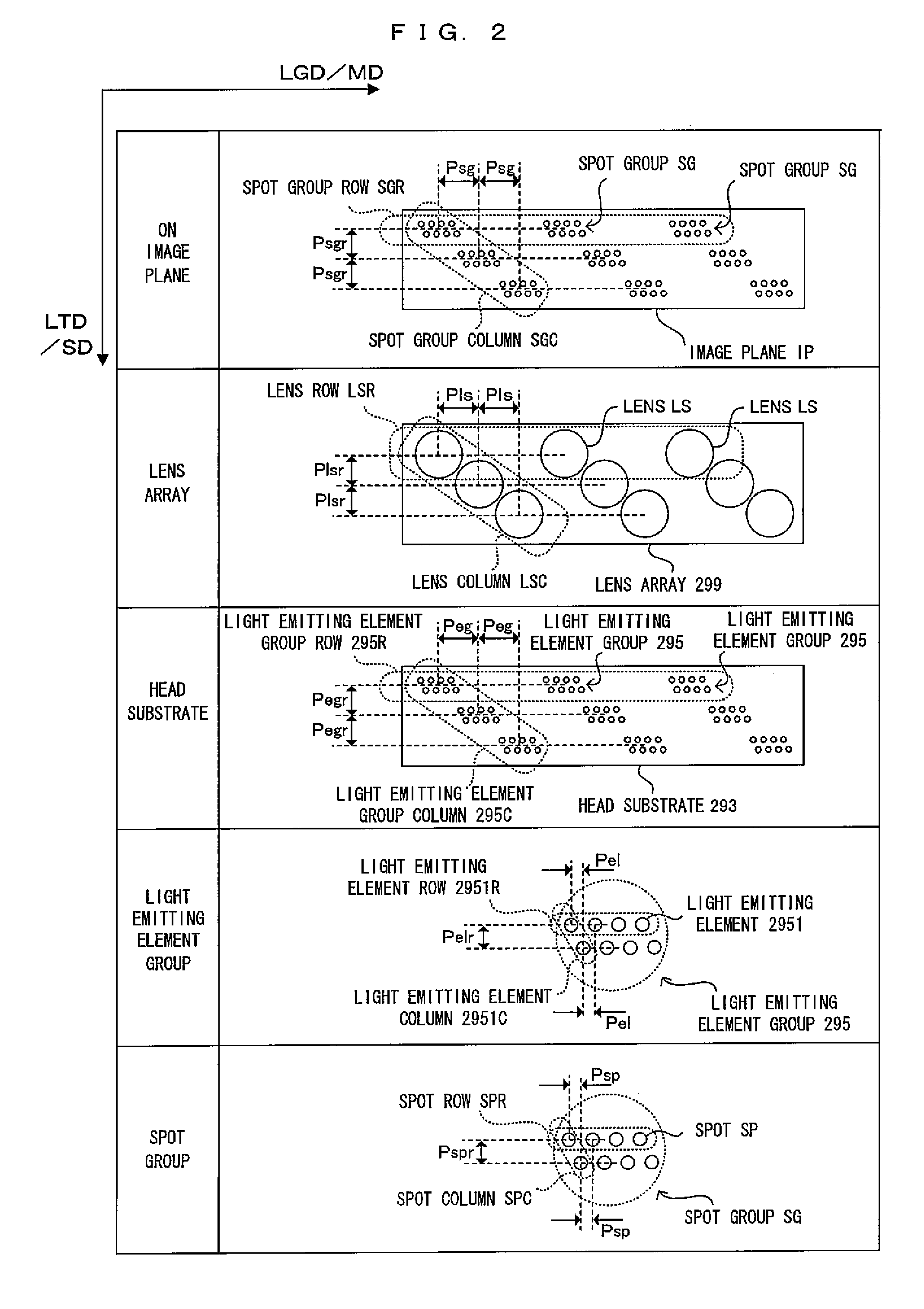

Exposure Head, An Image Forming Apparatus and An Image Forming Method

InactiveUS20090103947A1Simple timing controlEasily realizedElectrographic process apparatusLatent imageImage formation

An image forming apparatus, includes: a latent image carrier that moves in a moving direction; and an exposure head that includes a light emitting element which emits a light and an imaging optical system which images the light emitted from the light emitting element, and is adapted to form a spot on the latent image carrier, wherein a pitch in the moving direction of the latent image carrier between the spots formed by the different imaging optical systems is an integral multiple of a pixel pitch in the moving direction of the latent image carrier.

Owner:SEIKO EPSON CORP

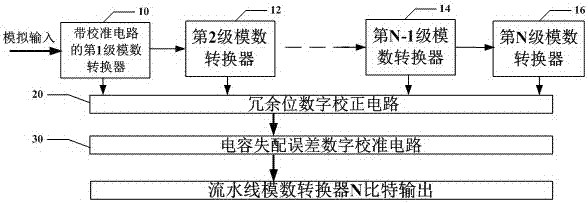

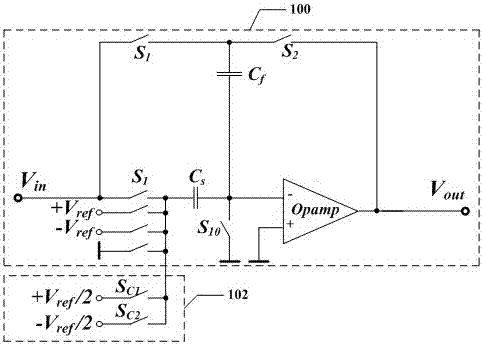

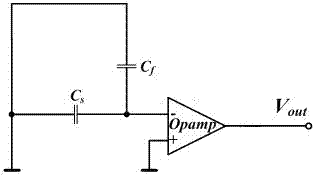

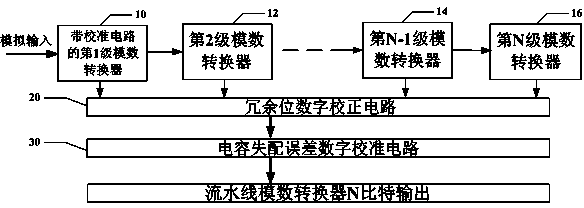

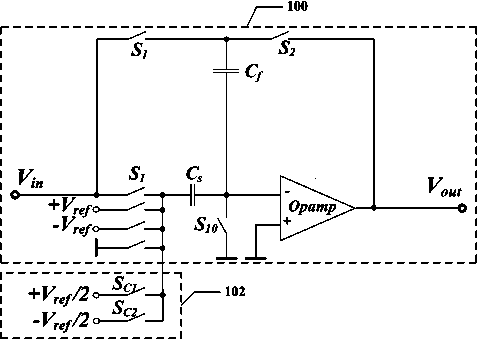

Pipeline ADC (analog to digital converter) and calibration method for capacitor mismatch error of pipeline ADC

ActiveCN104363019AReduce addReduce difficultyAnalogue/digital conversion calibration/testingCapacitanceDigital down converter

An embodiment of the invention discloses a calibration method for a capacitor mismatch error of a pipeline ADC (analog to digital converter). On the basis of the calibration-free structure of the traditional pipeline ADC, a calibration level with the capacitor mismatch error required to be calibrated is composed of a level MDAC (multiplying digital to analog converter) structure and a level-calibrated switch structure, and meanwhile, a capacitor mismatch error digital calibration circuit is added. During the calibration-level capacitor error extracting period, two special inputs are supported by the level-calibrated switch structure to a calibration-level sampling capacitor to obtain two digital codes containing the capacitor mismatch errors, and accordingly digital calibration is performed by extracting the calibration-level capacitor mismatch error. The calibration method is simple in structure, fewer additional elements are required, sequential control is easy, and the problem that poor static characteristics, caused by capacitor mismatch, is calibrated is solved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

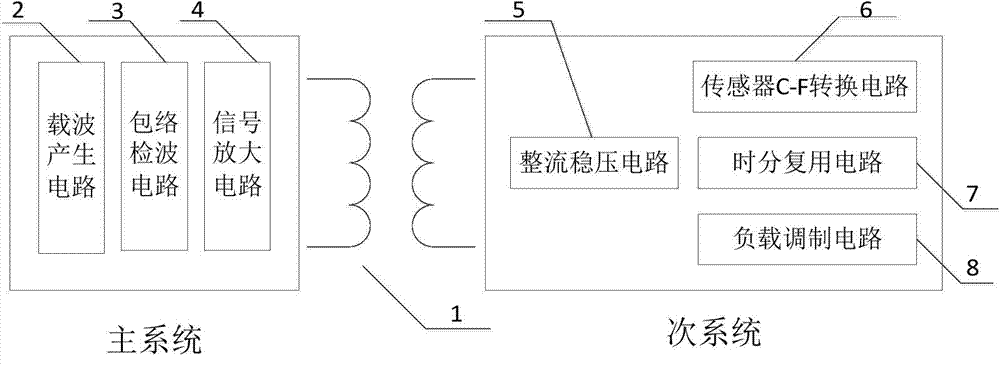

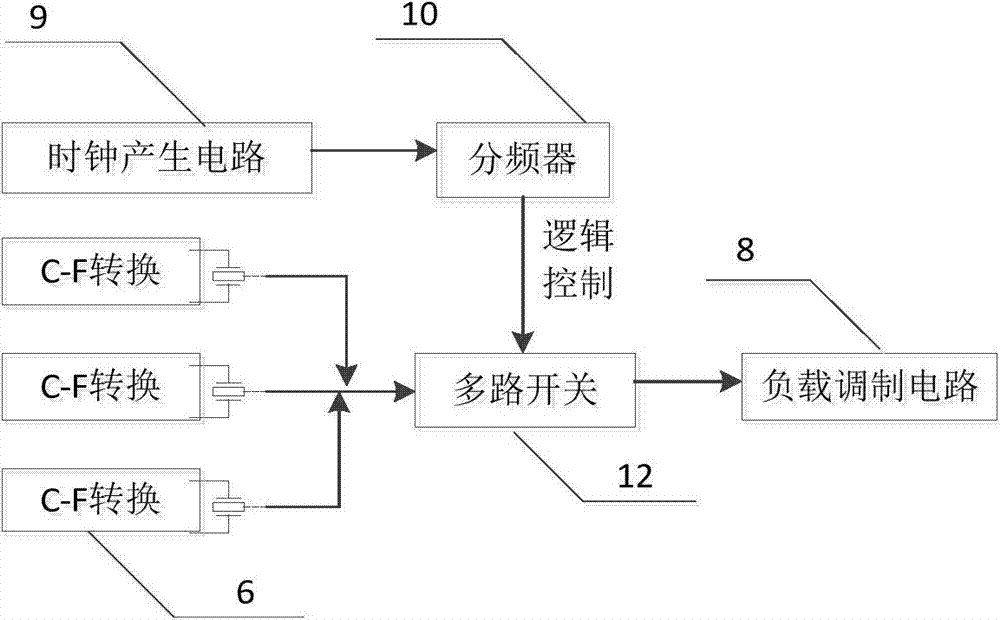

Passive wireless multi-parameter sensor system and multi-parameter measurement method thereof

InactiveCN103575306AIncrease the number ofIncrease gating capabilityConverting sensor output electrically/magneticallyCapacitanceCarrier signal

The invention discloses a passive wireless multi-parameter sensor system and a multi-parameter measurement method of the passive wireless multi-parameter sensor system. Multi-parameter measurement and signal transmission are achieved according to the time-division multiplexing technology. The system comprises a primary system and a subsystem. A signal transmitted by the primary system serves as a modulation carrier and also provides energy for the subsystem. The subsystem receives the signal transmitted by the primary system, and the signal is subject to circuit rectification and voltage stabilization and then provides energy for the subsystem. The subsystem comprises a plurality of capacitance-type sensors sensing changes of system-environment physical quantities. Capacitance signals of the sensors are converted into frequency signals through a C-F conversion circuit; then switching-on and switching-off of a load switch are controlled by multi-path frequency signals through one transmission channel according to the time-division multiplexing technology, and load modulation of a circuit is completed by changing the load impedance of the subsystem. Modulated signals are received by the primary system through inductive coupling to carry out demodulation and amplifying processing. Due to the adoption of the system, the number of measured parameters can be conveniently increased, and it is only required that the number of frequency dividers is increased and the state switching ability of a multiple-way switch is improved.

Owner:SOUTHEAST UNIV

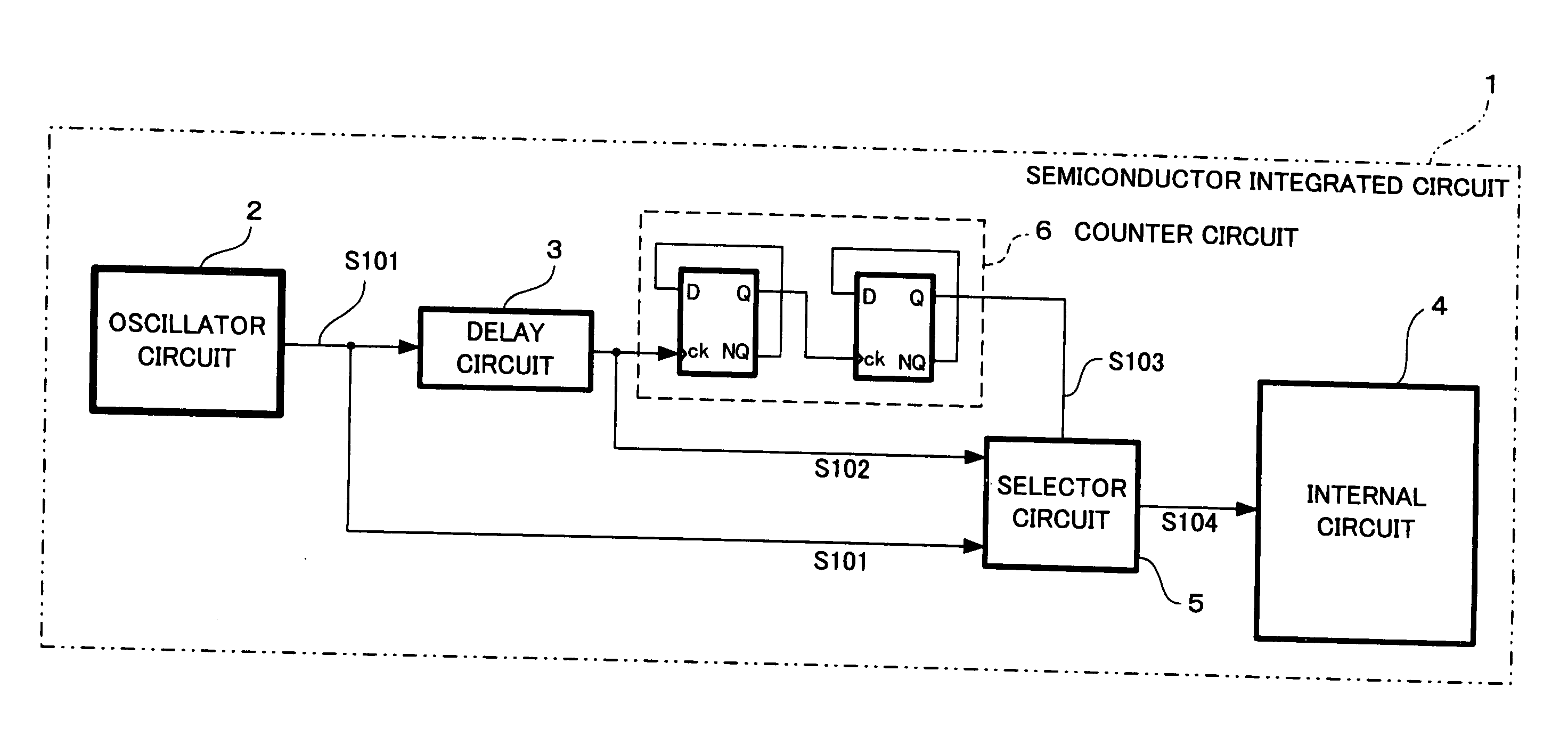

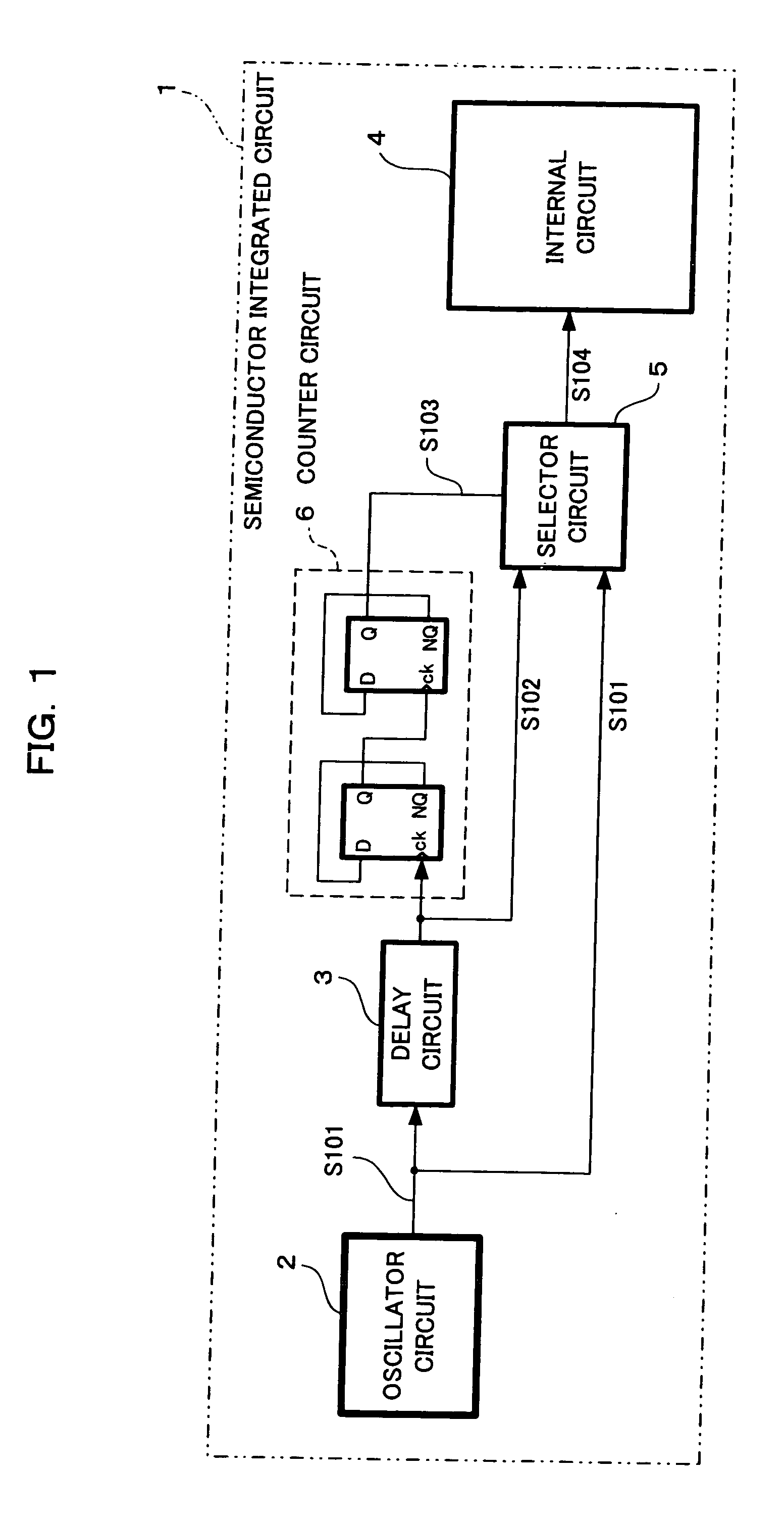

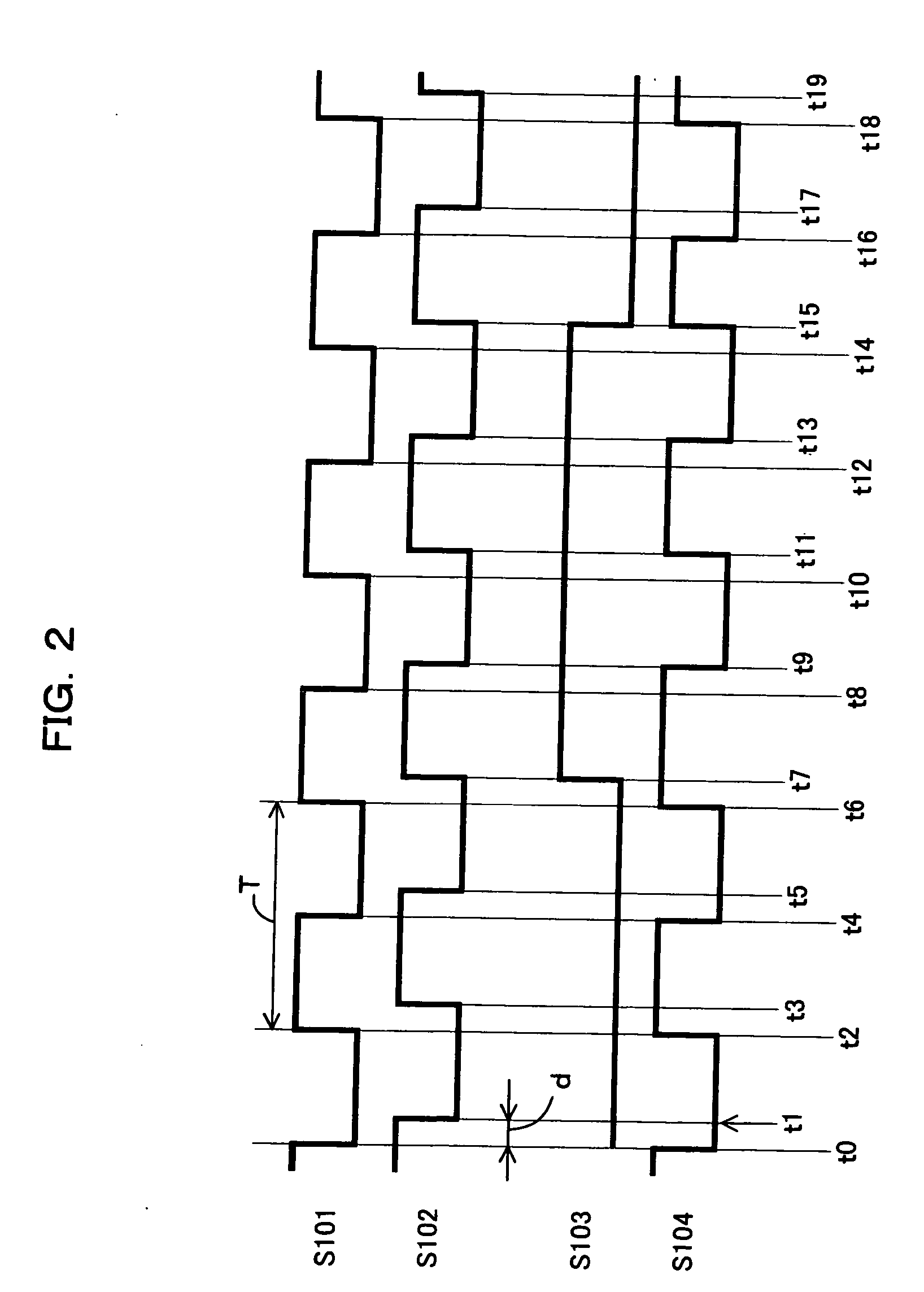

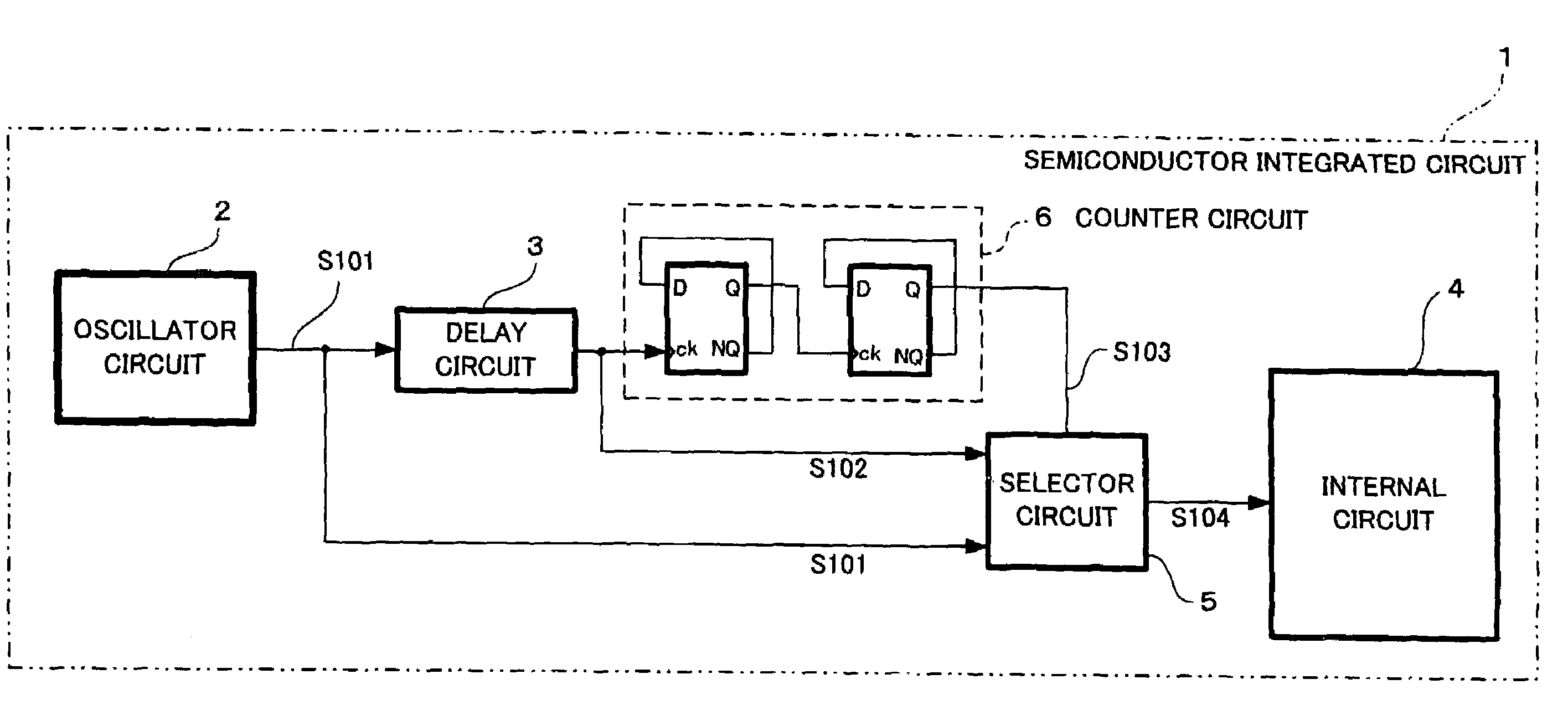

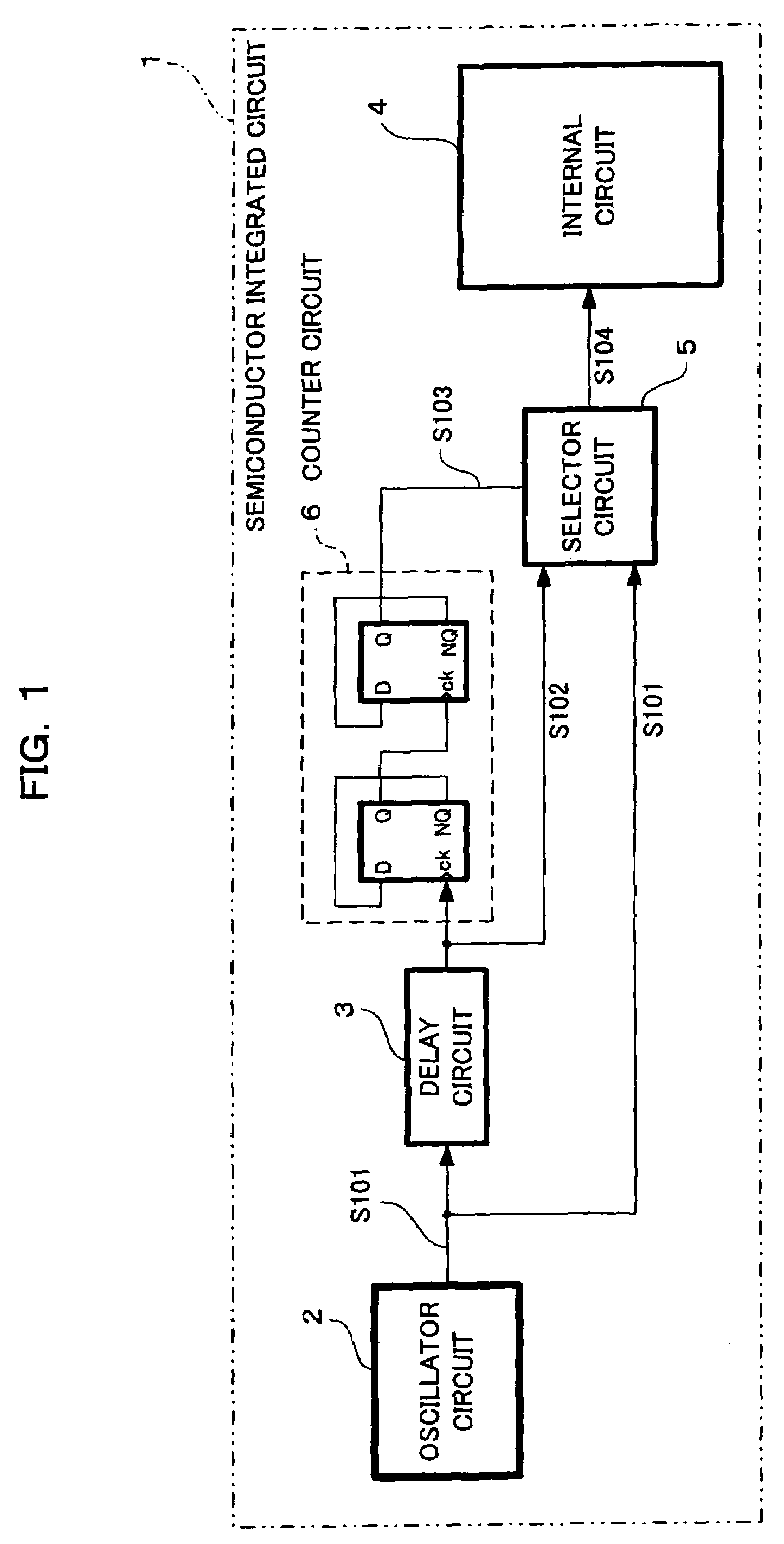

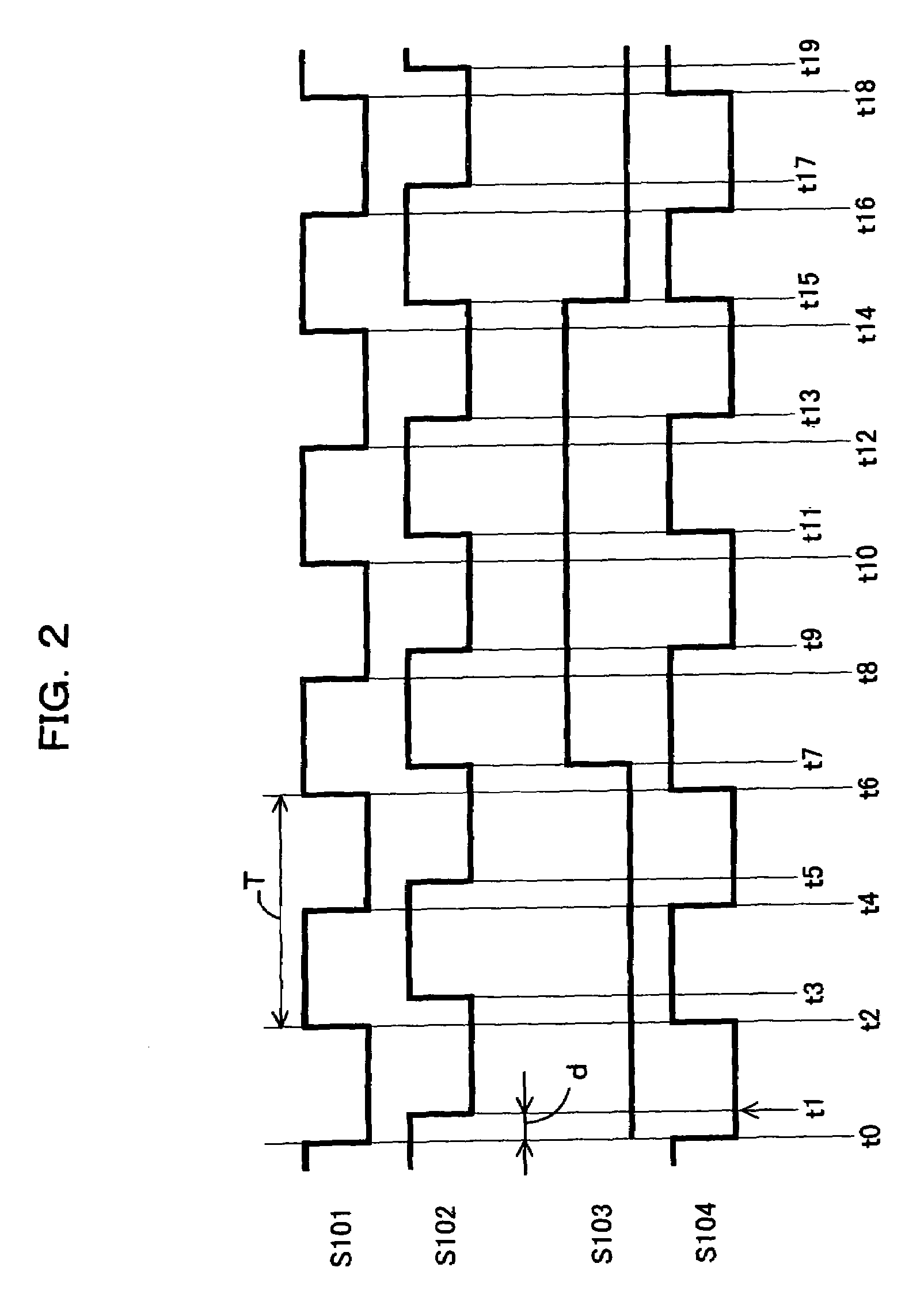

Semiconductor equipment

ActiveUS20060017487A1Easy to changeNot easy to electromagnetic interferenceElectronic switchingElectric pulse generatorHarmonicElectromagnetic interference

There is provided a semiconductor integrated circuit in which a source clock (S101) is inputted to a delay circuit (3), a counter circuit (6) is operated in response to a delay clock (S102) which is the output of the delay circuit (3), a clock used as a system clock by an internal circuit (4) is selected from the source clock (S101) and the delay clock (S102) based on the value of the counter circuit (6), and the duty cycle of the system clock is changed, so that it is possible to reduce electromagnetic interference resulting from harmonics generated by the switching of the internal circuit.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

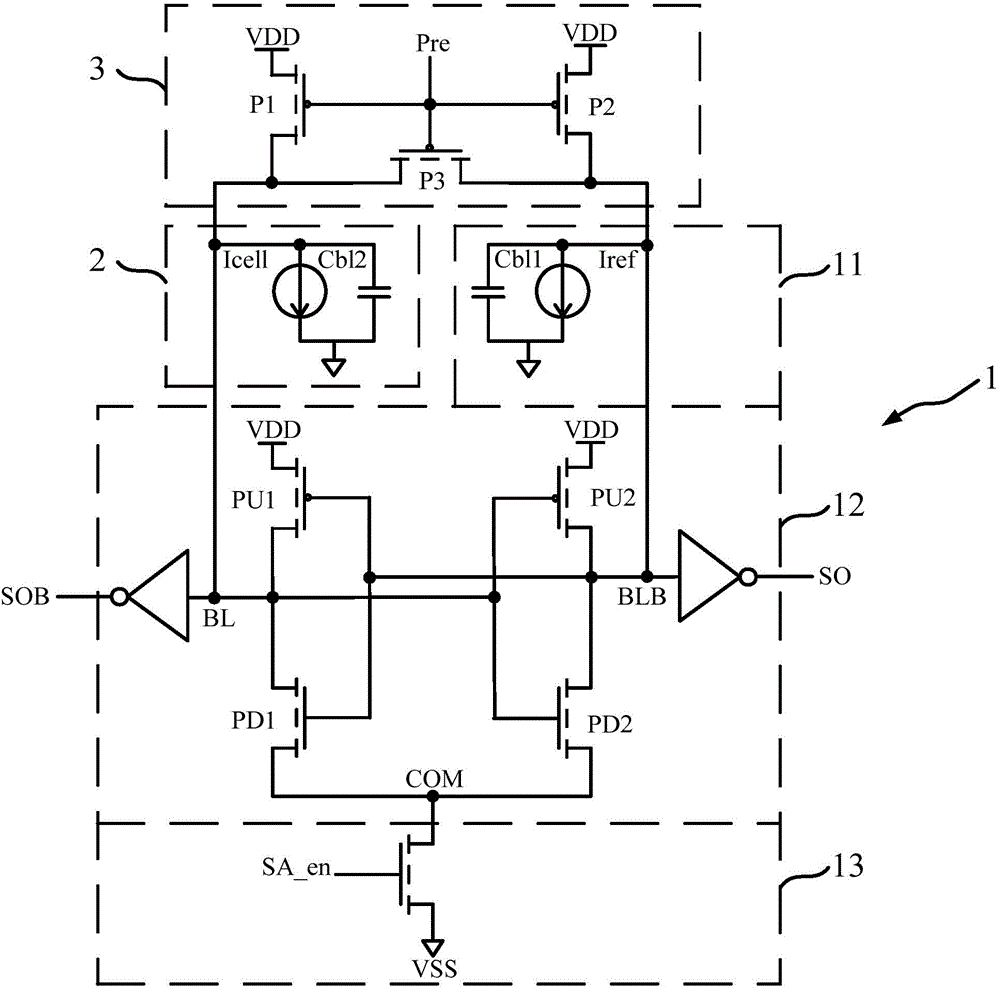

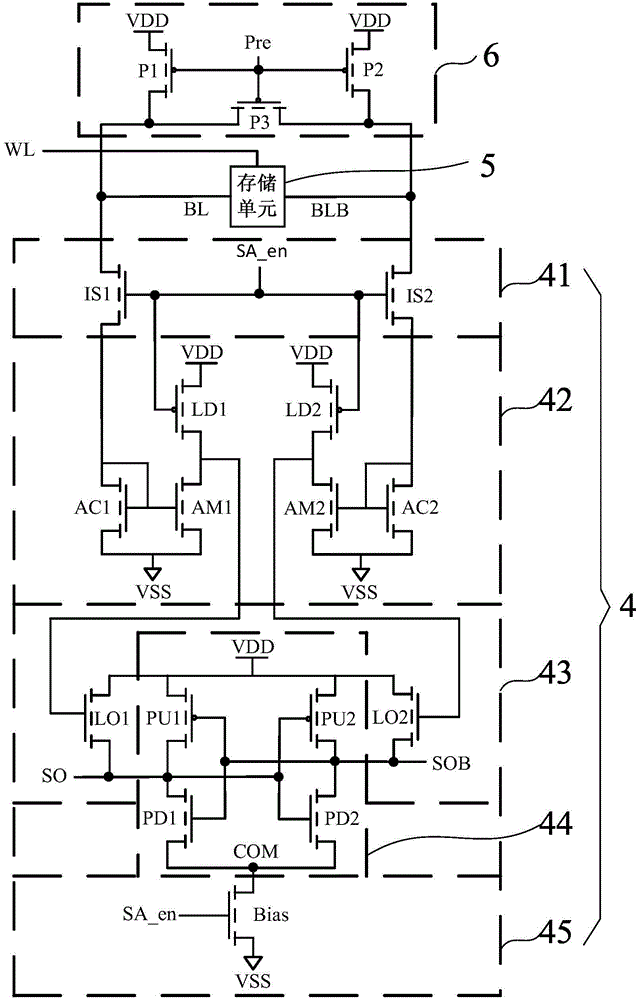

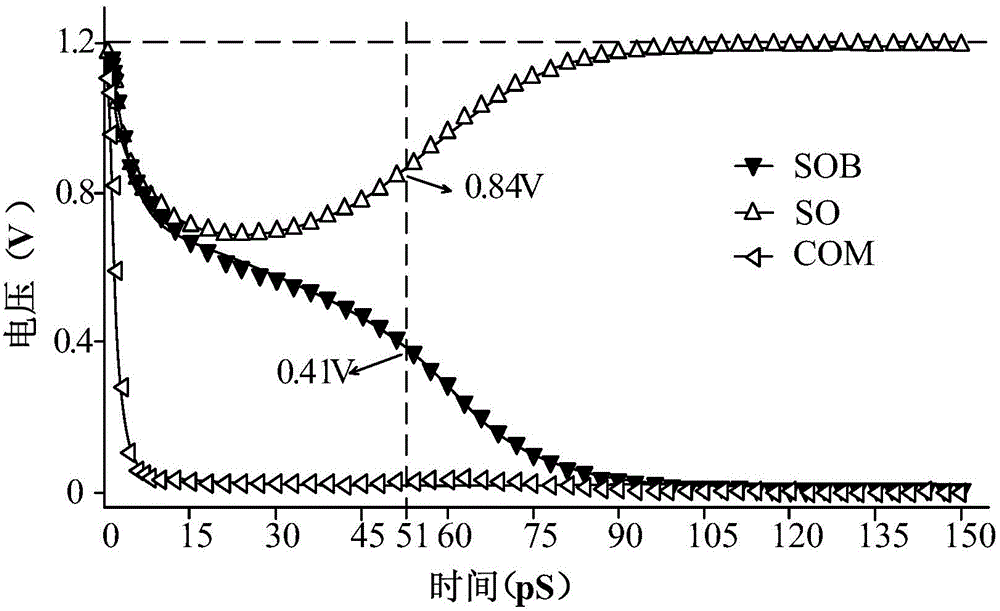

High-speed current sensitive amplifier applied to static random access memory circuit

ActiveCN104681055AIncreased read speed capabilitySimple timing controlDigital storageSoi cmosStatic random-access memory

The invention provides a sensitive amplifier, and discloses a high-speed current sensitivity amplifier applied to a static random access memory circuit. The high-speed current sensitivity amplifier at least comprises a current isolation circuit, a current amplification circuit, a voltage reduction circuit, a latch circuit and an offset circuit, wherein the current isolation circuit is used for isolating input signals from output signals; the current amplification circuit is connected with the current isolation circuit and is used for amplifying input current and used for outputting corresponding voltage signals; the voltage reduction circuit is connected with the current amplification circuit and is used for reducing voltage of signals output from the current amplification circuit; the latch circuit is connected with the voltage reduction circuit and is used for latching signals outputted from the voltage reduction circuit; the offset circuit is connected with the latch circuit and is used for providing offset for the latch circuit. The high-speed current sensitivity amplifier is not only simple in time-sequence control, but also applicable to design of a static random access memory circuit, and particularly applicable to high-speed design, and the reading time of the sensitive amplifier can be effectively shortened; in addition, based on an SOI CMOS process of 0.13 micrometer, the simulation result shows that it takes 51pS to output voltage high-level of 70%VDD by the sensitive amplifier.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

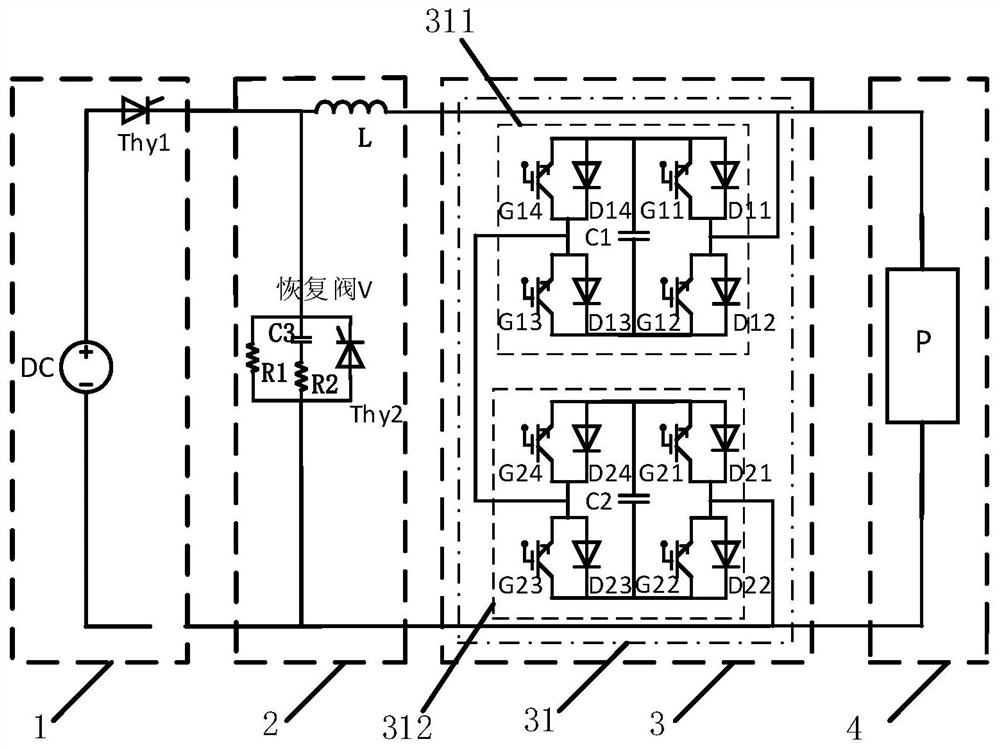

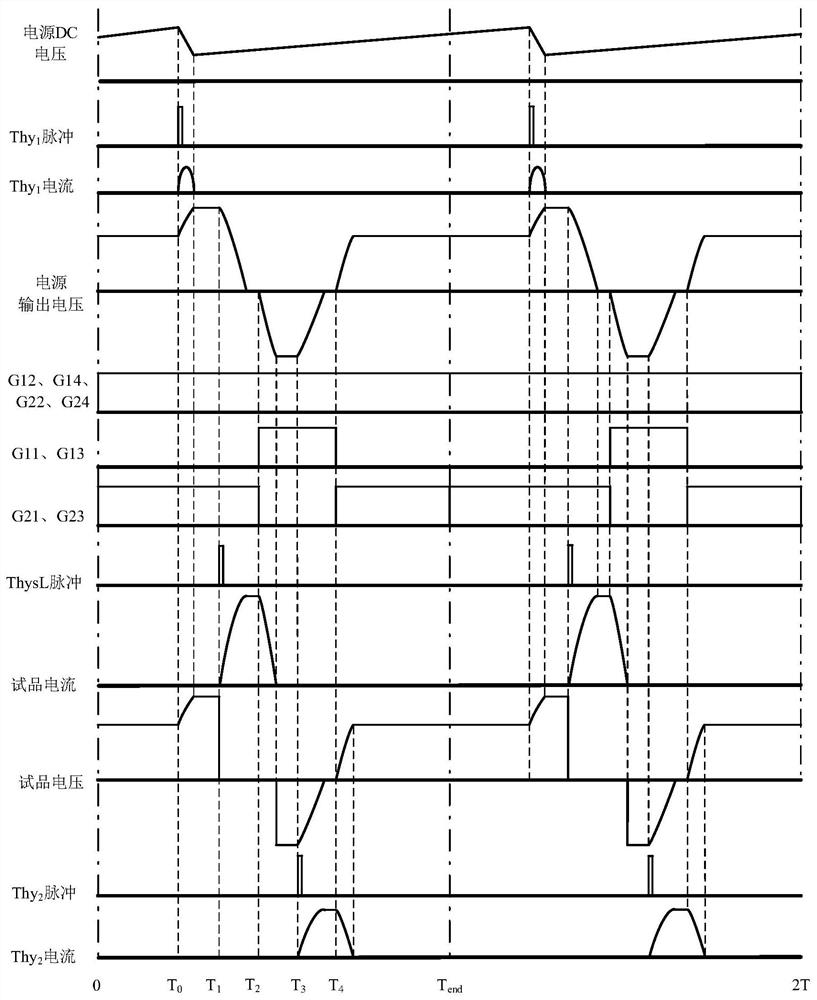

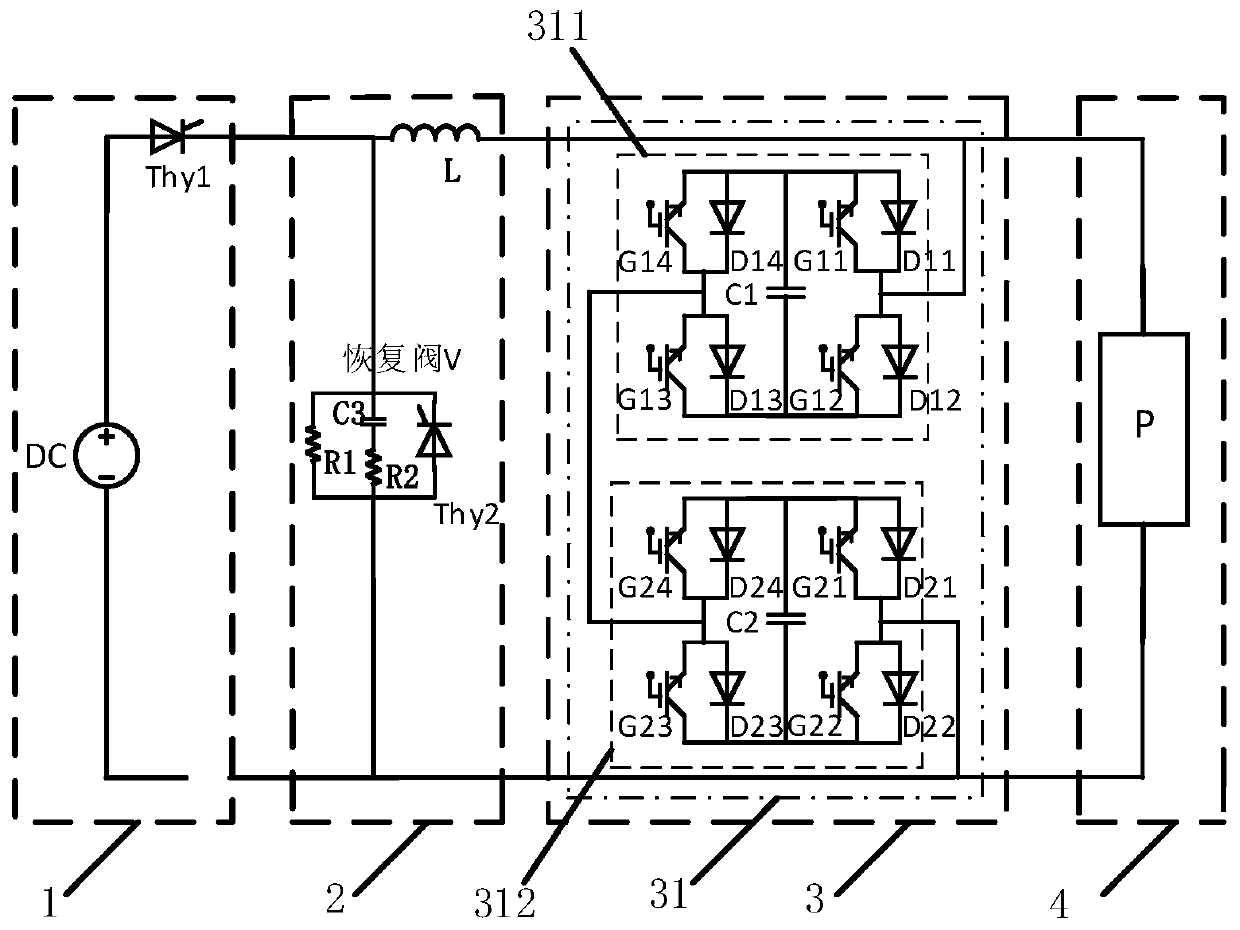

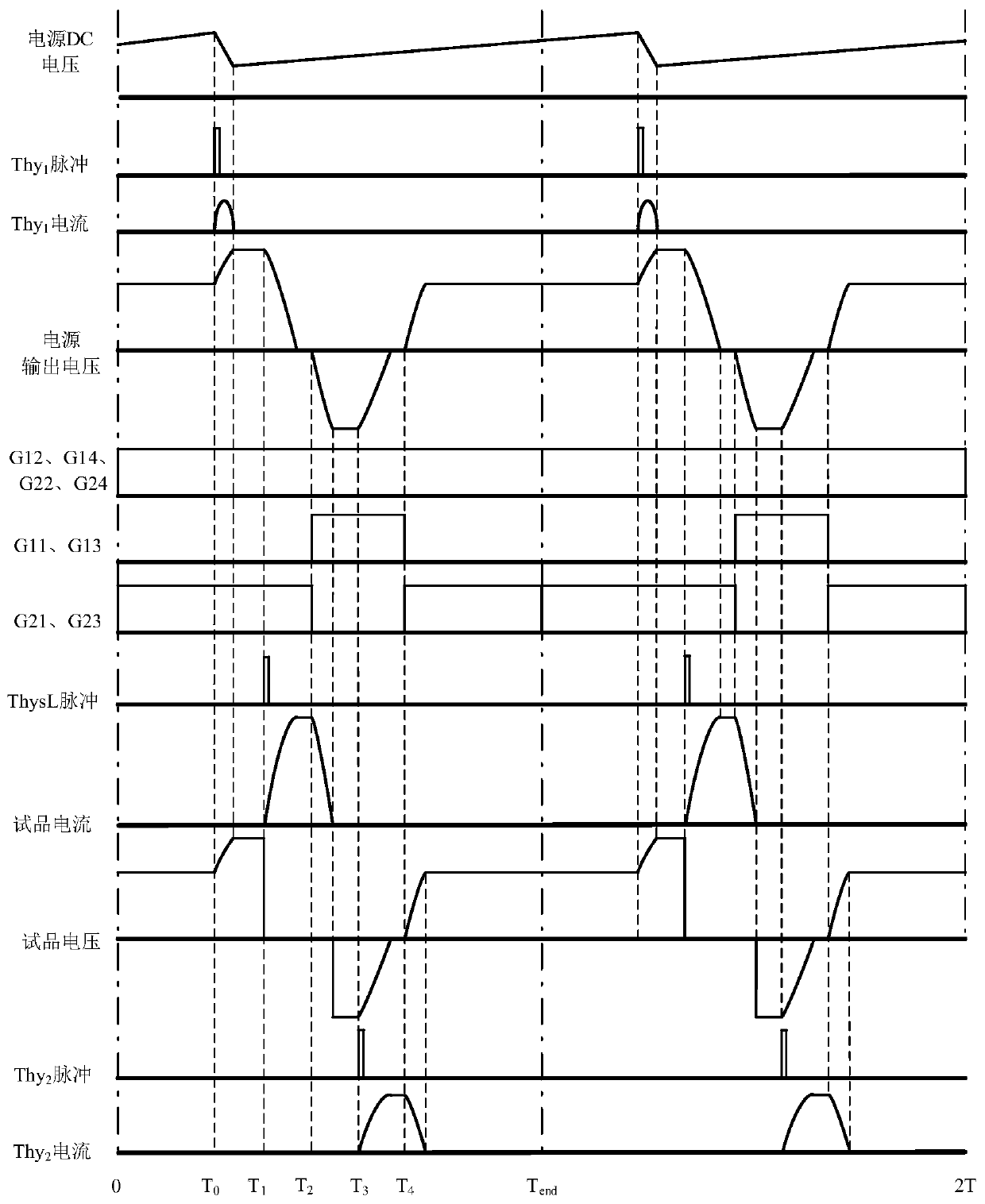

Test circuit and method for testing on-off characteristics of converter valve

ActiveCN111562494ASimple timing controlThe cycle runs continuouslyCircuit interrupters testingTest objectBridge circuit

The invention discloses a test circuit and method for testing the on-off characteristics of a converter valve. In the test circuit, the positive electrode of a DC power supply in an energy supplementloop is connected to the anode of a first thyristor; one end of a recovery valve in a recovery loop is connected to one end of an inductor and the cathode of the first thyristor, and the other end ofthe recovery valve is connected to the negative electrode of the DC power supply; one end of an H-bridge circuit in an output loop is connected to the other end of the inductor, the other end of the H-bridge circuit is connected to the negative electrode of the DC power supply, the H-bridge circuit comprises a first sub-module comprising a first capacitor and a first switch assembly and a second sub-module comprising a second capacitor and a second switch assembly, and the capacitance of the first capacitor is different from that of the second capacitor; a load loop comprises a to-be-tested valve test object, which is connected to two ends of the H-bridge circuit. By implementing the invention, a test platform which can be periodically operated and of which the turn-on voltage is differentfrom the turn-off voltage is built, and the on-off characteristics of the valve and the electrical performance of internal parts can be tested in a targeted manner.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

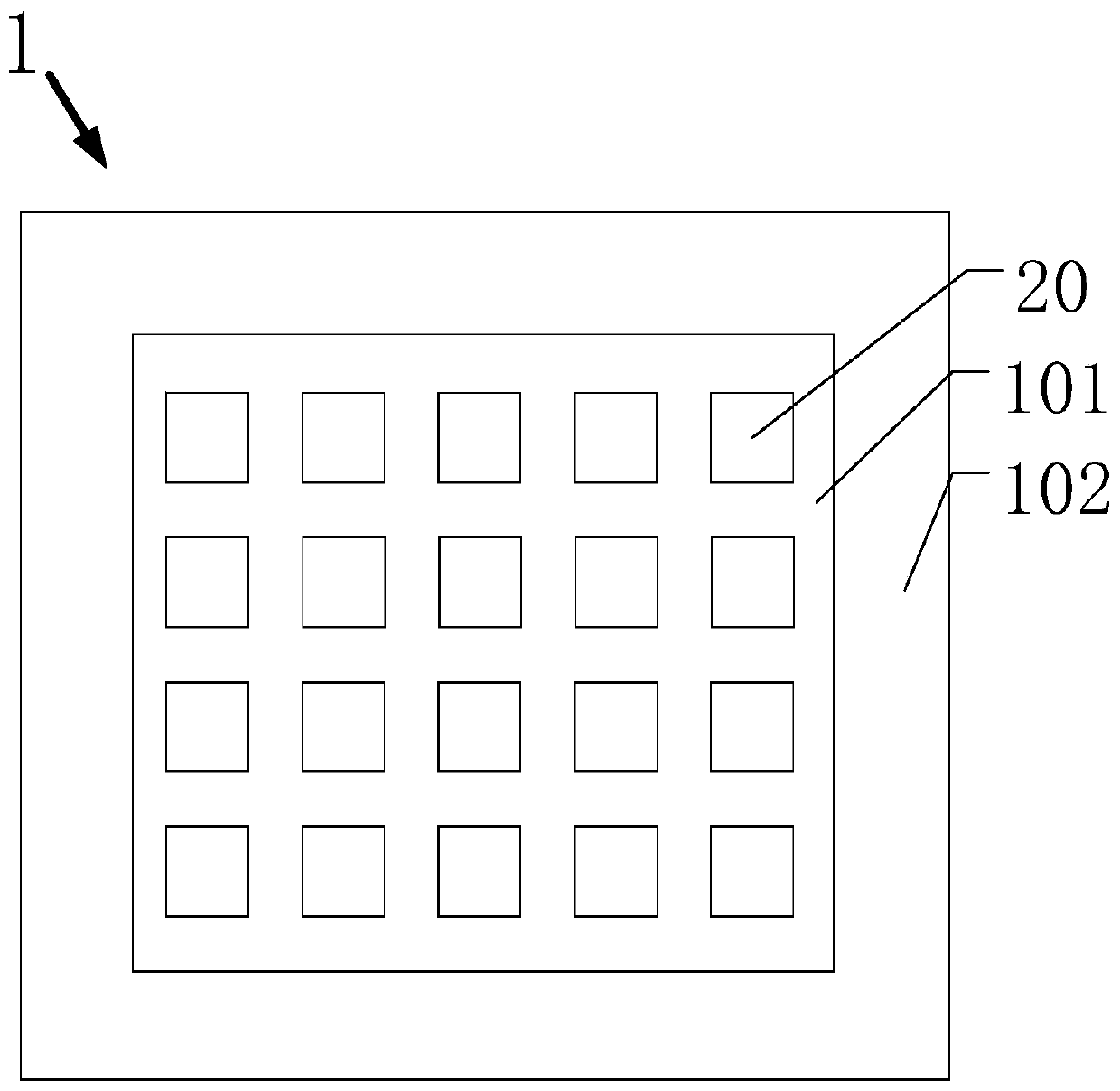

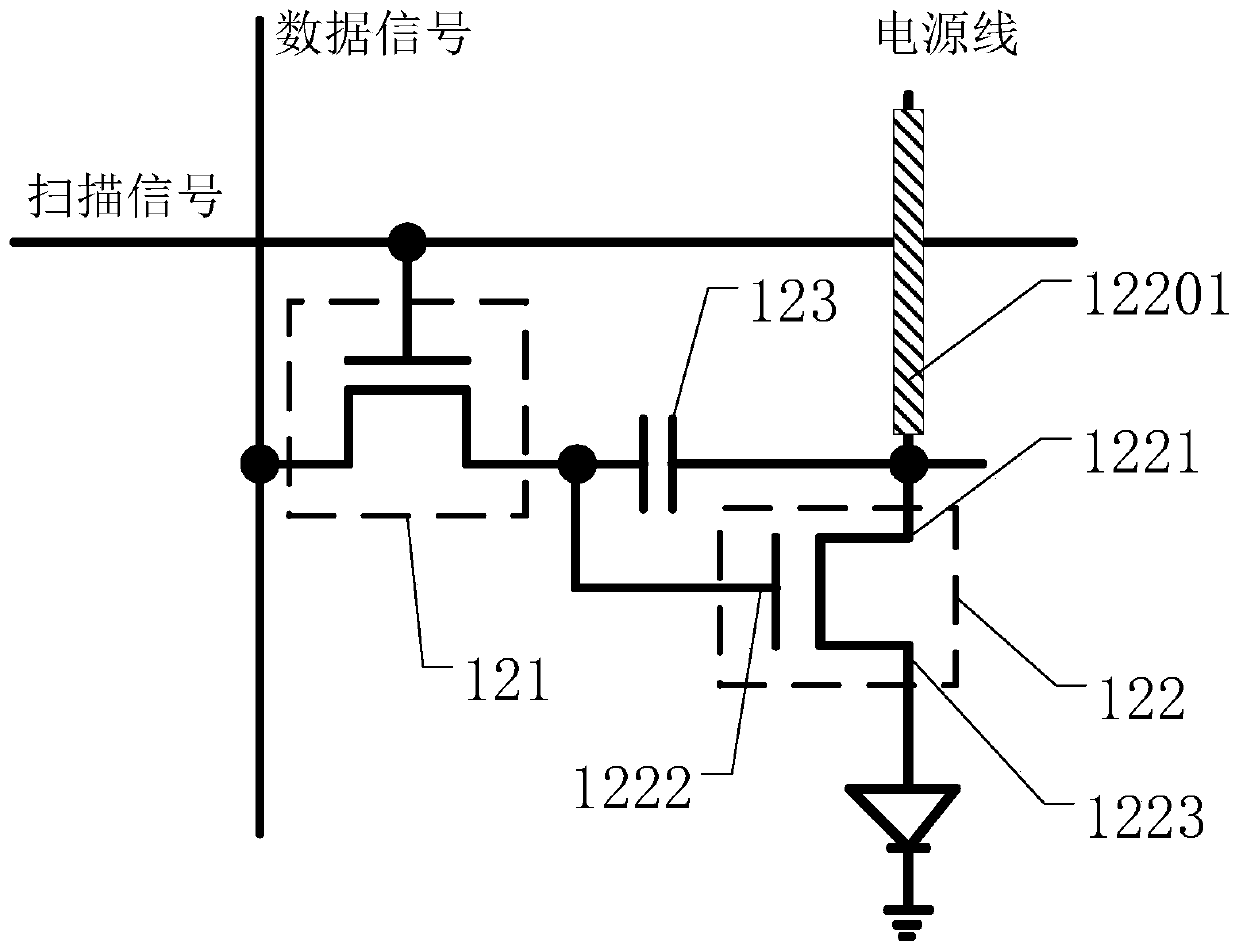

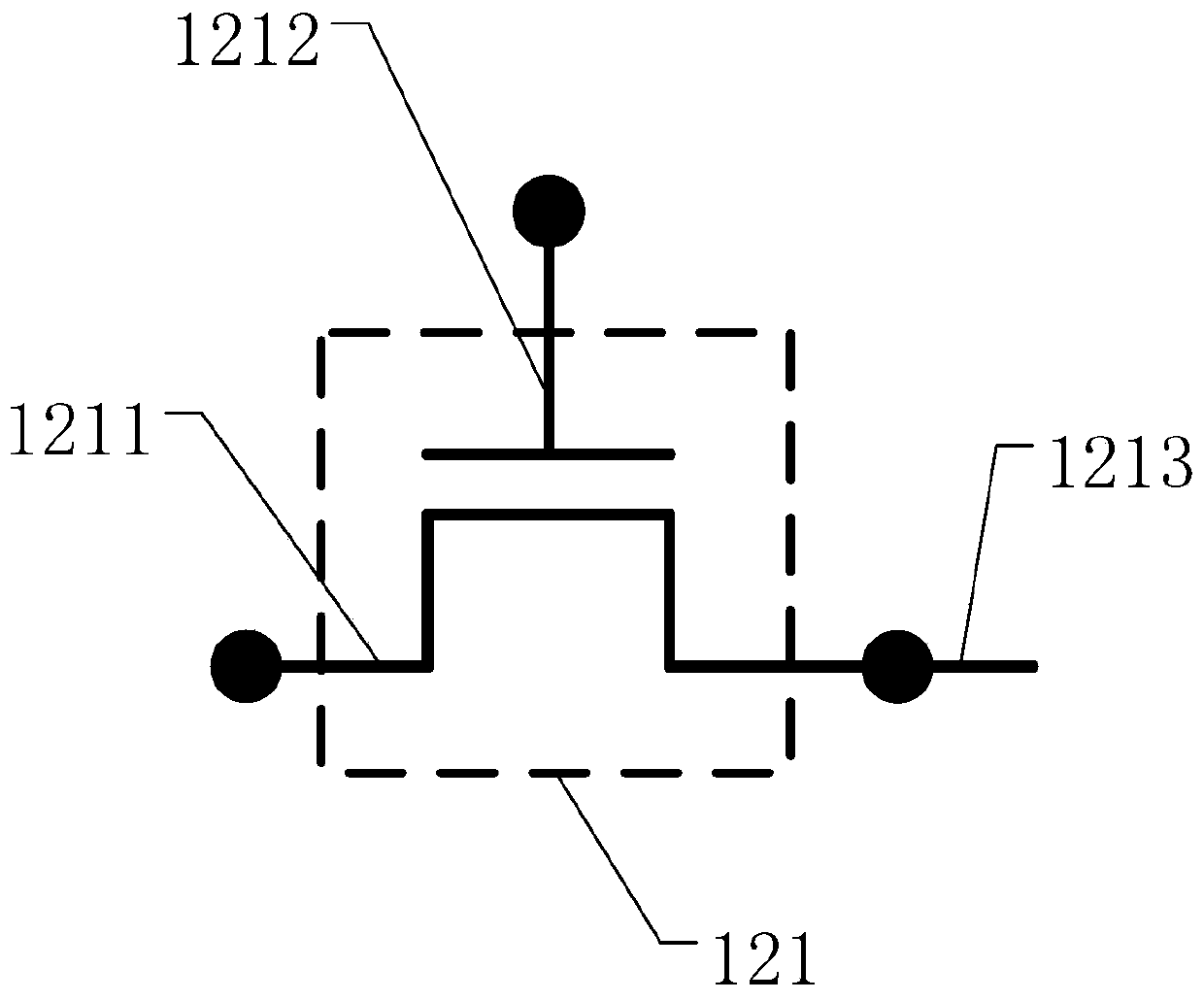

Display panel and preparation method thereof

InactiveCN111211117AImprove manufacturing yieldSmall pressure dropStatic indicating devicesSolid-state devicesImaging qualityHemt circuits

The invention provides a display panel and a preparation method thereof. The display panel comprises a first substrate and a plurality of LED chips; the first substrate is provided with a plurality ofthin film transistor units; the plurality of LED chips are distributed on the first substrate in an array; each thin film transistor unit is correspondingly connected with and controls one LED chip.According to the display panel and the preparation method thereof, the array circuit is prepared on the glass substrate, so that each LED chip can be independently controlled; such kind of control mode can adjust and control display image quality more accurately, and an image quality improvement effect is more obvious. According to a gray scale driving mode, field frequency modulation driving is adopted, sequential control is simpler, dependence on liquid crystal response speed is reduced, and color cast caused by direct current driving is avoided. In the manufacturing process of the display substrate, voltage drop caused by circuit impedance is reduced by adding a high-conductivity metal wire on a power line, so that poor display is avoided. A nano-silver paste technology is adopted to solve the problem of chip bonding caused by a non-copper manufacturing process, and the manufacturing yield of the display panel is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Semiconductor equipment

ActiveUS7288979B2Easy to changeNot easy to electromagnetic interferenceElectronic switchingElectric pulse generatorHarmonicElectromagnetic interference

There is provided a semiconductor integrated circuit in which a source clock (S101) is inputted to a delay circuit (3), a counter circuit (6) is operated in response to a delay clock (S102) which is the output of the delay circuit (3), a clock used as a system clock by an internal circuit (4) is selected from the source clock (S101) and the delay clock (S102) based on the value of the counter circuit (6), and the duty cycle of the system clock is changed, so that it is possible to reduce electromagnetic interference resulting from harmonics generated by the switching of the internal circuit.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

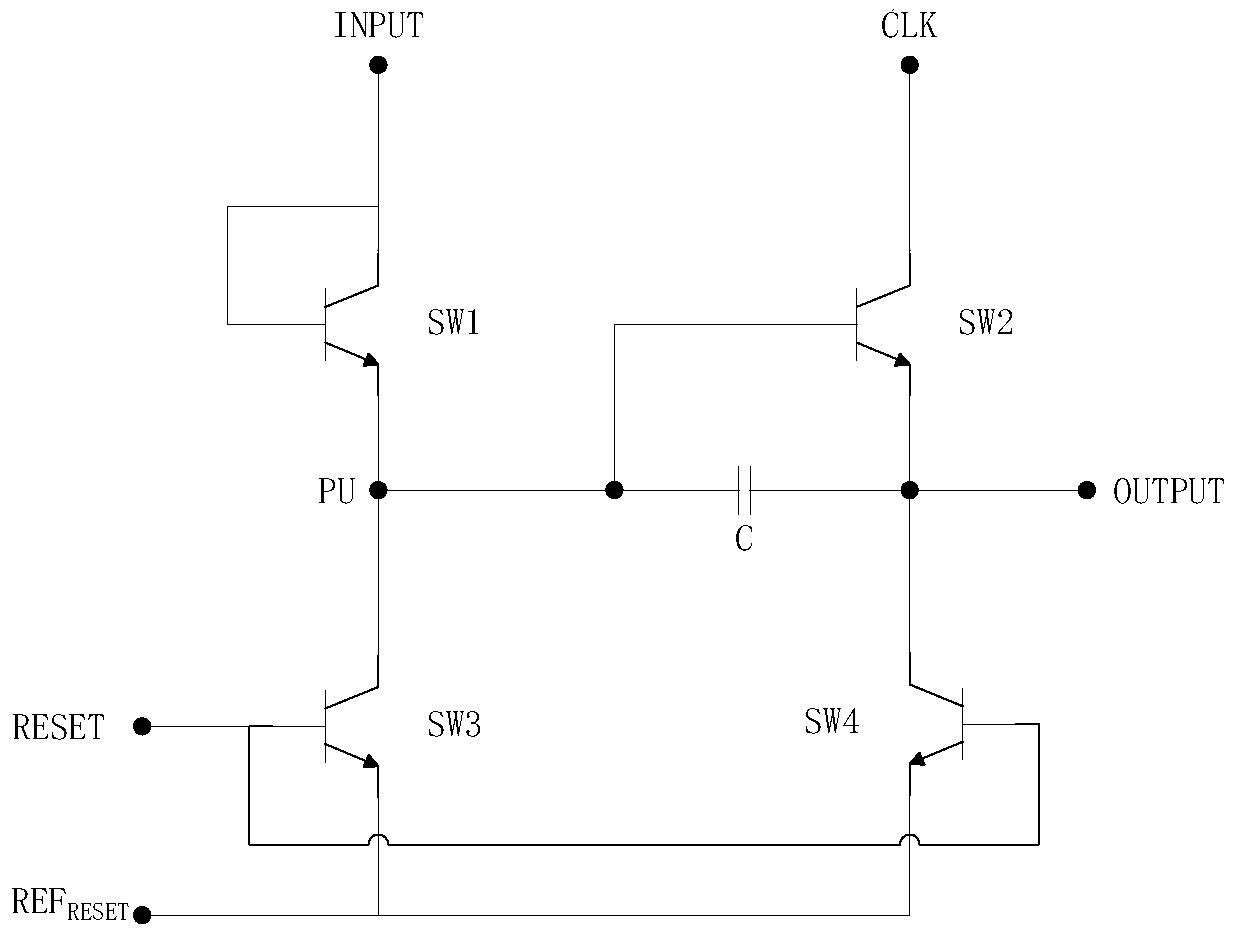

[circuit and method for enhancing motion picture quality ]

InactiveUS20050047671A1Enhancing motion picture qualityReduce dataTelevision system detailsCharacter and pattern recognitionComputer hardwareAccess control

A circuit structure and method for enhancing motion picture quality are provided. This circuit comprises a frame memory and two dual-port buffers. The memory structure can read the previous frame data and store the present frame data at the same time. Therefore, it can provide a simpler access control and structure of memory than the prior art. The circuit compresses the data by a nonlinear quantization method, which can reduce the size of the frame memory. The circuit uses alternate reading / writing and interpolation by using the adjacent pixels to further reduce the size of the frame memory.

Owner:SUNPLUS TECH CO LTD

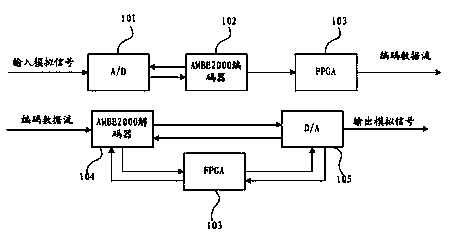

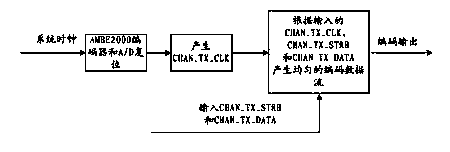

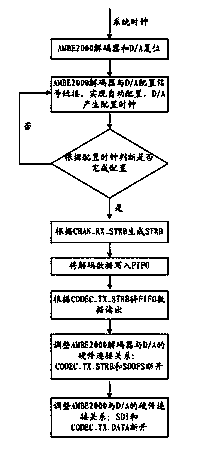

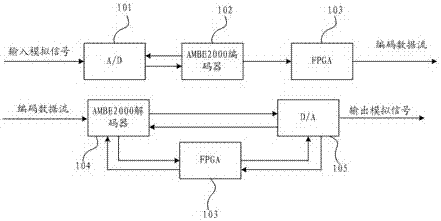

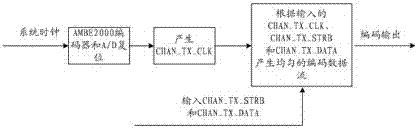

AMBE 2000 control system and control method

ActiveCN103578476ASimple timing controlSimple methodSpeech analysisDigital analog converterControl system

The invention discloses an AMBE 2000 control system. The AMBE 2000 control system comprises an analog-digital converter, an AMBE 2000 coder, an FPGA, an AMBE 2000 decoder and a digital-analog converter. In the process of decoding, the FPGA is used for achieving reuse of data pins of a chip through software programming, configuration signals are received in the process of configuration, normal decoding data (channel code streams) are received after configuration, and therefore sequential control of an AMBE 2000 is simplified greatly; meanwhile, the invention further discloses an AMBE 2000 control method used for carrying out processing on configuration clocks and data to judge whether configuration is completed or not, and therefore chip pins can be switched. The method is simple and convenient to use.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

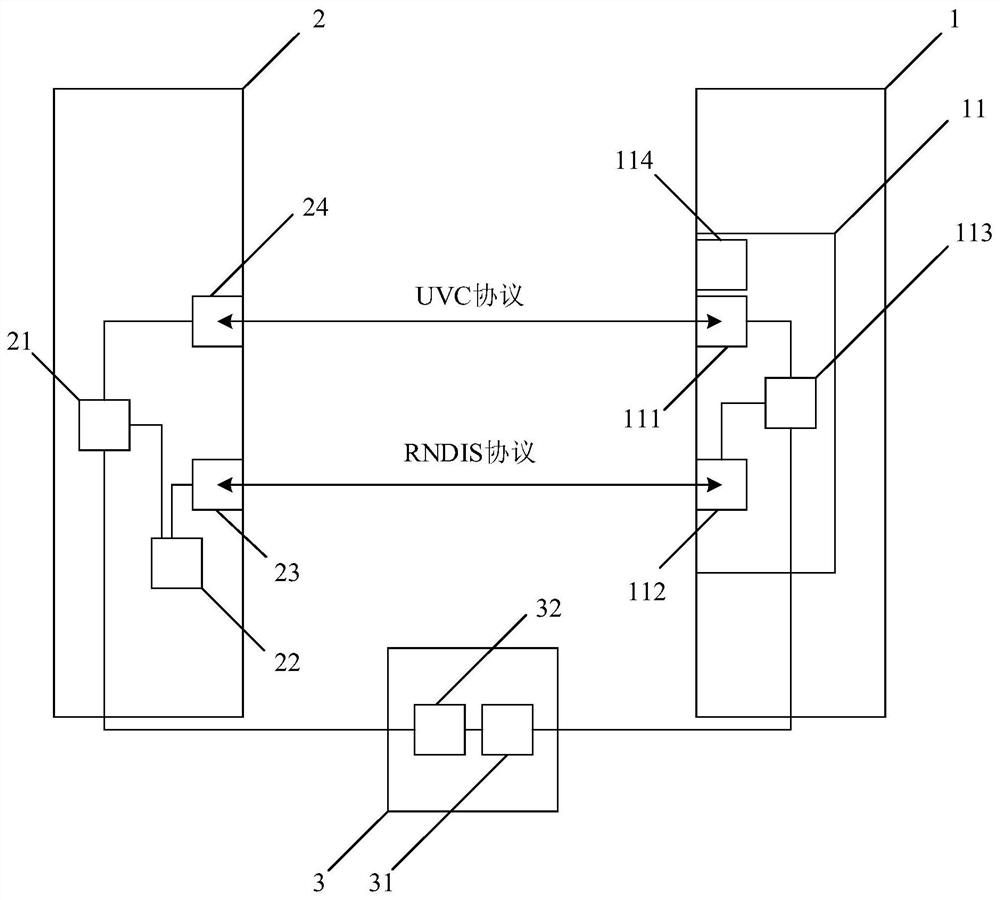

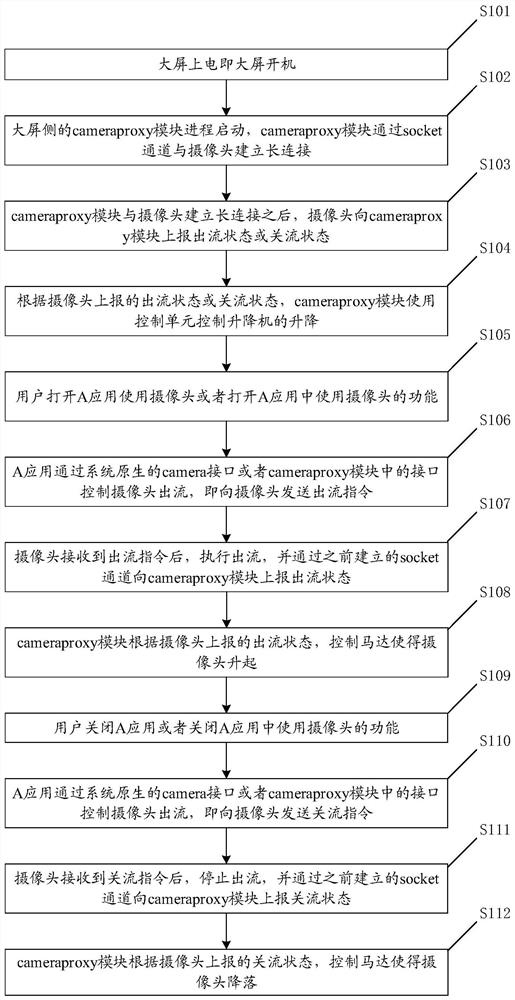

Camera control method and system and electronic equipment

PendingCN113556460AFew modulesSimple timing controlTelevision system detailsColor television detailsEmbedded systemCamera control

The embodiment of the invention discloses a camera control method and system and electronic equipment. According to the technical scheme provided by the embodiment of the invention, the lifting of the camera can be associated with the outflow state of the camera, a native interface of an operating system does not need to be called to control the lifting of a motor, and an application does not need to additionally add logic for calling the motor, so that modules called by the lifting control of the camera are fewer, and time sequence control is simpler. In addition, redundancy control logic after the camera is turned off is added, and the problem that the camera rises and falls repeatedly when multiple applications are switched and used can be avoided.

Owner:HUAWEI TECH CO LTD

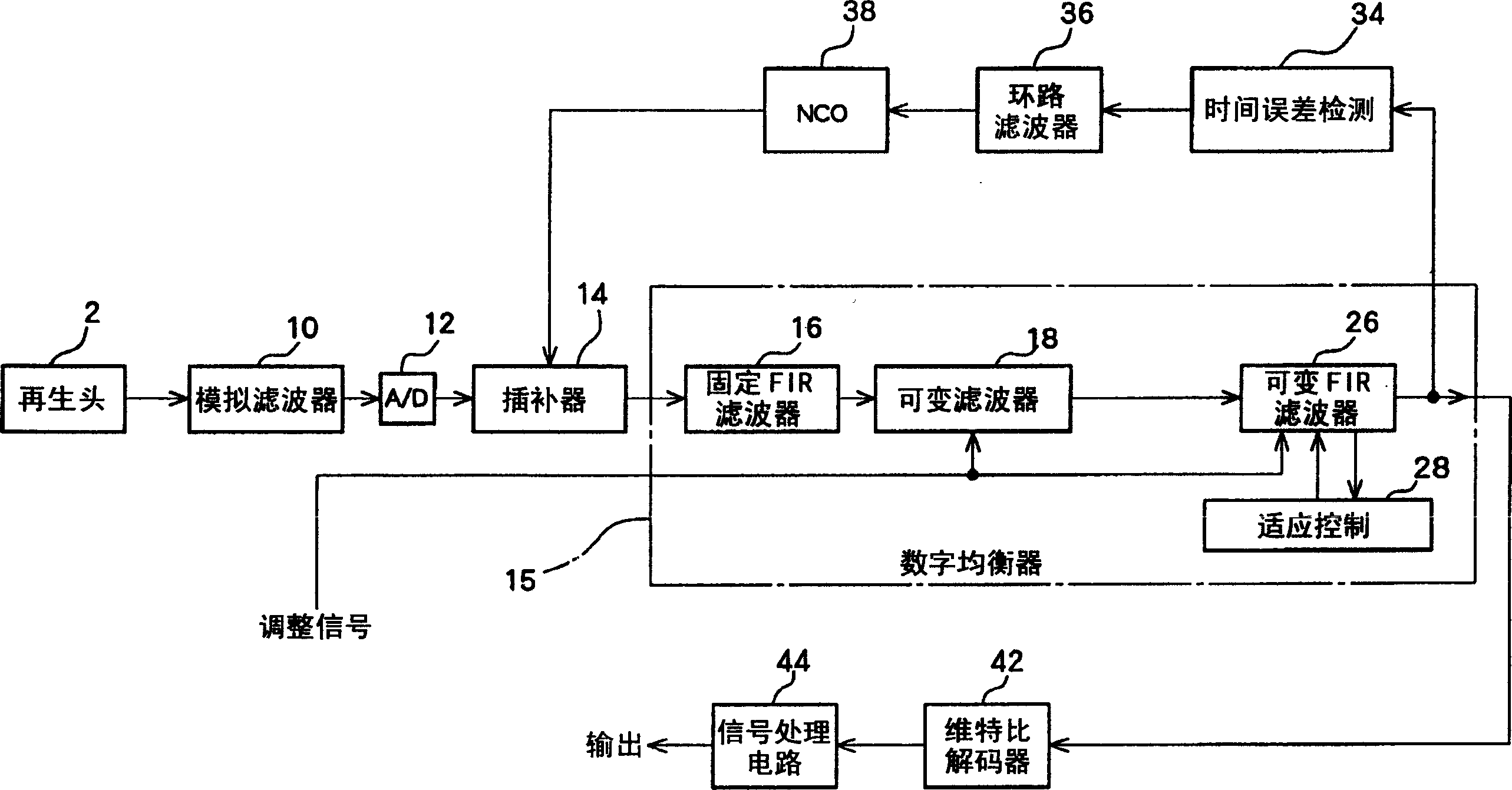

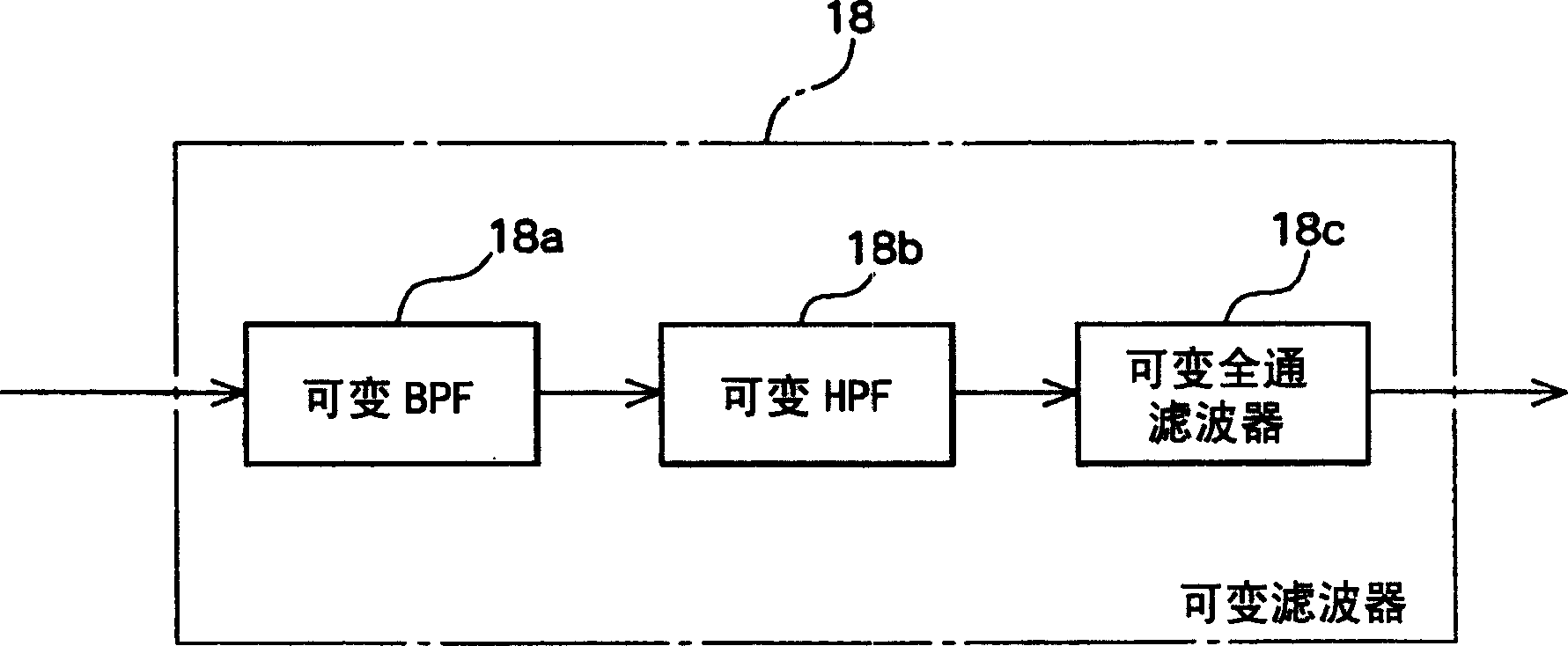

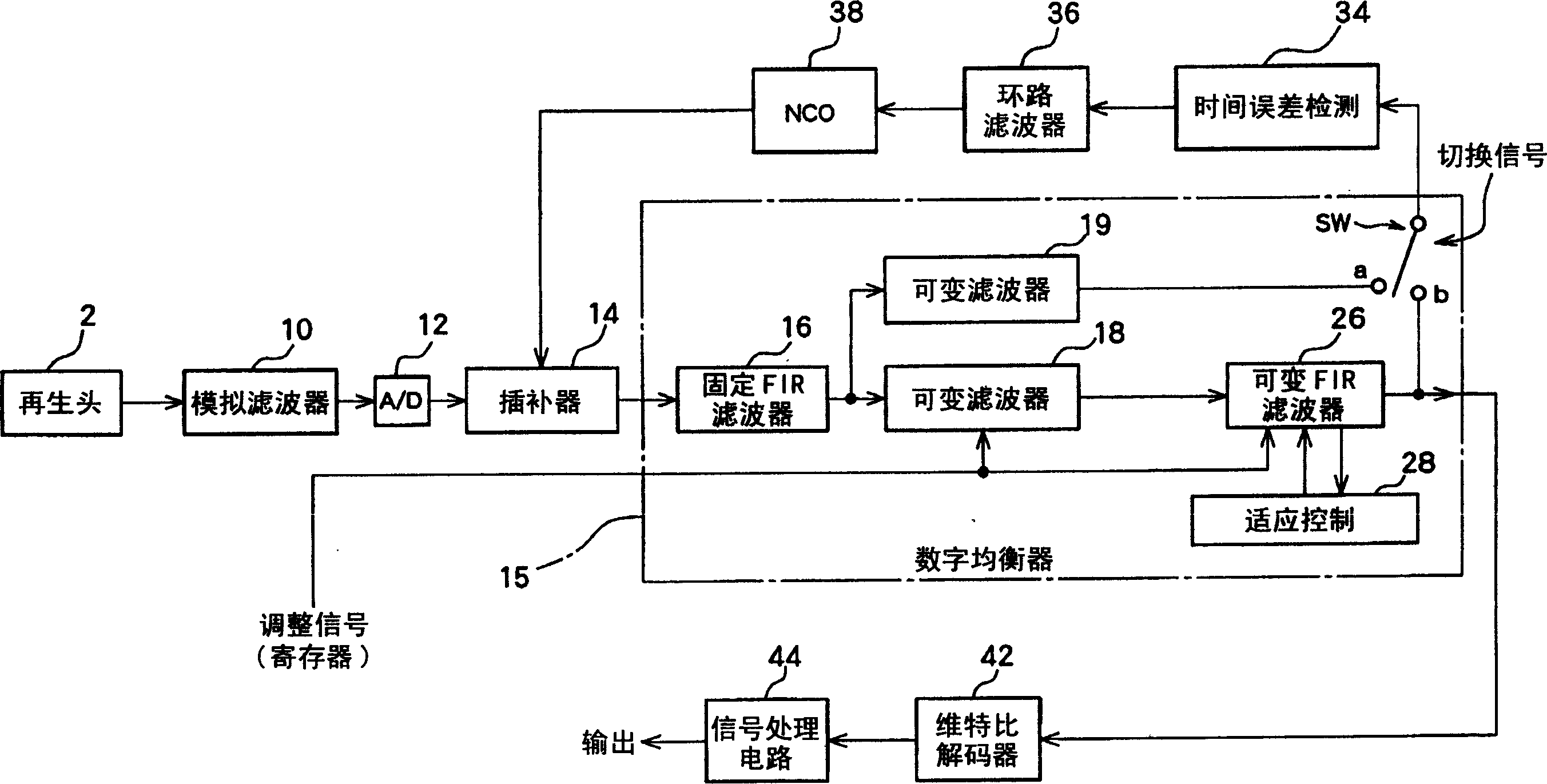

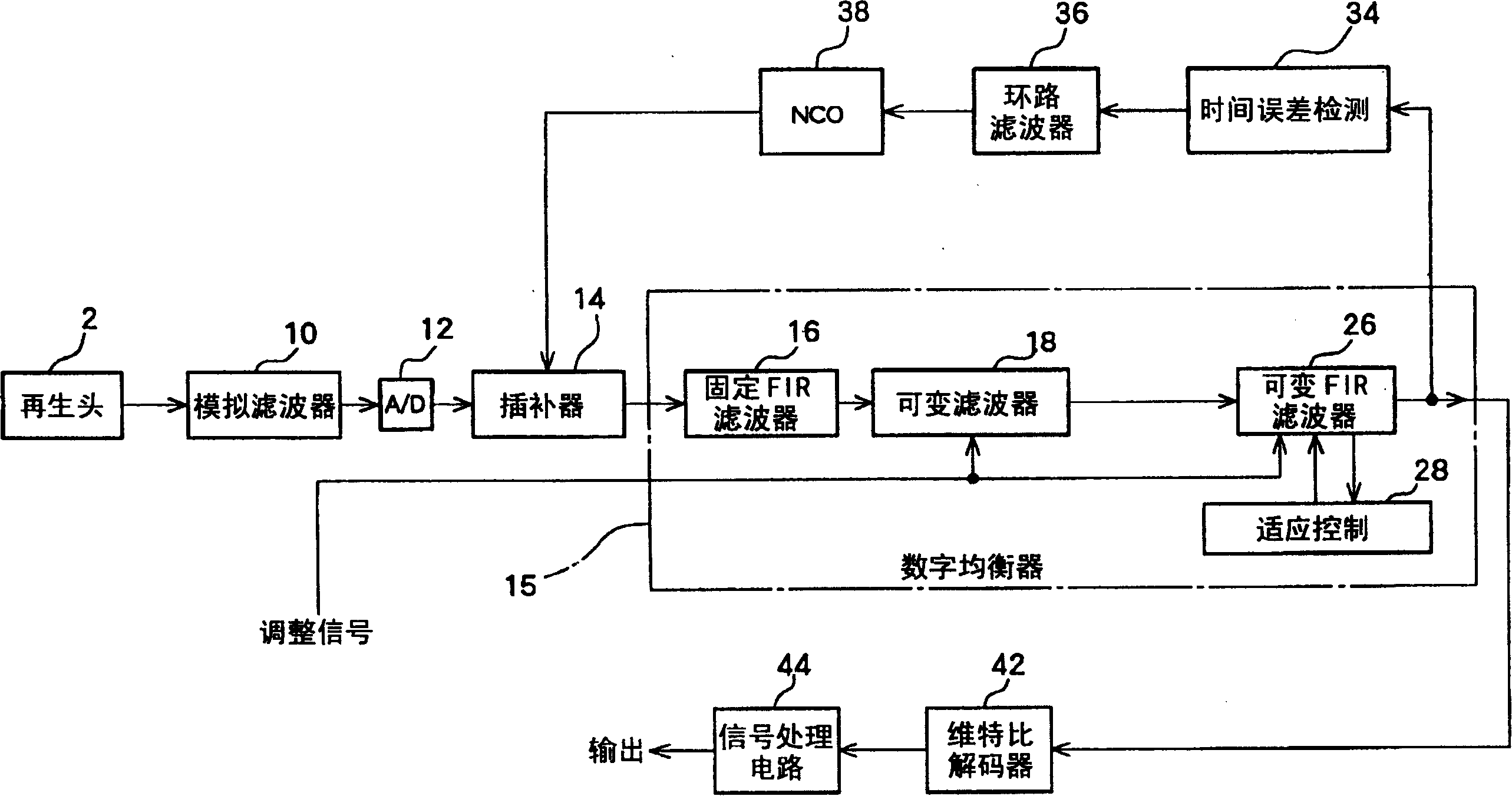

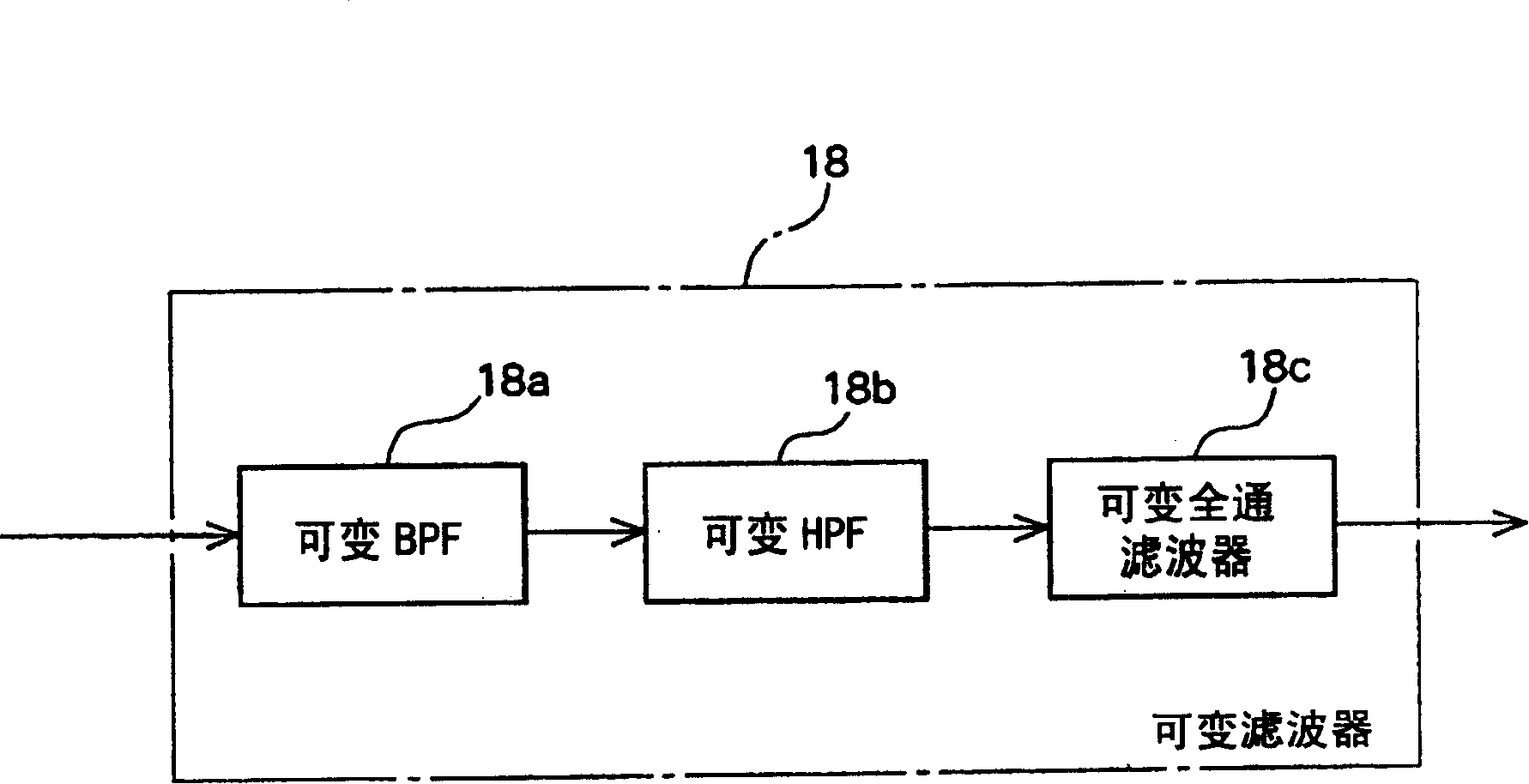

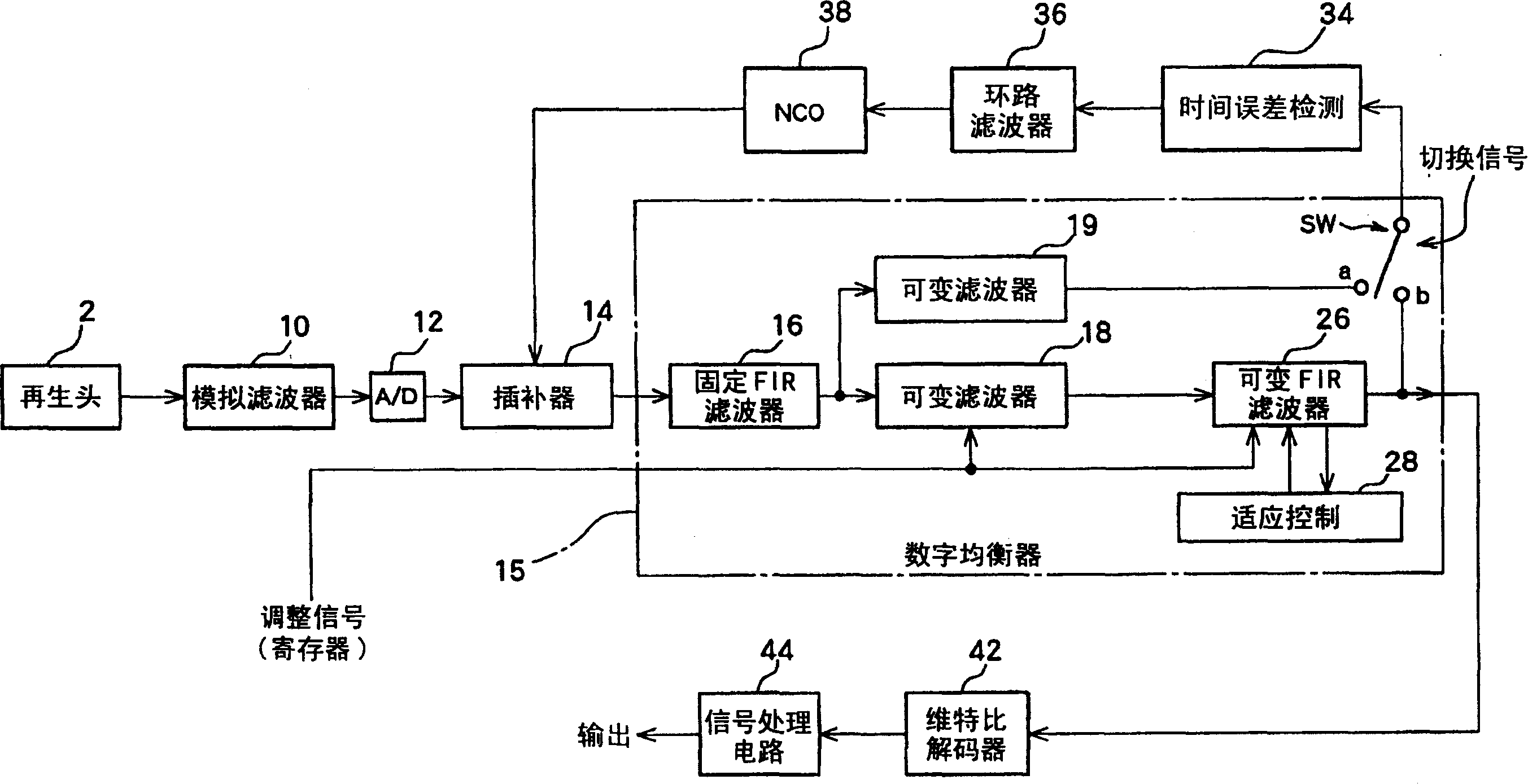

Data regeneration apparatus

InactiveCN1612212AUniform treatmentSimple timing controlModification of read/write signalsDigital technique networkDigital dataEngineering

An apparatus for generating digital data. A signal regenerated by a playback head is sequentially processed by an analog filter, A / D, and an interpolator, and is provided to a digital equalizer. The digital equalizer has a plurality of variable filters connected in parallel. While the characteristic of the first variable filter is adjusted, the interpolator performs timing control using the output of the second variable filter. After the adjustment is completed, the switch SW is switched to perform timing control of the interpolator using the output of the first variable filter. Thus, capable of varying the equalization processing characteristics of a digital signal and facilitating the timing adjustment of an interpolator at the same time.

Owner:SANYO ELECTRIC CO LTD

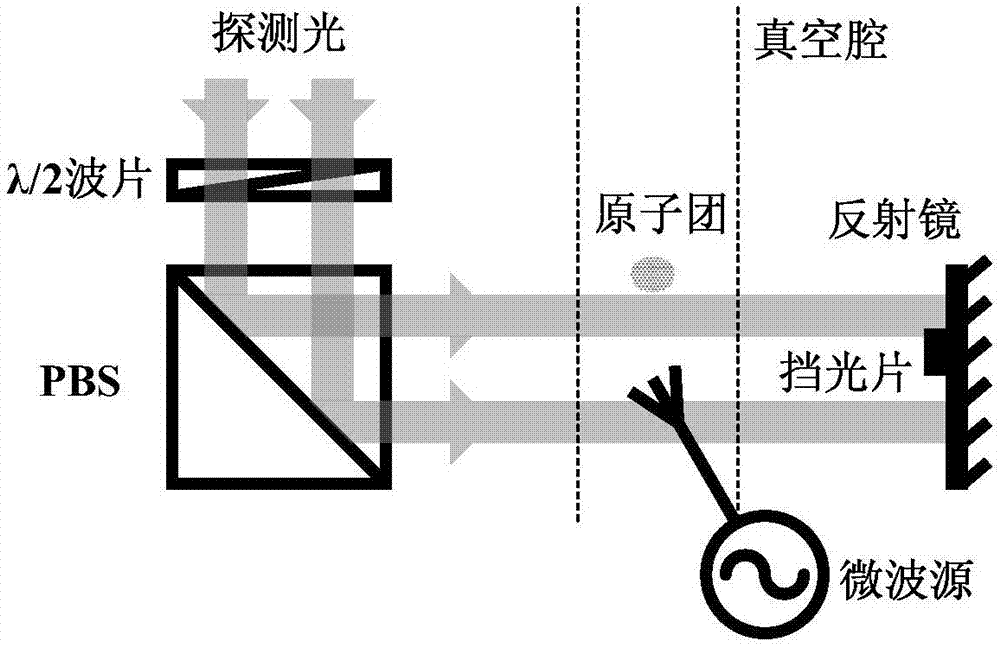

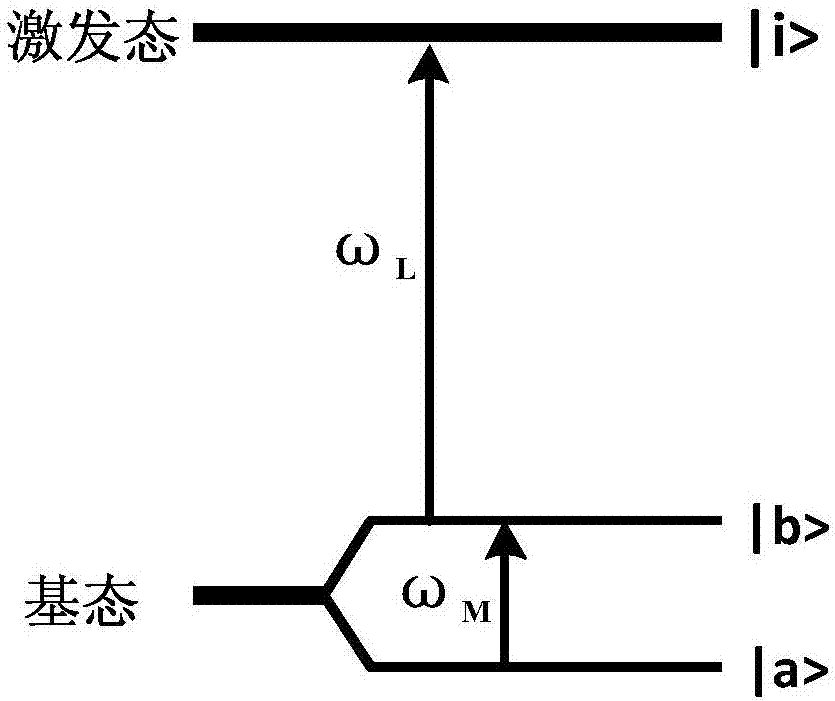

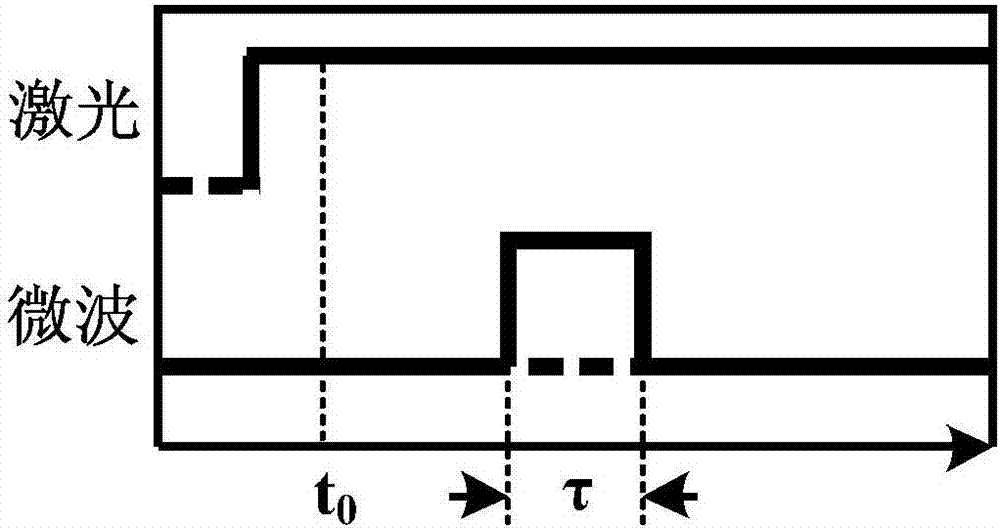

Microwave-enabled atom back pumping-based detection system and method applied to atom interferometer

PendingCN107193035ASimple structureOpen quicklyX/gamma/cosmic radiation measurmentAtomic groupLaser light

The present invention discloses a microwave-enabled atom back pumping-based detection system and method applied to an atom interferometer. The detection system comprises a laser light source, a microwave frequency source, a detection optical path, an atomic imaging device and a time sequence control module; after being interfered, falling atoms are in an a quantum state and a b quantum state, and interact with a beam of detection light which is horizontally located at an upper part in space, so as to generate fluorescent light; the number information Nb of the b-quantum state atoms is obtained through an imaging system; in a continuous falling process, the quantum-state atoms are removed from a detection region; before entering a beam of detection light which is horizontally located at a low part in space, another kind of a-quantum state atoms are back pumped to a b-quantum state through a microwave back pumping method, wherein the b-quantum state can interact with the detection light; and after remaining atomic groups pass through the lower detection light beam and generate fluorescent light, the number information Na of the a-quantum state atoms is obtained. The optical path structure of the detection system of the invention is simple and compact; the frequencies of the upper laser beam and lower laser beam are identical; the intensity of background light is constant; a microwave source can be turned on and turned off quickly; and the detection system has high practicability.

Owner:HUAZHONG UNIV OF SCI & TECH

Exposure head and image forming apparatus

A exposure head includes: a light-emitting element substrate including a first light-emitting element configured to emit light, a second light-emitting element disposed in a first direction of the first light-emitting element, a third light-emitting element, and a fourth light-emitting element disposed so as to satisfy the following relationship; Dr12:Dr23=1:m (l≠m) where, l: positive integer number, m: positive integer number, Dr12: distance between the first light-emitting element and the third light-emitting element in the direction orthogonal to the first direction, Dr23: distance between the third light-emitting element and the fourth light-emitting element in the direction orthogonal to the first direction, and an imaging optical system configured to image lights emitted from the first light-emitting element, the second light-emitting element, the third light-emitting element, and the fourth light-emitting element.

Owner:SEIKO EPSON CORP

Image capturing apparatus that controls performing of short-term and long-term exposures and corresponding read operations, and control method thereof

InactiveUS9113097B2Simple timing controlTelevision system detailsColor television detailsComputer scienceImage capture

Owner:CANON KK

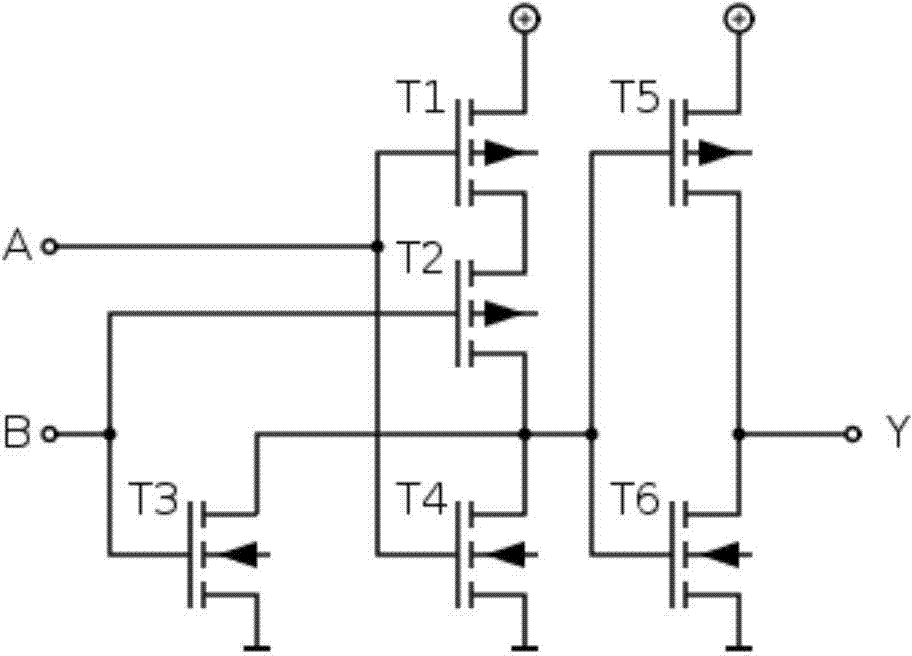

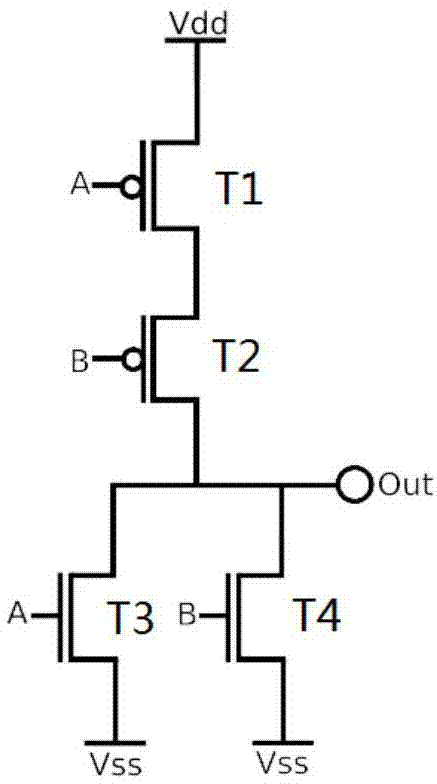

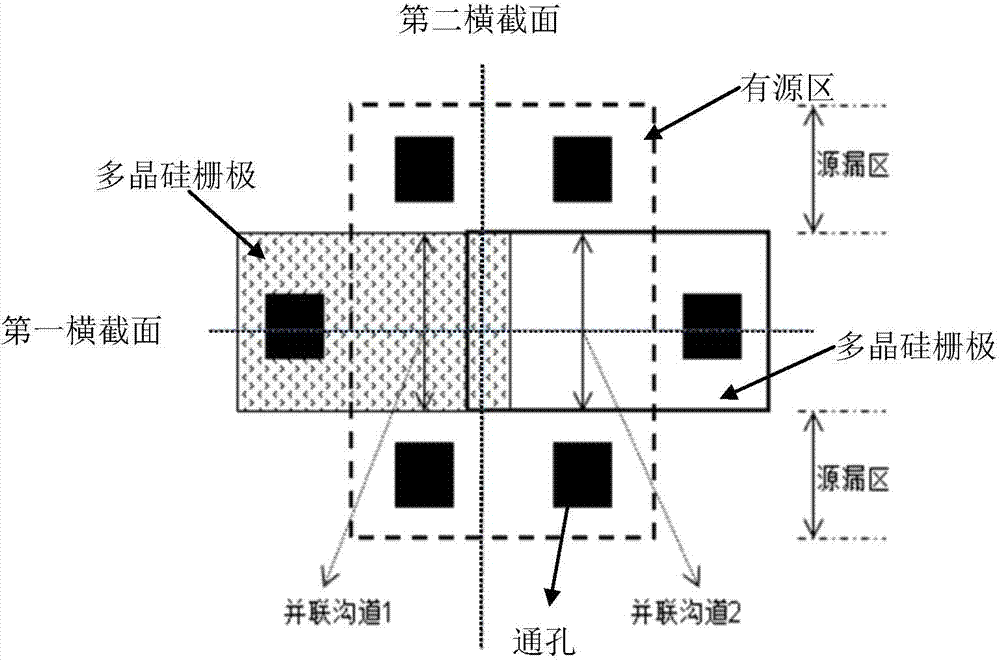

Structures and manufacturing methods of or logic and nand logic devices

InactiveCN104752418ASmall footprintReduce areaTransistorSolid-state devicesNAND logicPolycrystalline silicon

The invention discloses structures of or logic and nand logic devices. The or logic device is manufactured in a grounded p well or p type substrate, and two parallel and close door control gates are arranged on the upper side to control two adjacent and parallel n-type conductive trenches on the lower side respectively; a highly doped n type source region and drain region are arranged at the two ends of the door control gates along the direction of the boundary of the two door control gates to serve as lead-out ends of the two trenches; a polycrystalline gate is arranged on each door control gate; the two polycrystalline silicon gates are mutually electrically isolated and led out independently to serve as two input ends of or logic; the structures of the nand logic device and the or logic device are similar; the difference is that the nand logic device and the or logic device are manufactured in the n well or the n type substrate, and the source and drain regions are highly doped p type. The invention also discloses manufacturing methods of the or and nand logic devices of the structures. By designing the novel or and nand logic device structures, the devices and the circuit structures are simplified, the circuit area and the manufacturing cost are reduced, and the time sequence control of the circuit is simpler.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

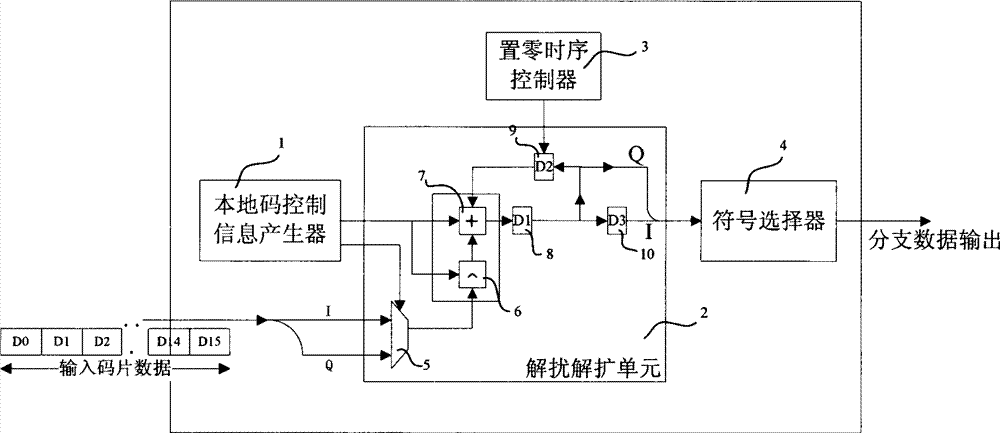

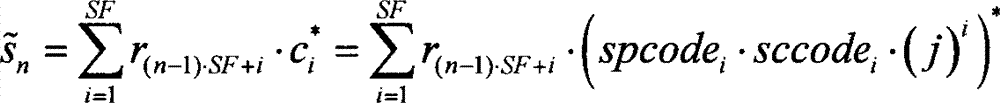

Device and method for serial descrambling and de-spreading of mobile communication system

InactiveCN101667844BSimple timing controlSave logic resourcesError preventionMultiplex code generationComputer hardwareTime schedule

The invention relates to a device and a method for serial descrambling and de-spreading of a mobile communication system. The device is characterized by comprising a local code control information generator, a descrambling and de-spreading unit, a reset time schedule controller and a symbol selector, wherein the local code control information generator generates control information with 2-time code chip rate according to scrambling codes and spreading codes; the descrambling and de-spreading unit performs descrambling and de-spreading on data according to code control information; the reset time schedule controller controls the reset of the descrambling and de-spreading unit; and the symbol selector performs symbol sampling on descrambling and de-spreading results and outputs the descrambling and de-spreading result of a branch, wherein the local code control information generator, the reset time schedule controller and the symbol selector are connected into the descrambling and de-spreading unit respectively. Thus, by using a full adder and an xor device, the multiplication of a code chip, the scrambling codes and spreading codes and the accumulation of the multiplication resultsof the code chip can be finished at the same time so as to implement the process of descrambling and de-spreading, and the device and the method are suitable for achieving an integrated circuit in the mobile communication system.

Owner:MEDIATEK INC

A pipelined analog-to-digital converter and its capacitance mismatch error calibration method

ActiveCN104363019BReduce addReduce difficultyAnalogue/digital conversion calibration/testingCapacitanceDigital down converter

The embodiment of the present invention discloses a simple calibration scheme for the capacitance mismatch error of the pipeline analog-to-digital converter. On the basis of the traditional non-calibration pipeline analog-to-digital converter structure, it consists of a stage MDAC structure and a stage calibration switch structure that needs to be calibrated The calibration stage of the capacitance mismatch error, meanwhile, increases the digital calibration circuit of the capacitance mismatch error. During the calibration stage capacitance error extraction work, two specific inputs are given to the calibration stage sampling capacitor through the stage calibration switch structure, and two digital codes containing capacitance mismatch errors are obtained, and then the calibration stage capacitance mismatch error is extracted based on them And perform digital calibration. The capacitance mismatch error calibration solution has an extremely simple structure, extremely few additional components, and extremely simple timing control, and can effectively calibrate the problem of static characteristic degradation caused by capacitance mismatch.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

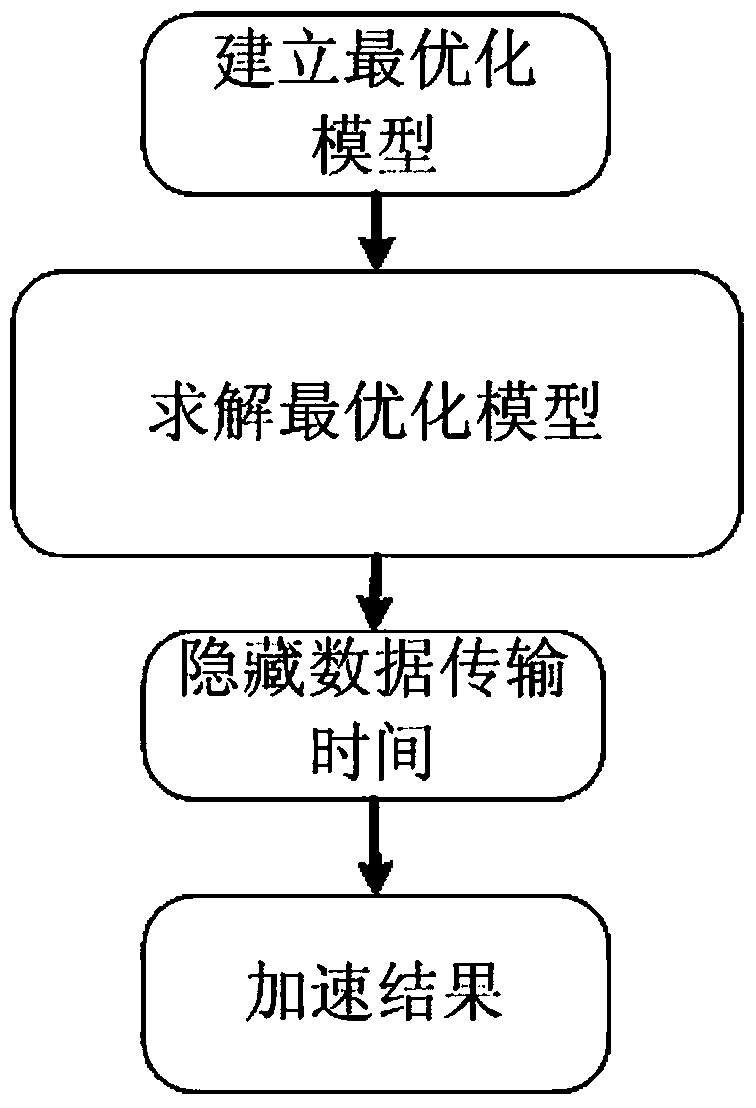

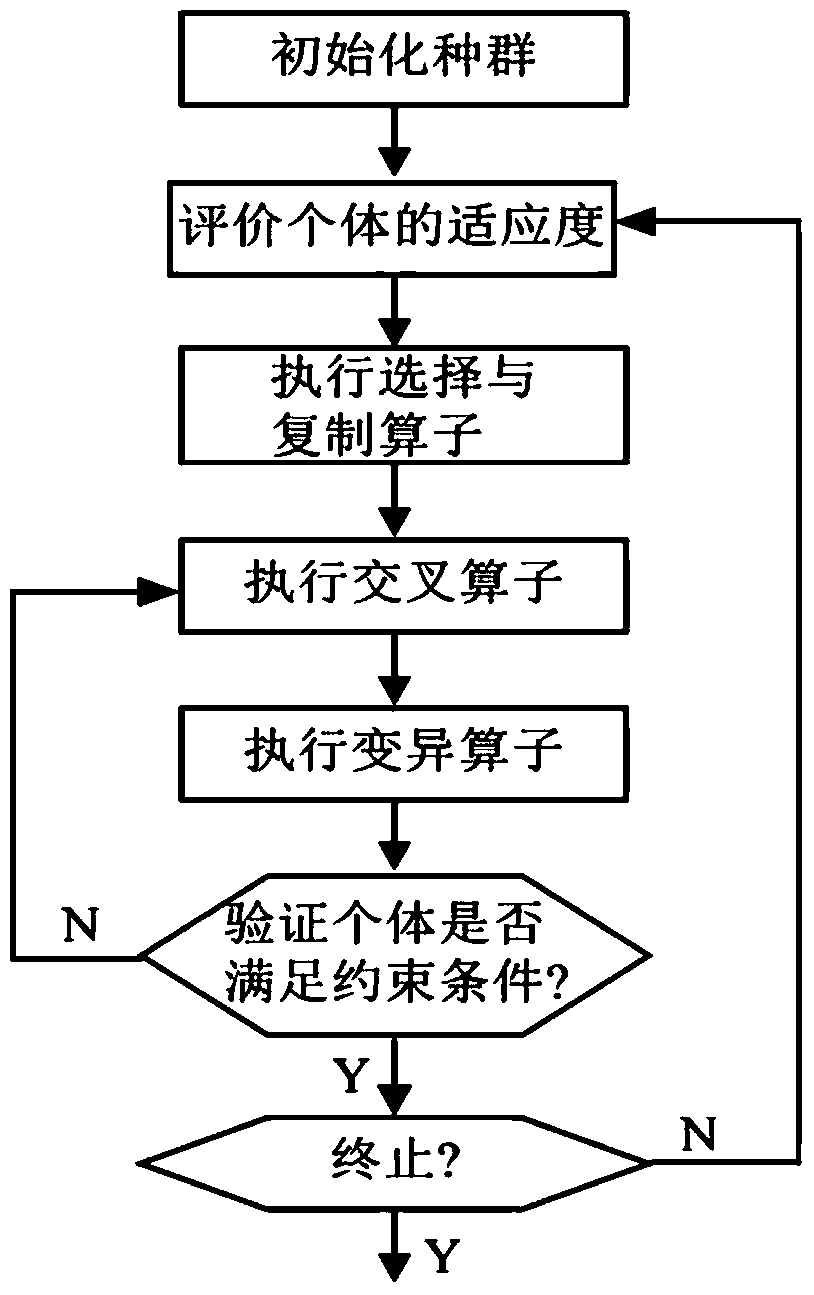

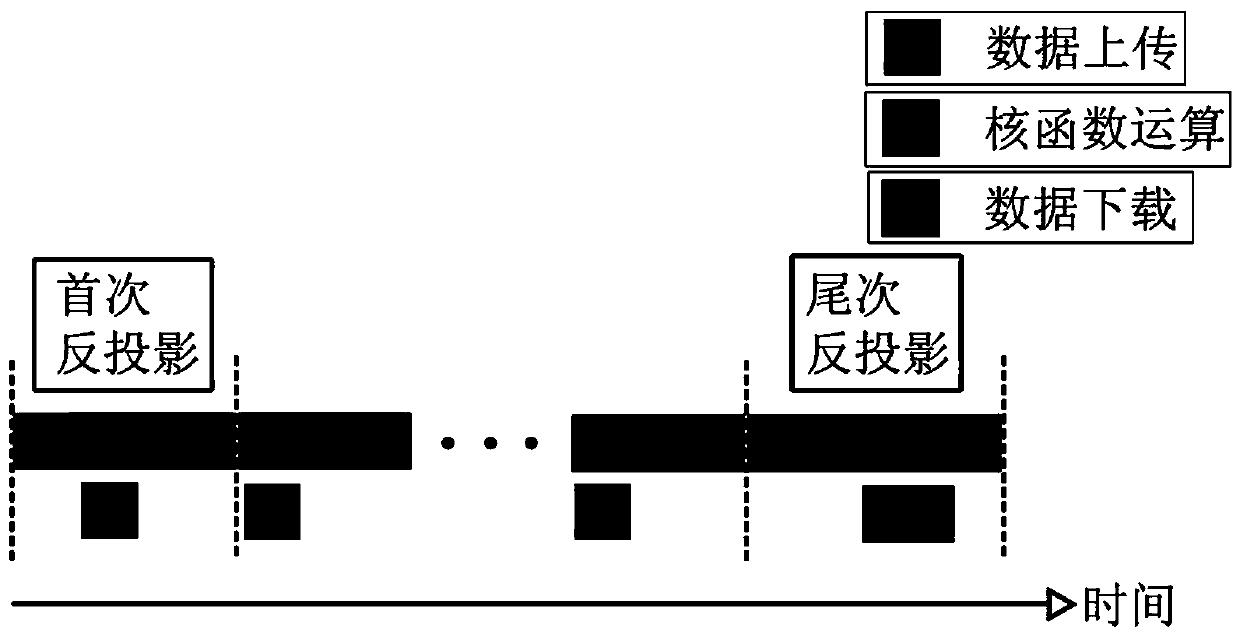

Acceleration Method of Back Projection for CT Image Reconstruction Based on Genetic Algorithm

ActiveCN105374006BHigh degree of adaptabilityThe proportion of calculation consumption is lowGenetic modelsImage memory managementAlgorithmReconstruction method

Owner:THE PLA INFORMATION ENG UNIV

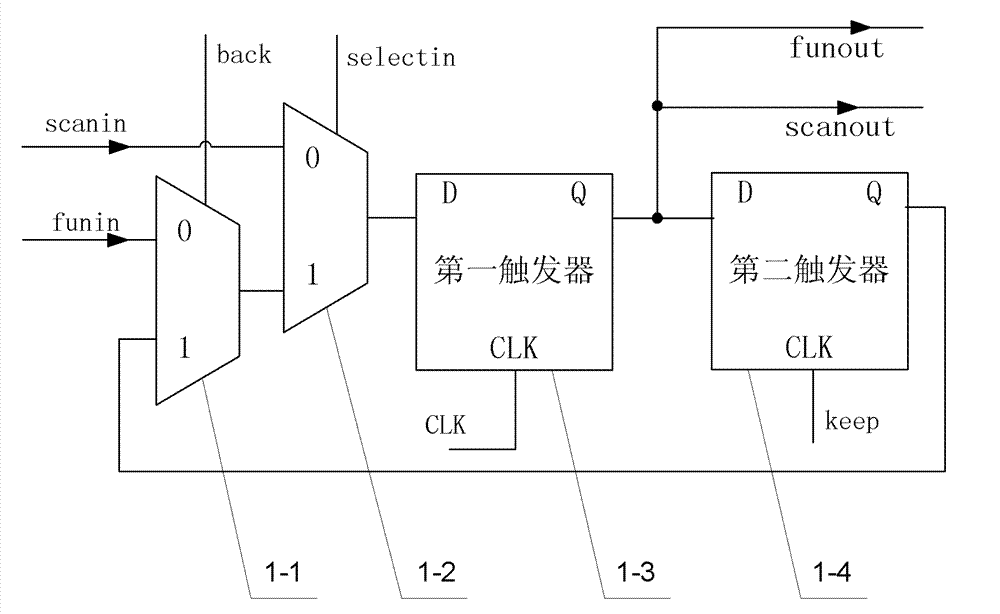

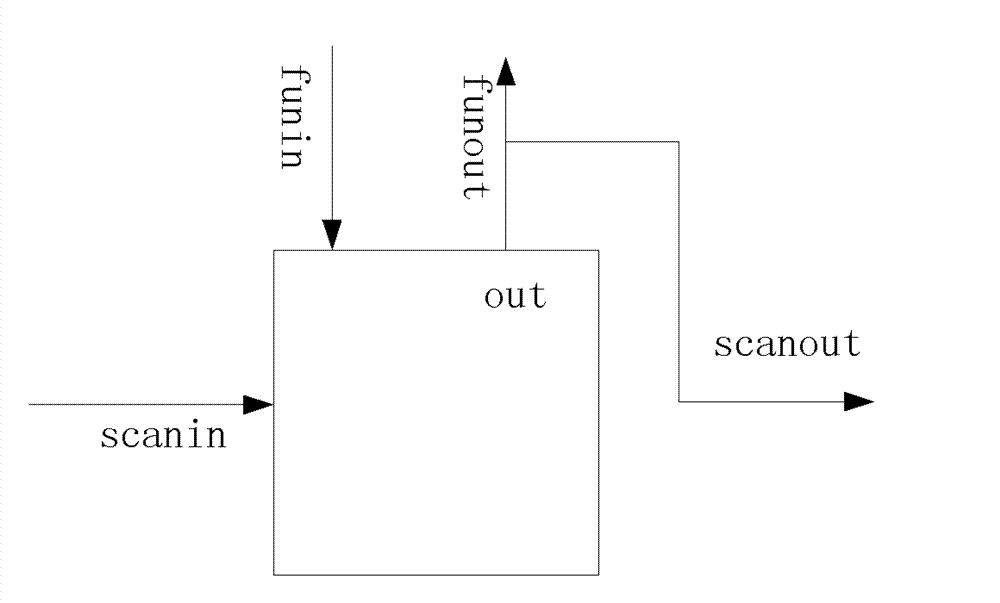

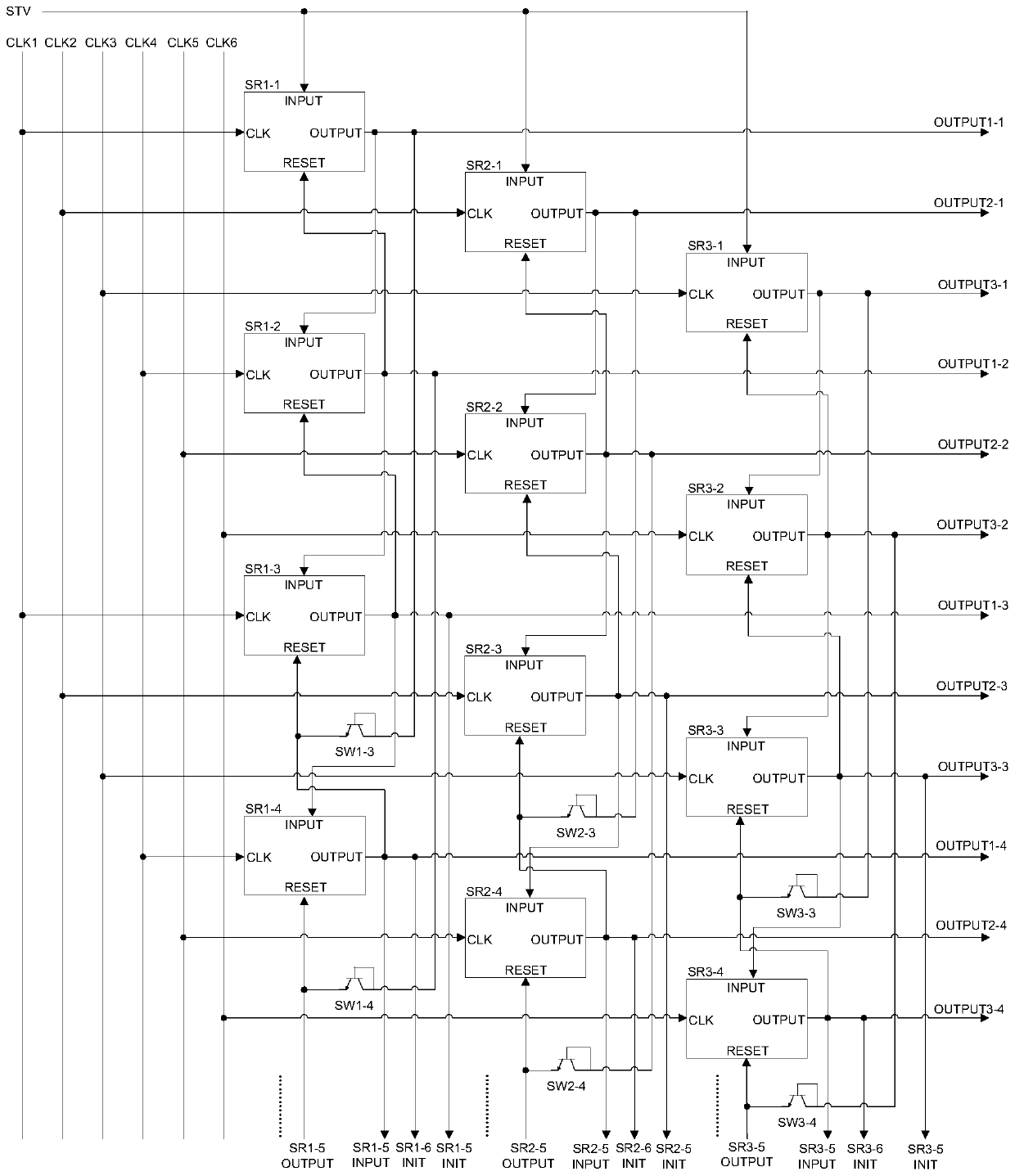

Improved scan chain unit and non-concurrent testing method based on same

InactiveCN102043122BSimple timing controlImprove test efficiencyDigital circuit testingMultiplexerOnline test

The invention relates to an improved scan chain unit and a non-concurrent testing method based on the same, which belongs to the filed of on-chip system testing and aims at solving the problems that the existing scan chain-based non-concurrent on-line testing method has strict requirements for time sequences, is difficult to control and can not realize the one-step import of multiple groups of test vectors. The improved scan chain unit is used for replacing a D trigger in an on-chip system, and the unit contains two triggers and two selectors, wherein a first trigger is a basic unit which composes the original circuit scan chain and is used for realizing the function same with that of the original D trigger, and a second trigger is introduced for saving data in the testing process; and the two data selectors control the flow direction of data by means of enable ends, a first selector is used for controlling whether data in the second trigger can be transmitted to the first trigger, and a second selector is used for controlling the working state or the scanning state of the first trigger. Thus, multiple groups of test vectors can be input to the unit for continuous testing, and therunning state of the circuit is not changed before and after the test.

Owner:HARBIN INST OF TECH

A test circuit and method for testing the on-off characteristics of a converter valve

ActiveCN111562494BThe cycle runs continuouslySimple timing controlCircuit interrupters testingHemt circuitsTest platform

The invention discloses a test circuit and a method for testing the on-off characteristics of a converter valve. In the test circuit, the positive pole of the DC power supply in the energy supplement circuit is connected to the anode of the first thyristor; one end of the recovery valve in the recovery circuit is respectively connected to the One end of the inductor is connected to the cathode of the first thyristor, and the other end of the recovery valve is connected to the negative pole of the DC power supply; one end of the H bridge circuit in the output circuit is connected to the other end of the inductor, and the other end of the H bridge circuit is connected to the negative pole of the DC power supply. The circuit includes: a first sub-module including a first capacitor and a first switch component and a second sub-module including a second capacitor and a second switch component, the capacitance of the first capacitor and the second capacitor are different; the load circuit includes a The valve test object, the valve test object to be tested is connected to the two ends of the H-bridge circuit. Through the implementation of the invention, a test platform capable of periodic operation and whose turn-on voltage is different from the turn-off voltage can be built, so that the turn-on and turn-off characteristics of valves and the electrical performance of internal components can be tested in a targeted manner.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

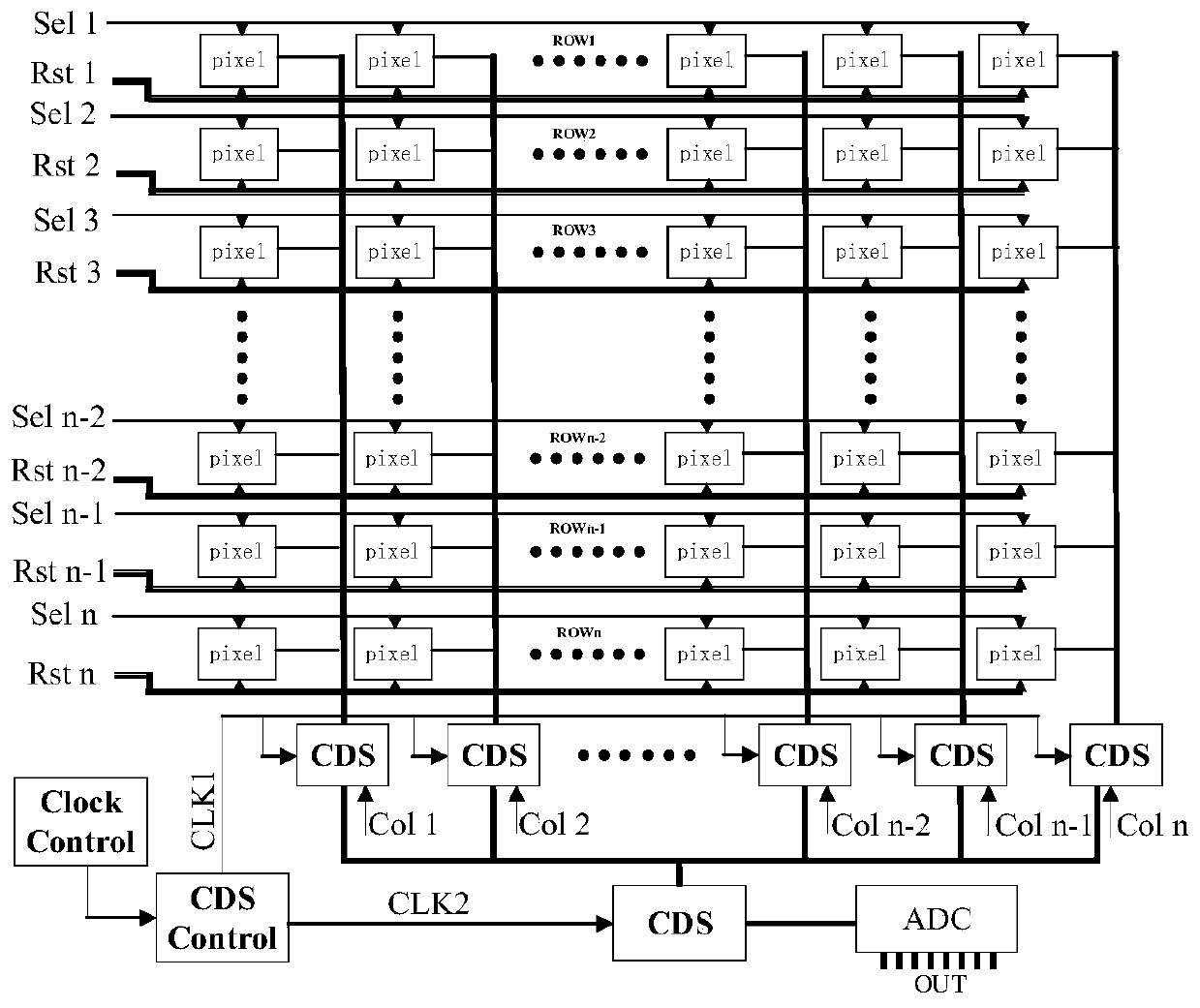

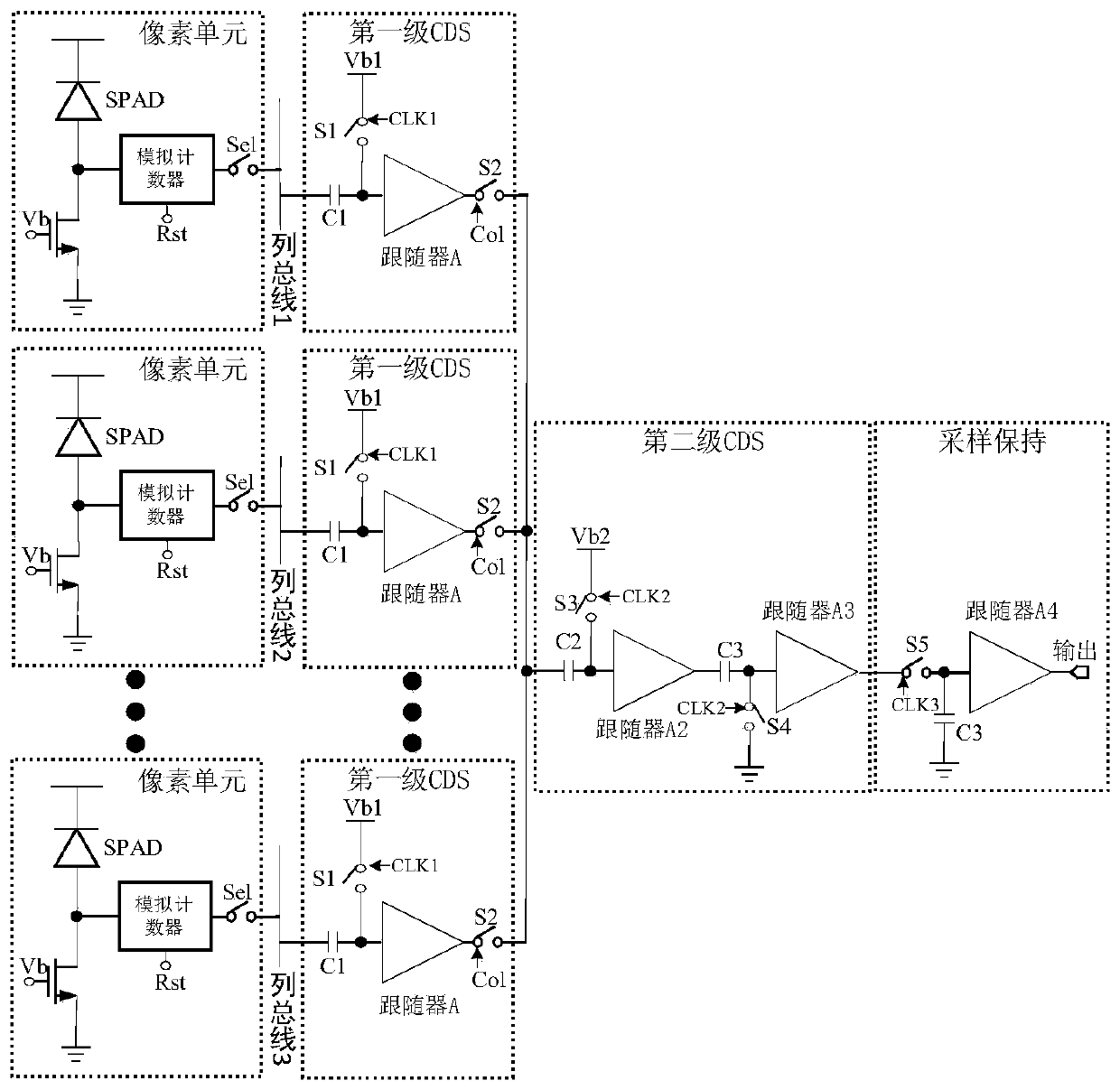

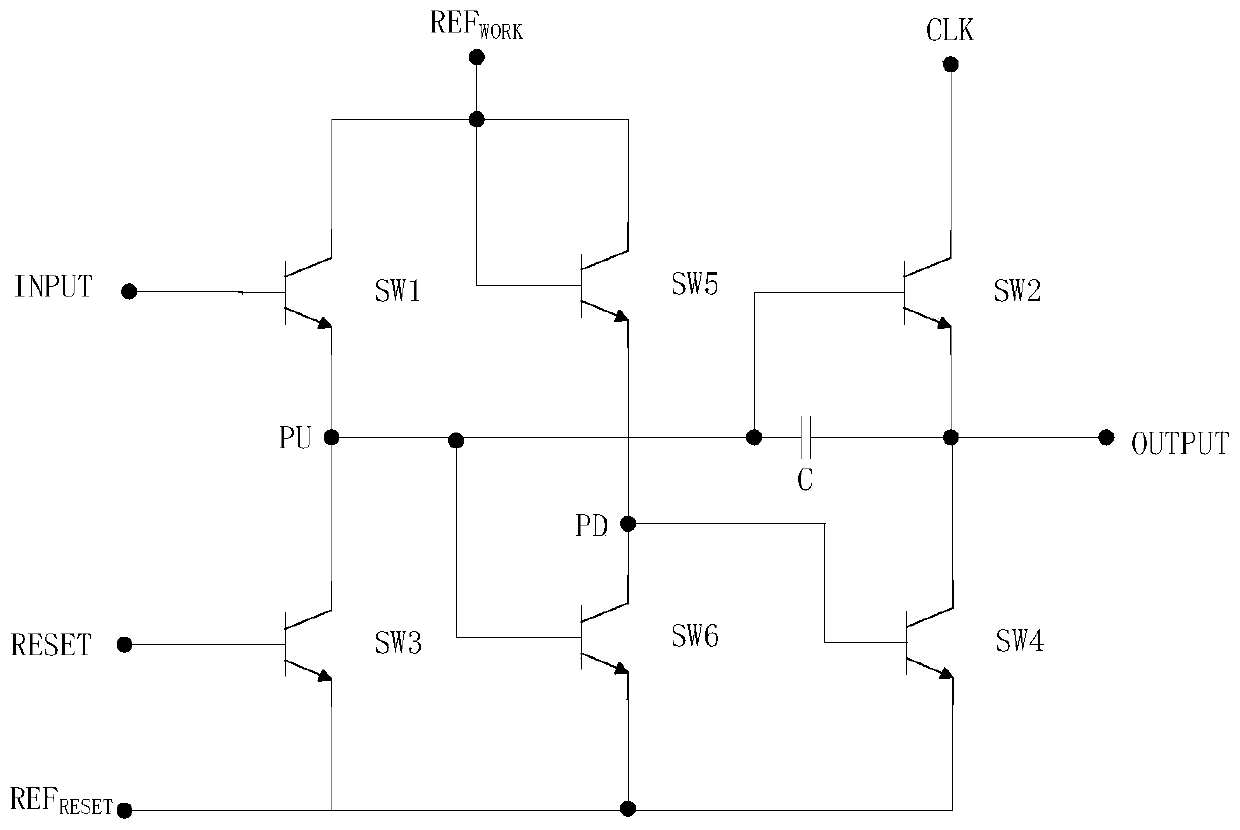

A Spad Array Level Readout Circuit Using Quadratic Correlation Double Sampling Technology

ActiveCN108391071BImprove compatibilitySimple structureTelevision system detailsColor television detailsCapacitanceControl signal

The invention discloses a SPAD array-level readout circuit adopting quadratic correlation double-sampling technology, which includes a CDS readout circuit and a sample-and-hold circuit. The first-stage CDS readout circuit consists of a voltage follower, two switch circuits and a sampling capacitor, which are connected to each column bus to ensure fast readout of the information of the pixel unit, and the information in the pixel unit Fixed pattern noise cancellation. The second-stage CDS readout circuit consists of 2 voltage followers, 2 switch circuits and 2 sampling capacitors, which are used to eliminate fixed pattern noise in the readout circuit. The quadratic correlation double-sampling array-level readout circuit only needs two control signals, and the timing signal is simple. The invention has the advantages of simple timing control and fast readout speed. The two-stage CDS only needs two control signals, and the readout speed is fast, which improves the working efficiency of the readout circuit. Therefore, it has obvious advantages in large-scale pixel array circuits.

Owner:NANJING UNIV OF POSTS & TELECOMM +1

A method and device for measuring the geometric dimension of a gap in a free-form surface

ActiveCN106705847BReduce demandEasy to operateImage analysisGeometric image transformationFree formComputer science

The invention discloses a geometric size measuring method and a device for a slit inside free-form surface. The geometric size measuring method for the slit inside free-form surface comprises the steps of acquiring a slit image: conducting the segmented acquisition of the slit image of a to-be-measured free-form surface product; processing the slit image: processing each segment of the acquired slit image so as to obtain a slit cross-sectional profile, and positioning the edge feature points of each segment of the slit profile, the inflection point of the slit profile, the highest point of the slit profile and the lowest point of the slit profile; conducting the registering and splicing operation: registering and splicing all segments of the processed slit profile; conducting the segmented fitting operation: conducting the segmented fitting for the feature points of the slit profile after the registering and splicing operation so as to obtain an overall slit profile containing the lowest-point curve, the edge curve and the highest-point curve of a slit; and acquiring the geometric size of the slit: according to the fitted curve, acquiring the depth, the length and the width of the slit.

Owner:CHONGQING ACAD OF METROLOGY & QUALITY INST

Data regeneration apparatus

InactiveCN1294557CUniform treatmentSimple timing controlModification of read/write signalsDigital technique networkDigital dataEqualization

An apparatus for generating digital data. A signal regenerated by a playback head is sequentially processed by an analog filter, A / D, and an interpolator, and is provided to a digital equalizer. The digital equalizer has a plurality of variable filters connected in parallel. While the characteristic of the first variable filter is adjusted, the interpolator performs timing control using the output of the second variable filter. After the adjustment is completed, the switch SW is switched to perform timing control of the interpolator using the output of the first variable filter. Thus, capable of varying the equalization processing characteristics of a digital signal and facilitating the timing adjustment of an interpolator at the same time.

Owner:SANYO ELECTRIC CO LTD

ambe2000 control system and control method

The invention discloses an AMBE2000 control system, comprising an analog / digital converter, an AMBE2000 encoder, an FPGA, an AMBE2000 decoder, and a digital / analog converter; Multiplexing, receiving configuration signals during configuration, and receiving normal decoded data (channel code stream) after configuration, thus greatly simplifying the timing control of AMBE2000; at the same time, the invention also discloses a control method of AMBE2000, which controls the configuration clock and The data is processed to determine whether the configuration is completed, so as to switch the chip pins. This method is simple and convenient.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

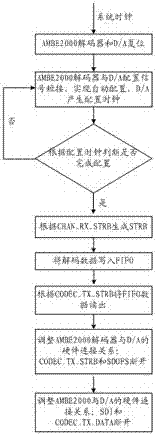

Array substrate gate driving circuit, driving method thereof, and display device

InactiveCN106935179BLow costSimple timing controlStatic indicating devicesDigital storageShift registerDriver circuit

Provided are an array substrate gate driving circuit, a driving method thereof, and a display device. The array substrate gate drive circuit includes at least one shift register group, each shift register group includes a plurality of shift registers cascaded together, the plurality of shift registers include a first shift register, and the connection position is at a second shift register after the first shift register and a third shift register connected after the second shift register, wherein the third shift register is provided with an initialization terminal, and the The initialization terminal is connected to the output terminal of the first shift register.

Owner:BOE TECH GRP CO LTD +1

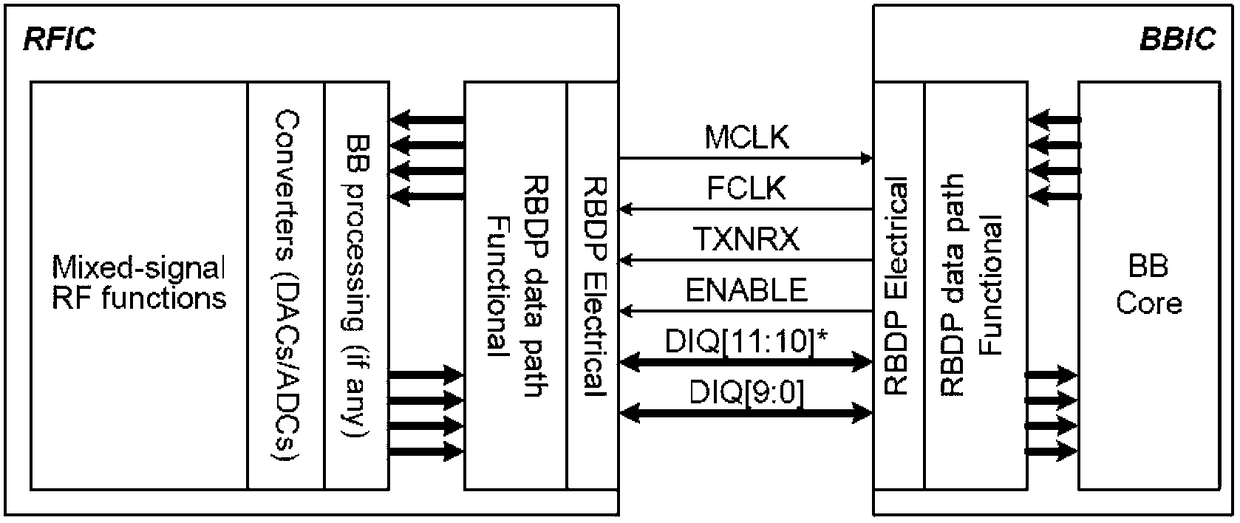

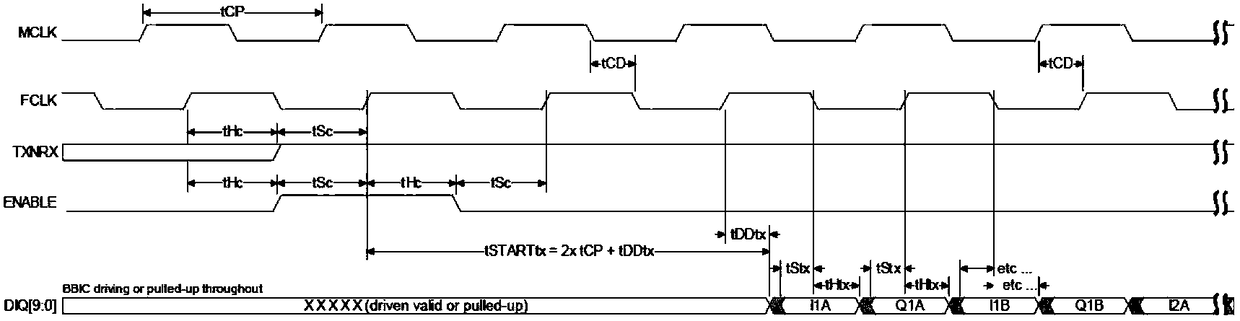

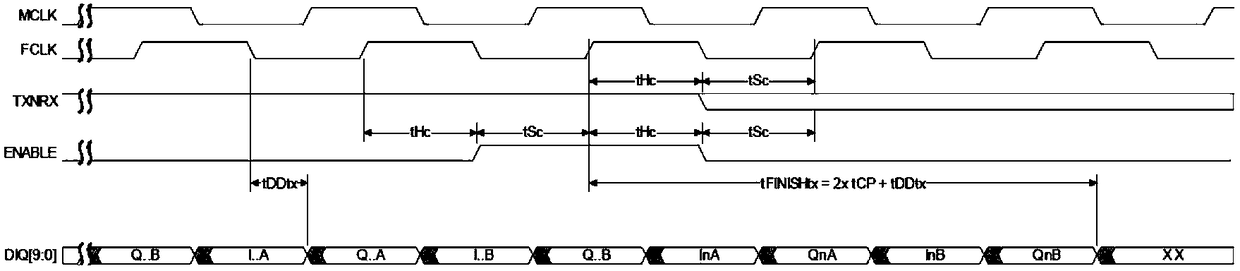

Parallel Interface Timing Control Device

The invention discloses a parallel interface sequential control device which is positioned at an analog baseband or digital baseband. The device comprises the following modules: a control module used for receiving control information from a system and status indication information from an opposite-end baseband and generating a control sequence and a status indication signal according to the control information and the status indication information, wherein the control sequence can control a channel multiplexing module to send data and control a channel demultiplexing module to receive data and the status indication signal indicates the data sending / receiving status; the channel multiplexing module used for sending first data through a two-channel to the opposite-end baseband according to the control sequence when the status indication signal indicates the sending status; and the channel demultiplexing module used for receiving second data from the opposite-end baseband through the two-channel according to the control sequence when the status indication signal indicates the receiving status. According to the invention, interface sequential control complexity is simplified, and power consumption is minimized.

Owner:SANECHIPS TECH CO LTD

![[circuit and method for enhancing motion picture quality ] [circuit and method for enhancing motion picture quality ]](https://images-eureka.patsnap.com/patent_img/bc895e02-5f14-4c79-9145-87b5ae7eb0d8/US20050047671A1-20050303-D00000.png)

![[circuit and method for enhancing motion picture quality ] [circuit and method for enhancing motion picture quality ]](https://images-eureka.patsnap.com/patent_img/bc895e02-5f14-4c79-9145-87b5ae7eb0d8/US20050047671A1-20050303-D00001.png)

![[circuit and method for enhancing motion picture quality ] [circuit and method for enhancing motion picture quality ]](https://images-eureka.patsnap.com/patent_img/bc895e02-5f14-4c79-9145-87b5ae7eb0d8/US20050047671A1-20050303-D00002.png)