Parallel Interface Timing Control Device

A timing control and interface technology, applied in the field of communication, can solve problems such as complex interface control, complex timing control, and slow switching time, and achieve the effects of reducing physical pin resources, simplifying interface timing control, and reducing packaging area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] Hereinafter, the present invention will be described in detail with reference to the drawings and in conjunction with the embodiments. It should be noted that the embodiments in the application and the features in the embodiments can be combined with each other if there is no conflict.

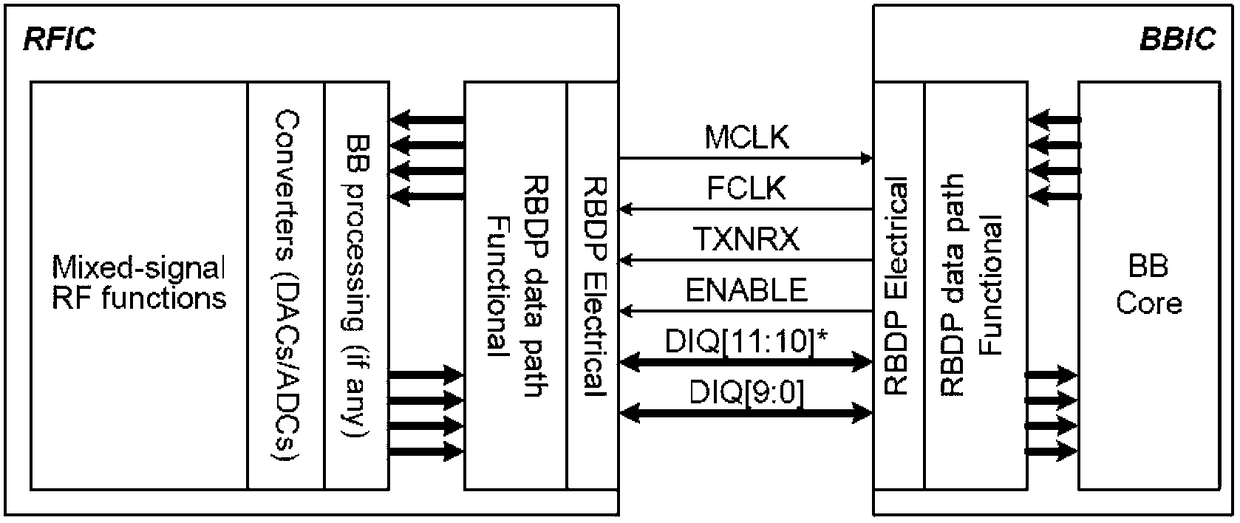

[0037] Figure 4 It is a structural block diagram of a parallel interface timing control device according to an embodiment of the present invention, such as Figure 4 As shown, the device mainly includes:

[0038] The parallel interface timing control device provided by the present invention is located in an analog baseband (ABB) or a digital baseband (DBB), and mainly includes a control module 10, a channel multiplexing module 20, and a channel demultiplexing module 30. Among them, the control module 10 is used to receive control information from the system and status indication information from the peer baseband, and generate control sequence and status indication signals according to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More