A Spad Array Level Readout Circuit Using Quadratic Correlation Double Sampling Technology

A correlated double sampling and readout circuit technology, which is applied to TV, electrical components, color TV, etc., can solve the problems of complex timing signals, ineffective operation, large integral capacitance, etc., to improve work efficiency, reduce production costs, read fast effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described in detail below with reference to the accompanying drawings.

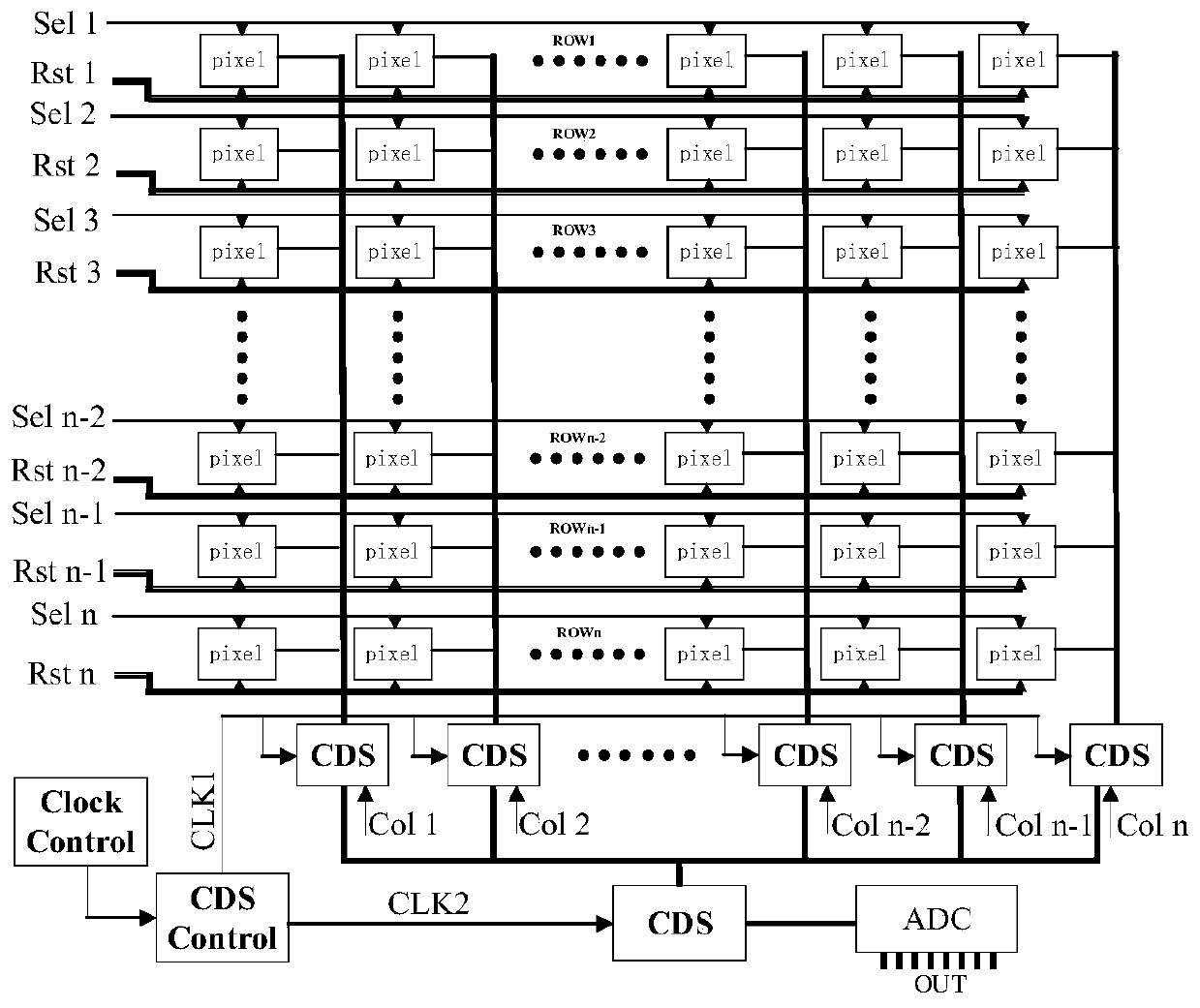

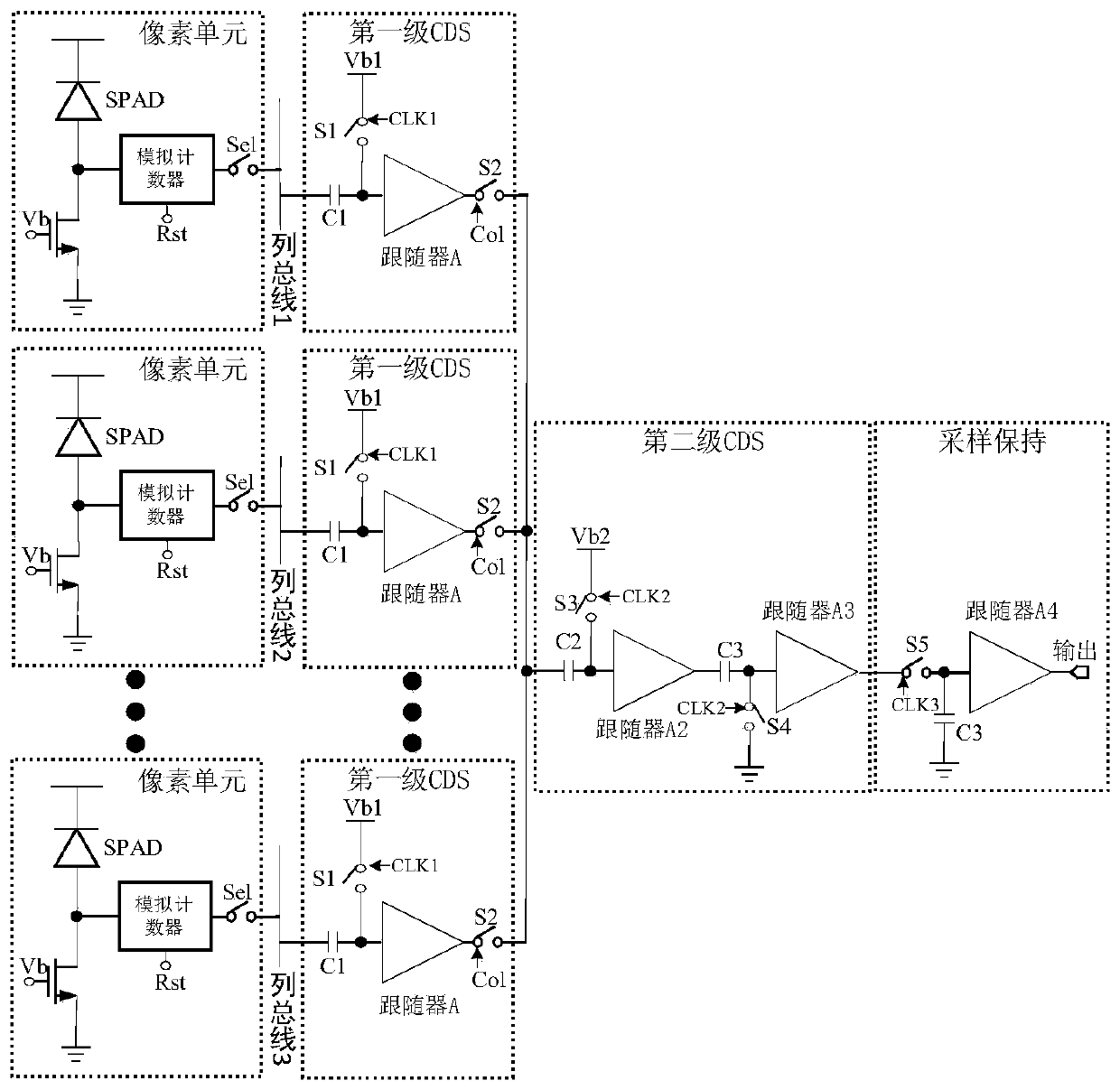

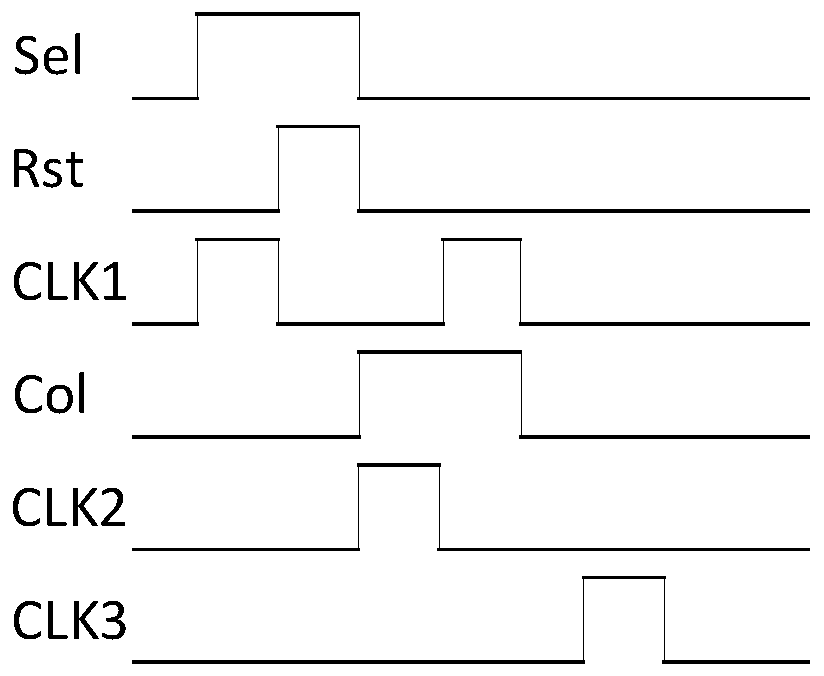

[0025] like figure 1As shown, the quadratic correlated double sampling array-level readout circuit based on the voltage follower proposed by the present invention is composed of two-stage CDS readout circuits. The first-stage CDS readout circuit is connected to each column bus, and the counting result in the analog counter of each row of pixel units is read into the first-stage CDS readout circuit through the column bus under the control of the row selection signal Sel. Under the control of the timing control signal CLK1, the first-stage CDS readout circuit samples twice the output results of the pixel unit after exposure and after reset, so as to eliminate the fixed pattern noise in the pixel unit. The first-stage CDS readout circuit on each column sends the result of the subtraction of two samples to the second-stage CDS readout circuit in time sequence unde...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More