Fin field effect transistor and method of forming the same

A fin field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve the problems that the performance of fin field effect transistors needs to be improved, and achieve the improvement of short channel effect and electric field control ability Enhanced, effective length-increased effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 example

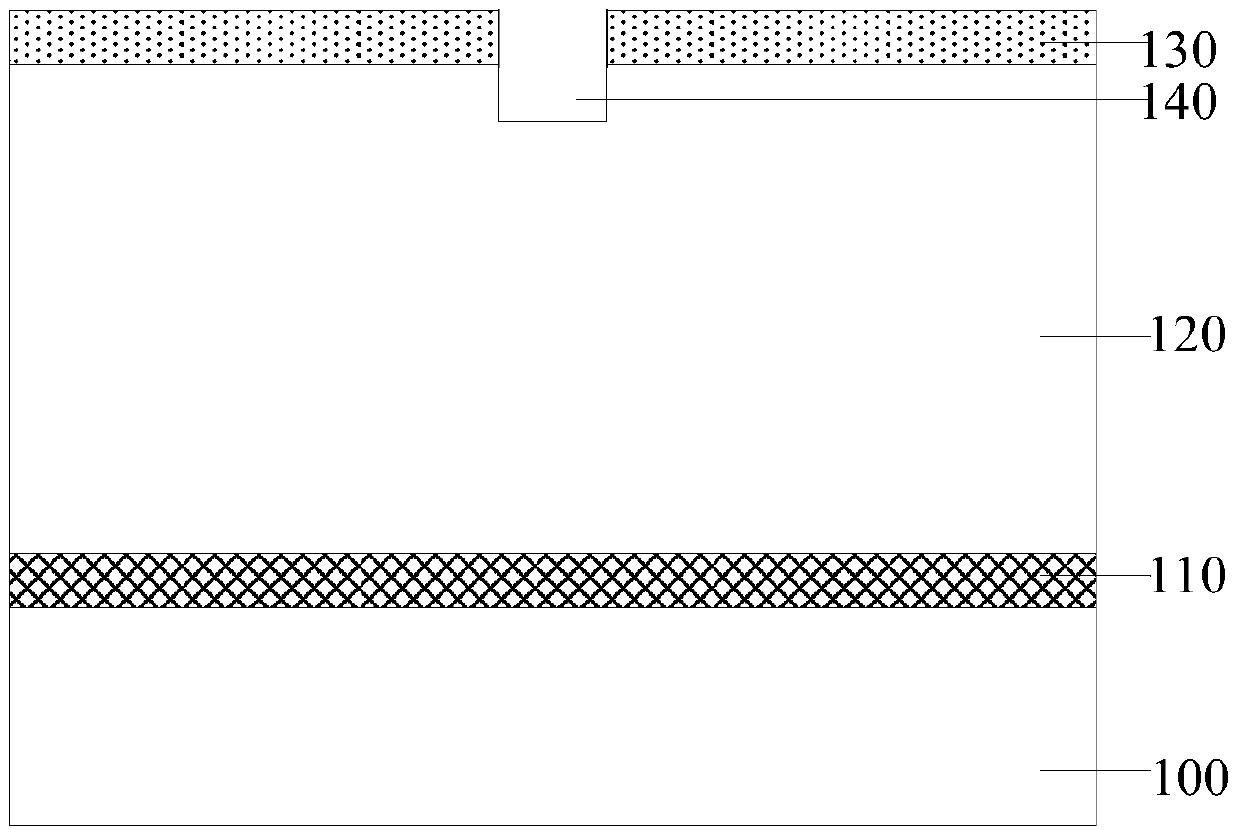

[0070] Figure 12 to Figure 20 It is a structural schematic diagram of the formation process of the fin field effect transistor in the second embodiment of the present invention.

[0071] The difference between the second embodiment and the first embodiment is that a groove is formed in the sacrificial layer, and the side wall of the groove has two pairs of groove protrusions, and each pair of groove protrusions is respectively located on both sides of the groove. side walls. The parts of the second embodiment that are the same as those of the first embodiment will not be described in detail.

[0072] refer to Figure 12 , Figure 12 for in Figure 6 Based on the schematic diagram formed, after forming the second protective layer 170, the second protective layer 170 and the sacrificial layer 120 are etched downward along the first groove 140 and the first opening 160, and the second protective layer 170 and the sacrificial layer 120 are formed at the bottom of the first op...

no. 3 example

[0103] Figure 21 to Figure 29 It is a structural schematic diagram of the formation process of the fin field effect transistor in the third embodiment of the present invention.

[0104] The difference between the third embodiment and the second embodiment is that a groove is formed in the sacrificial layer, and the side wall of the groove has three pairs of groove protrusions, and each pair of groove protrusions is respectively located on two sides of the groove. side walls. The parts of the third embodiment that are the same as those of the second embodiment will not be described in detail.

[0105] refer to Figure 21 , Figure 21 for in Figure 15 Based on the schematic diagram formed, after forming the fourth protective layer 230, the fourth protective layer 230 and the sacrificial layer 120 are etched downward along the first groove 140, the first opening 160, the second groove 200 and the second opening 220 , forming a third groove 340 at the bottom of the second o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More