Fin field effect transistor and method of forming the same

A fin field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve the problems that the performance of fin field effect transistors needs to be improved, and achieve the reduction of short channel effect and electric field control ability Enhanced, effective length-increased effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

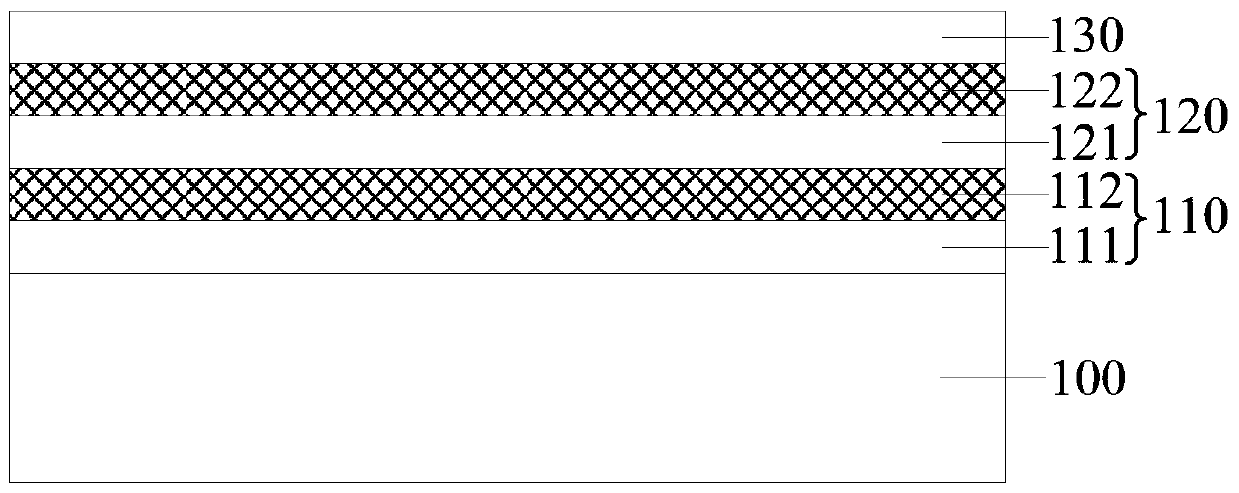

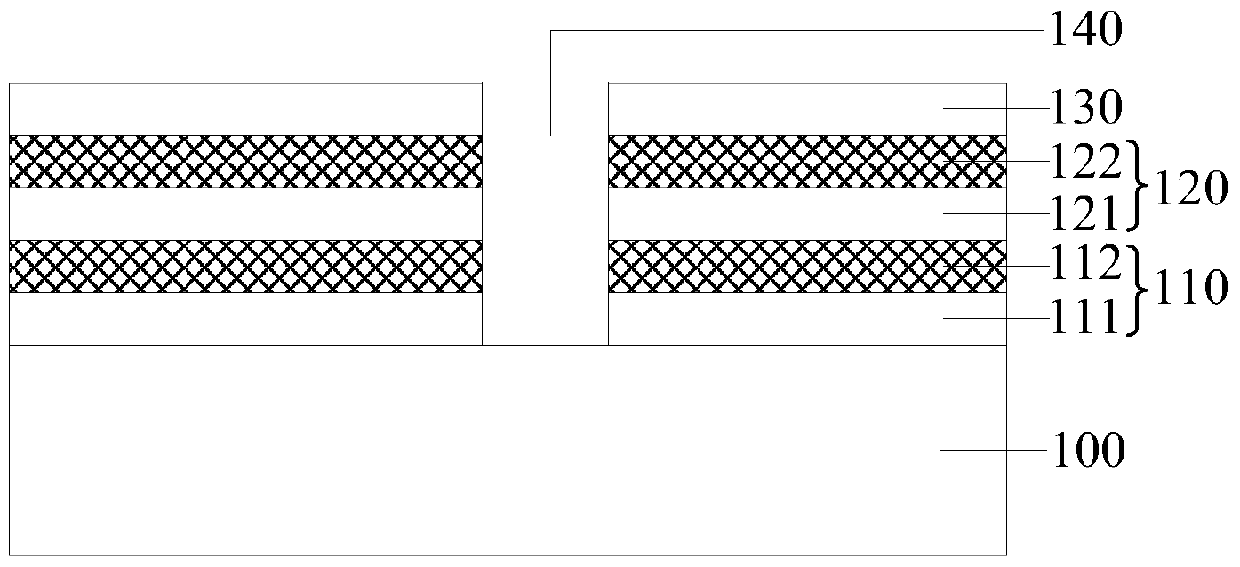

[0024] For the analysis of the fin field effect transistor formed in the prior art, the fin portion of the fin field effect transistor is usually formed by patterning the semiconductor substrate, and the sidewall of the fin portion is planar. With the further increase of the feature size, especially when the technology node is reduced below 10nm, the short channel effect of the fin field effect transistor in the prior art is serious.

[0025] On this basis, the present invention provides a method for forming a fin field effect transistor, in which several layers of sacrificial unit layers are sequentially formed on the semiconductor substrate from bottom to top, and the sacrificial unit layers include the bottom sacrificial layer and the The top sacrificial layer on the bottom sacrificial layer, and then a protective layer is formed on the several sacrificial unit layers; an anisotropic dry etching process is used to etch the protective layer and the sacrificial unit layer unti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More