Array base plate, display panel and display device

A technology for array substrates and base substrates, which is applied in the field of display devices and can solve problems such as source and drain short circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

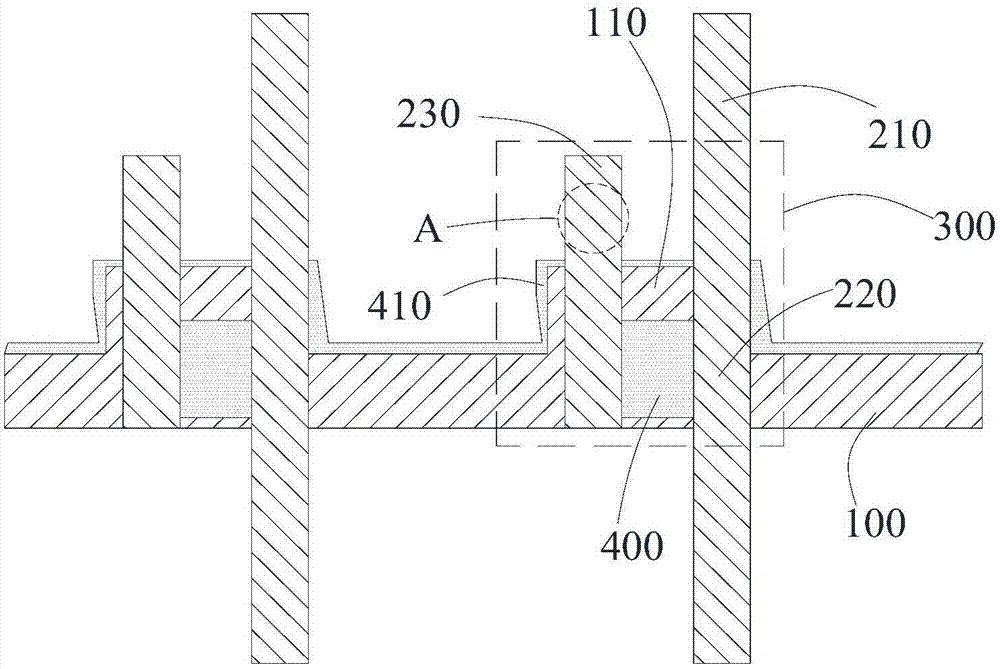

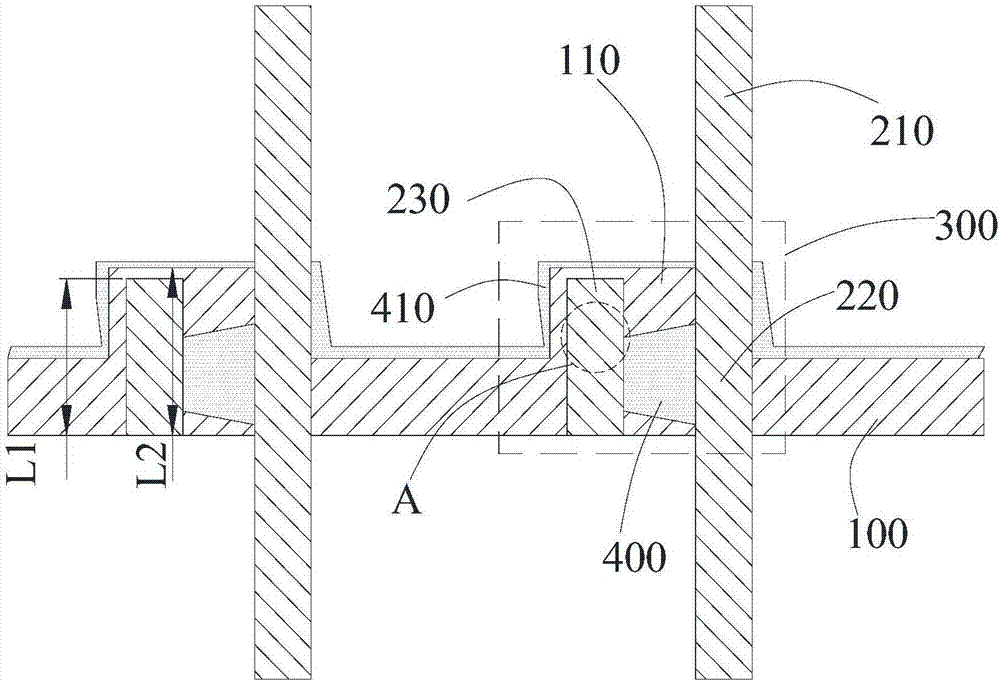

Image

Examples

Embodiment approach

[0037] As a preferred implementation manner of the present invention, the common electrode can be arranged between the pixel electrode and the base substrate. Specifically, the array substrate includes a passivation insulating layer covering the source-drain pattern layer, the array substrate further includes a pixel electrode layer, and the pixel electrode layer has a plurality of pixel electrodes, and each of the pixel units is provided with One said pixel electrode, said pixel electrode is electrically connected to a corresponding drain through a via hole penetrating through said passivation insulating layer.

[0038] As a second aspect of the present invention, a display panel is provided, and the display panel includes an array substrate, wherein the array substrate is the above-mentioned array substrate provided by the present invention.

[0039] Since there is no residual active layer material between the source and the drain in the thin film transistor of the array sub...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More