Array substrate and manufacturing method thereof

A manufacturing method and array substrate technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as electrostatic discharge damage, process abnormalities, and impact on product quality, so as to prevent electrostatic discharge and improve quality. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be further described in detail below with reference to the drawings and embodiments.

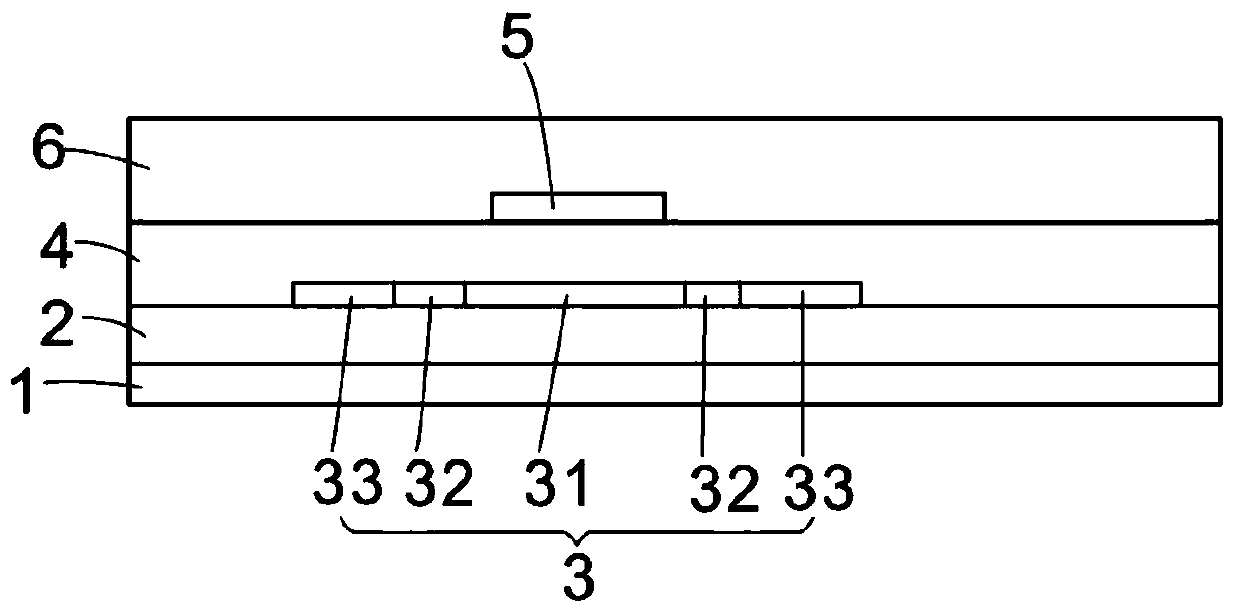

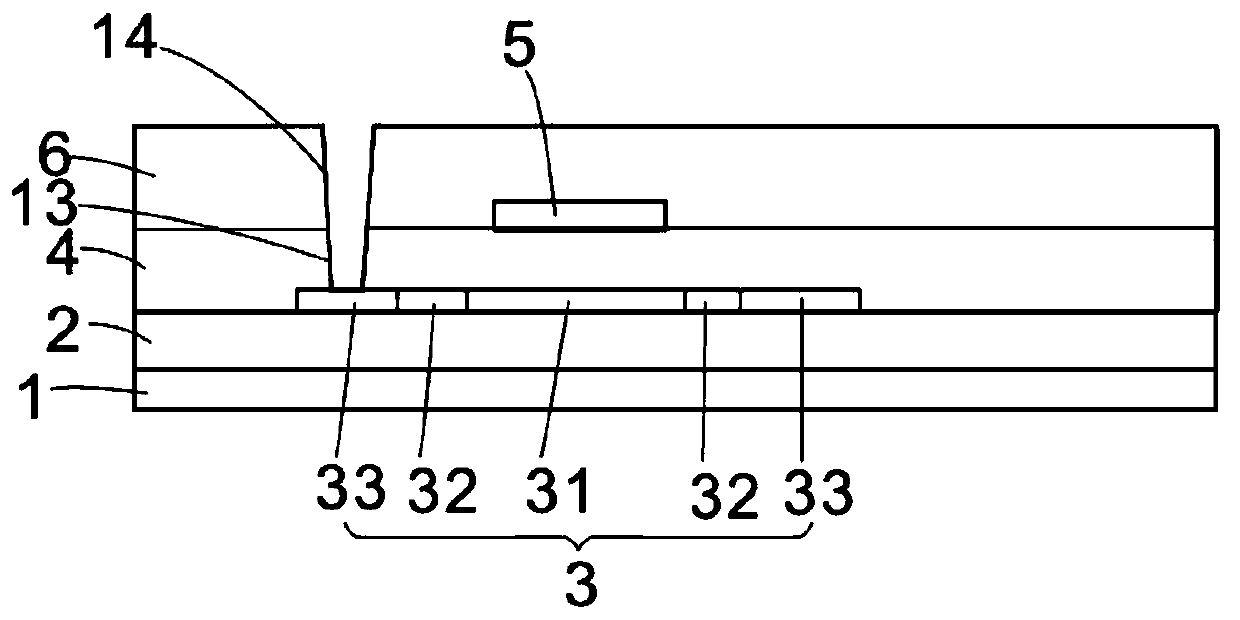

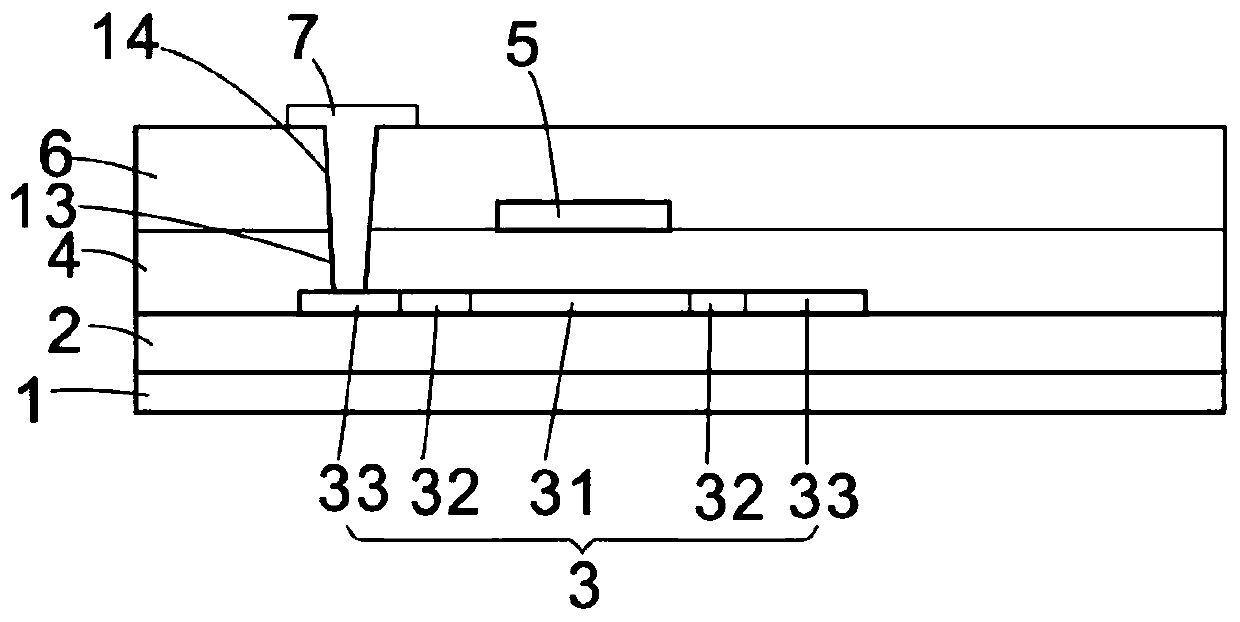

[0035] Such as Image 6 As shown, the array substrate of the present invention includes a substrate 1, a buffer layer 2, an active layer 3, a gate insulating layer 4, a gate 5, an interlayer insulating layer 6, and an interlayer insulating layer 6 sequentially disposed on the substrate 1. The first via 13 of the gate insulating layer 4 and the second via 14 of the gate insulating layer 4 are in contact with the source electrode 7, the flat layer 8, the common electrode 9, and the passivation layer 10 of the active layer 3; The source layer 3 is provided with a fourth via 91, the flat layer 8 is provided with a third via 81 at the fourth via 91, and a through fourth via 91 and a third via are provided on the passivation layer 10 81. The flat layer 8, the interlayer insulating layer 6, and the fifth via hole 11 of the gate insulating layer 4. A pixel electrode 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More