Settling time test method and system for digital to analog converter

A technology of digital-to-analog converter and settling time, applied in the direction of analog/digital conversion calibration/test, analog/digital conversion, code conversion, etc., can solve problems affecting product development progress and achieve the effect of setting up time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

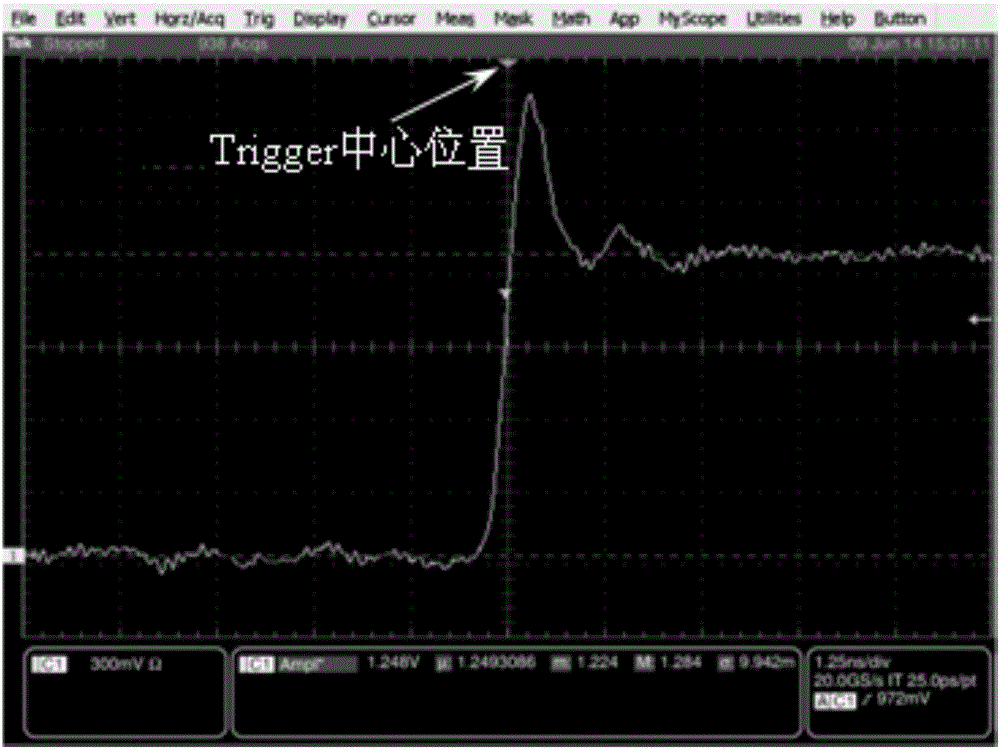

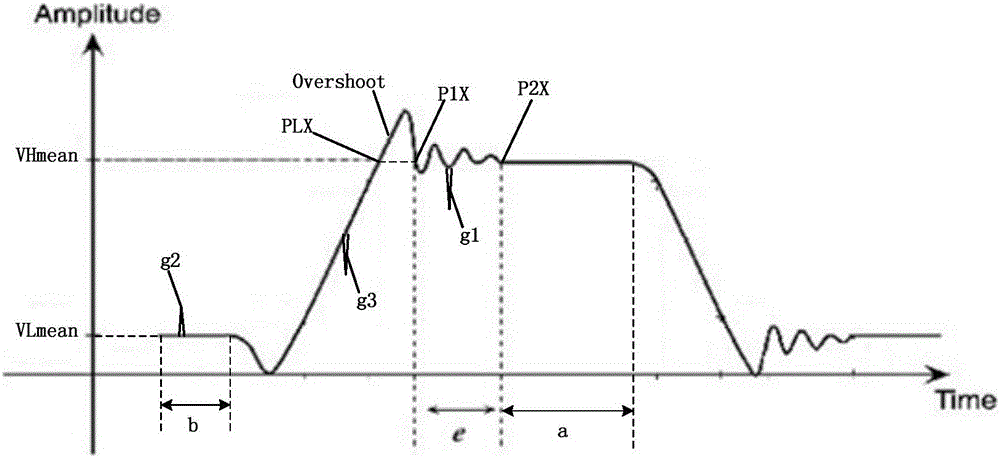

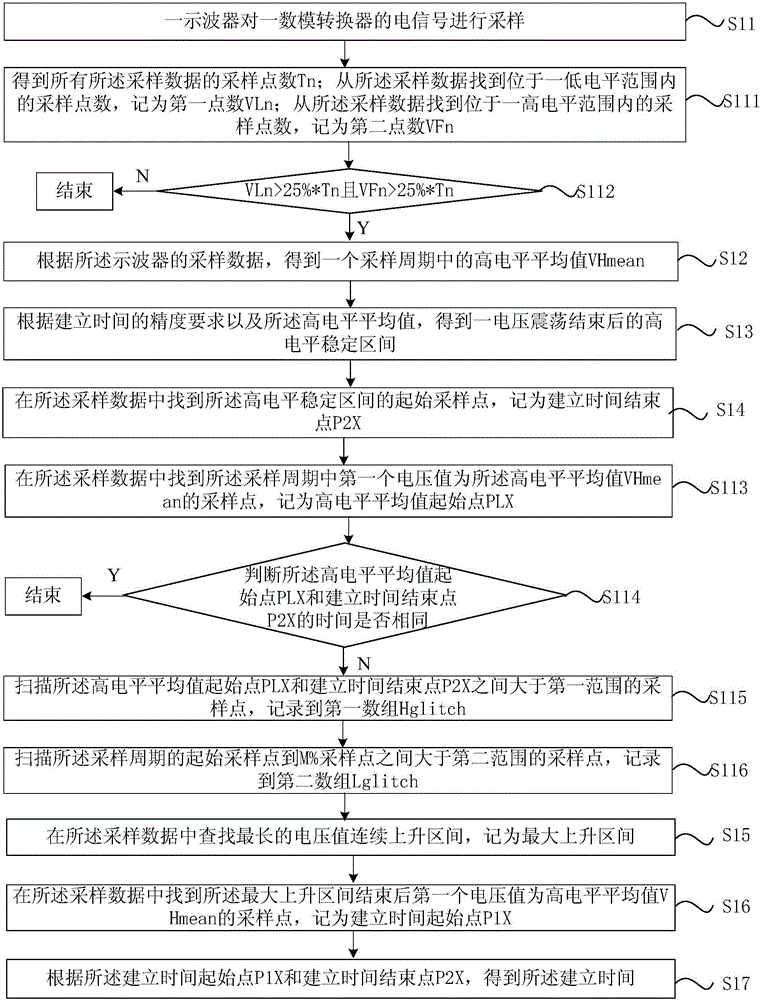

[0059] figure 1 For the waveform diagram of the measured data output by the digital-to-analog converter, the prior art cannot automatically test the setup time of the digital-to-analog converter, and manual identification is required based on the measured data output by the digital-to-analog converter. The inventor studied the setup time and the waveform output by the digital-to-analog converter and found that in one sampling period, such as figure 2 Shown (in figure 2 Where the abscissa is the time time, the ordinate is the voltage amplitude (amplitude), after the voltage overshoot (overshoot), after the end of the voltage oscillation, enters the high-level stable interval a, in the high-level stable interval a, the voltage The average value is the high level average value VHmean. After the overshoot (overshoot), the first time the voltage value is the high-level average value VHmean sampling point is the setup time start point P1X, the high-level stable interval a starts at ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More