Chip testing and sealing device and technology thereof

A technology of chip testing and testing equipment, which is applied in the fields of electronic circuit testing, electrical components, semiconductor/solid-state device manufacturing, etc. It can solve the problems of poorly sealed cover tape, cover tape disengagement, maximum and minimum Gauss amount, etc., to achieve The effect of external disturbance reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

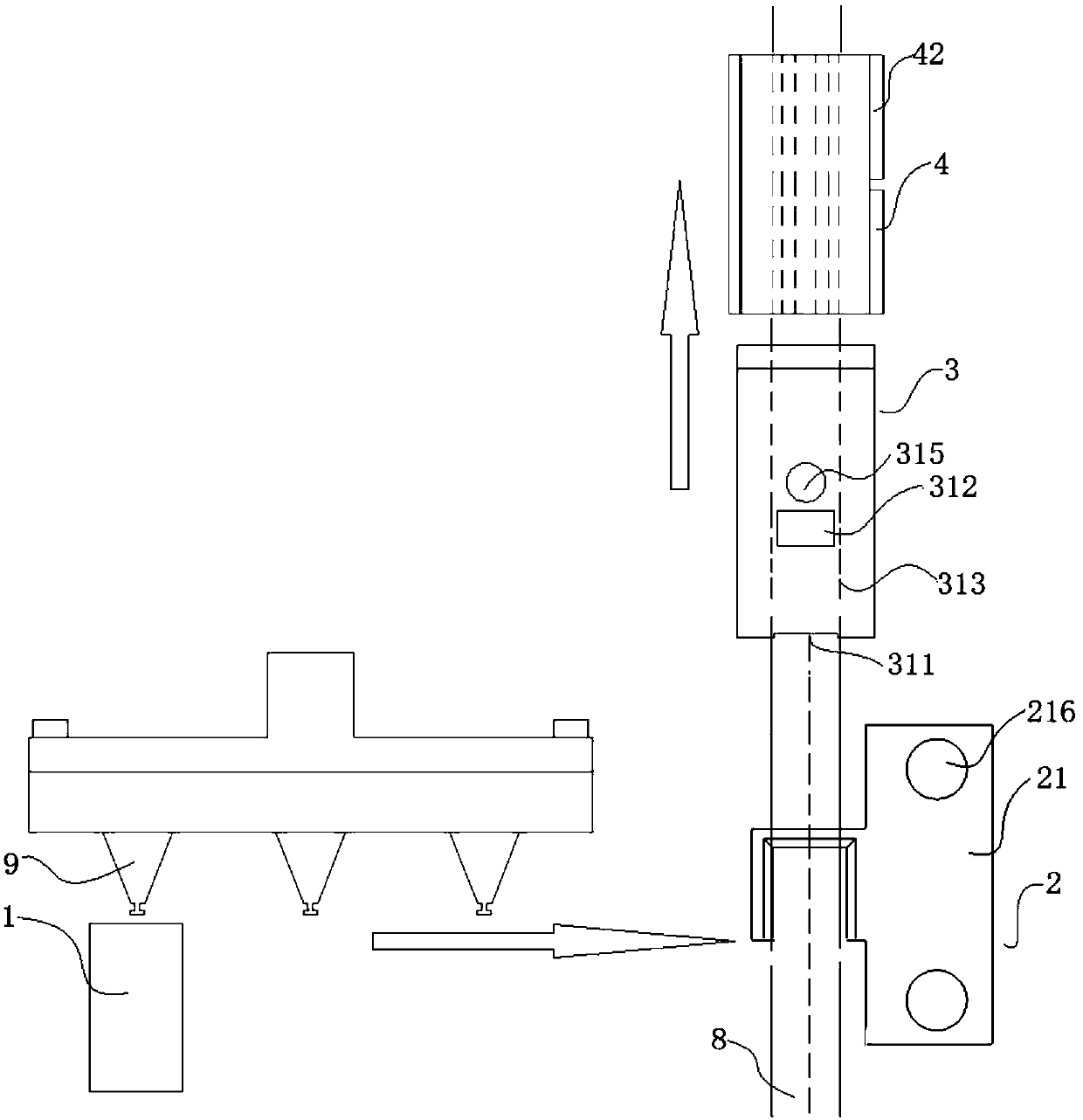

[0093] The chip testing and sealing device of the present embodiment, such as figure 1 As shown, it includes a suction nozzle 9, a test device 1, and an anti-snap into the bag mechanism 2, an anti-cover tape offset mechanism 3, and a sealing knife mechanism 4 arranged in a process sequence above the carrier tape 7. The suction nozzle 9 will test The chip 8 after the device 1 test is transferred to the anti-snap pin into the bag mechanism 2, wherein: as Figure 28 As shown, the test device 1 includes a Hall coil 11, a collar 12, a test base 13, a Hall test piece and a Hall movable clamp 16; the Hall coil includes an I-shaped support 112 and is wrapped in the middle of the I-shaped support 112. Parts of the enameled wire coil 111, such as Figure 36 , 37, 38, one end of the I-shaped bracket 112 is a ring platform 1121, and the center of the ring platform 1121 is a circular groove 1124; the center of the circular groove 1124 is a circular through hole 1123. The chip 8 can be ...

Embodiment 2

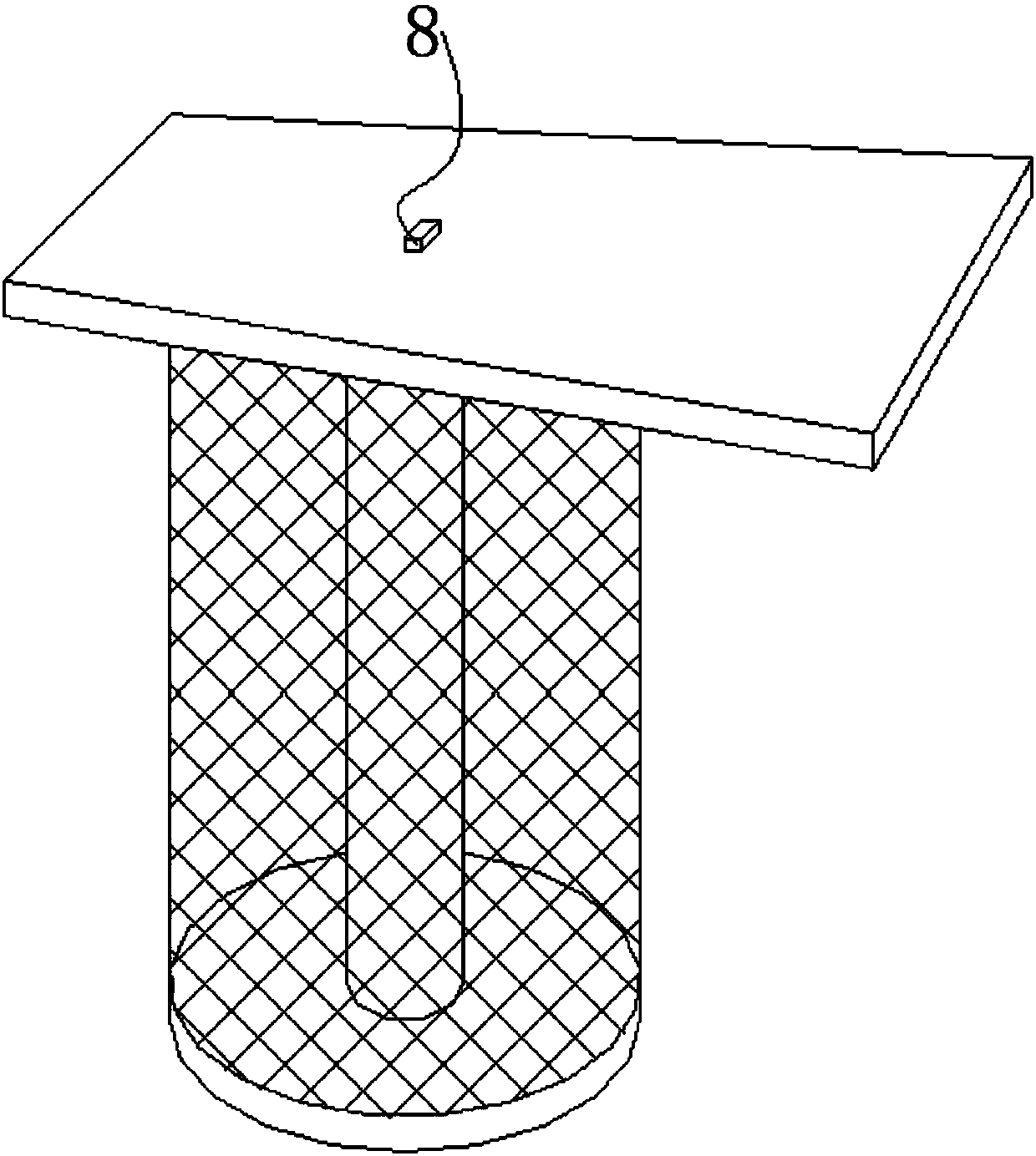

[0095] The chip testing and sealing device of present embodiment, basic structure is the same as embodiment 1, difference and improvement are: the depth of circular groove 1124 is not less than the sum of the thickness of test base 13, test piece and chip 8, with It is ensured that the chip 8 does not protrude from the circular groove 1124, thereby ensuring the stability of the test magnetic field. On the ring platform 1121 of the I-shaped bracket 112, two left and right symmetrical slots 1122 are opened outward from the circular groove 1124, providing passages for the chip 8 to enter and exit. The shape and size of the bottom of the braiding window 22 are consistent with the opening of the bag of the carrier tape 7, which is 3.3×3.2mm, forming a straight drop microchannel of the chip to avoid secondary offset when the chip is inserted; Mechanism and directional track mechanism cooperate to realize, and elastic mechanism realizes the purpose of buffering, and directional track...

Embodiment 3

[0097] The chip testing and sealing device of present embodiment, basic structure is the same as embodiment 2, difference and improvement point are: the two ends of the enameled wire volume 111 of Hall coil and ring platform 1121 directly contact (without gasket), avoid unnecessary The magnetic field interference factor, the periphery of the enameled wire coil 111 is exposed, so as to improve the efficiency of the magnetic field. Such as Figure 7 As shown, the braiding window 22 includes a square area 221 at the bottom and a receiving area 222 at the top, and the thickness ratio of the two is 2-4:6-8. In this embodiment, the thickness ratio of the two is 3:7, and the thickness of the receiving area is relatively large. Larger, almost twice as large, providing a relatively large operating space for deviation correction; the upper surface of the pressure plate 31 is fixed with a vertical pressure plate male rail 312; the bottom surface of the bracket 32 is provided with a Su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More