A control method, device and converter for a single-inductance multi-output converter

A single-inductor multi-output, control device technology, applied in output power conversion devices, adjustment of electrical variables, control/regulation systems, etc., can solve problems such as low load capacity and large ripple

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. Obviously, the described embodiments are only some embodiments of the present invention, rather than all embodiments . Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

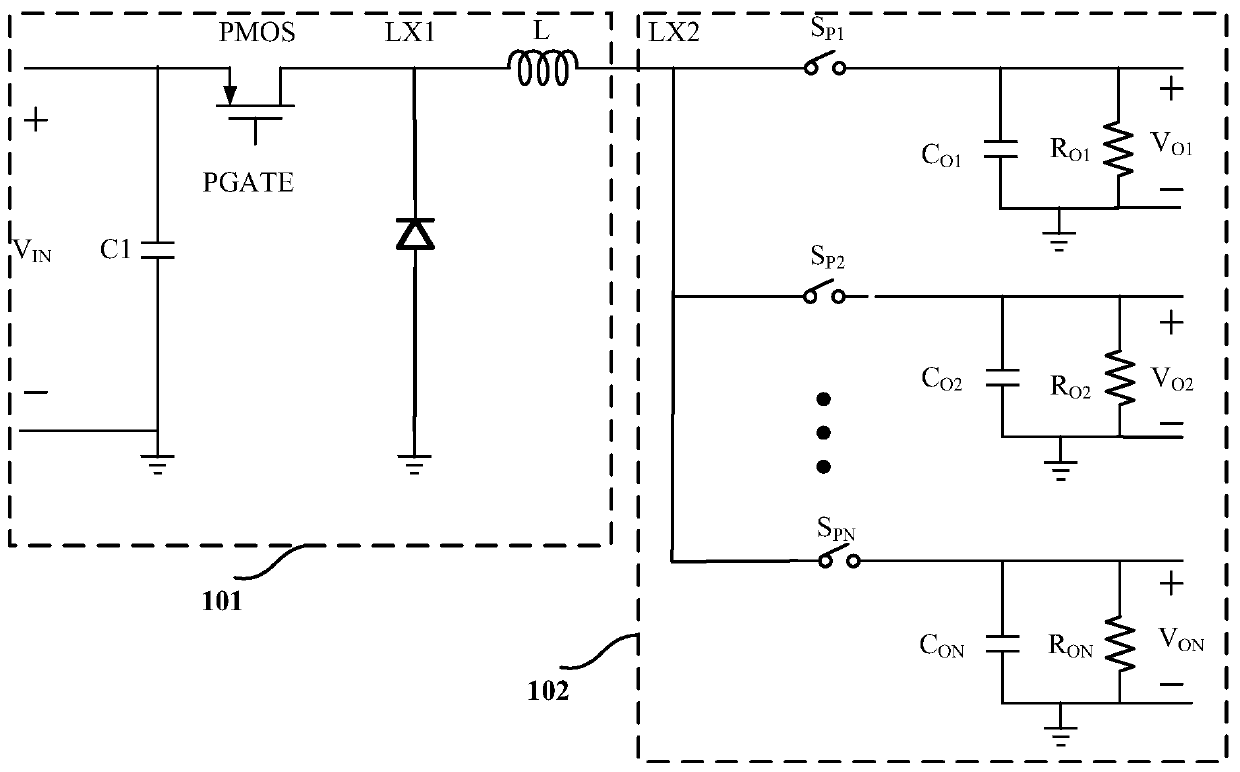

[0032] A Single Inductor Multiple Output (SIMO) converter utilizes the time-sharing working principle of each output branch, and can independently control multiple energy outputs by using one inductor. Since a plurality of output branches share one inductance, they can work in time-division, reducing the number of inductances required by the circuit, so while realizing independent control of each output branch, the size of the converter sys...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com