UVM environment constructing method and system

An environment and module-under-test technology, applied in the field of general verification methodology, can solve problems such as time-consuming, complex verification environment, and the inability of verification engineers to complete independently, saving time, improving verification efficiency, and reducing verification difficulty.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] Specific embodiments of the present disclosure will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present disclosure, and are not intended to limit the present disclosure.

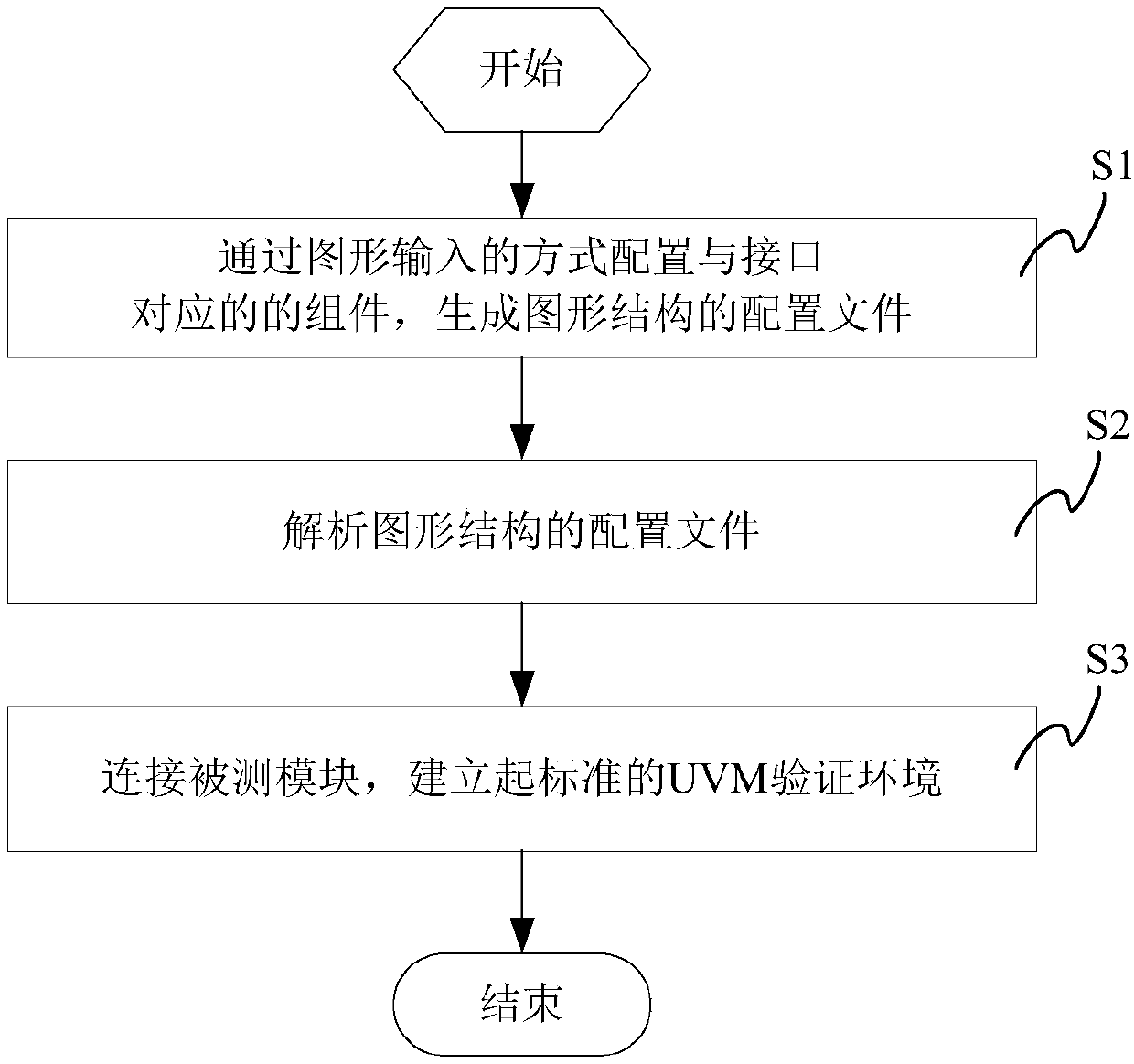

[0065] Such as figure 2 As shown, the overall flowchart of a UVM environment construction method provided by the present invention, the method includes:

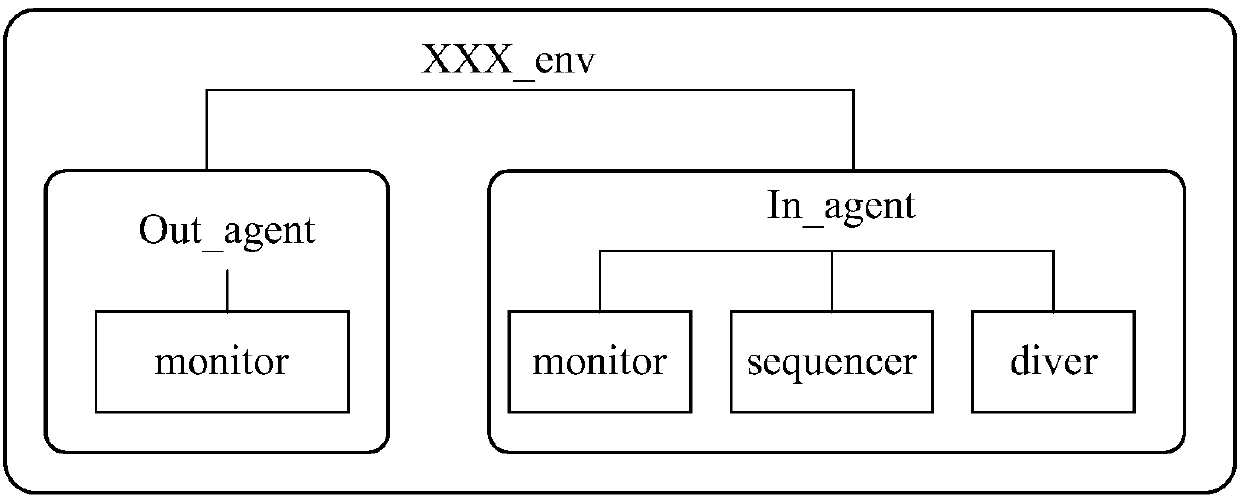

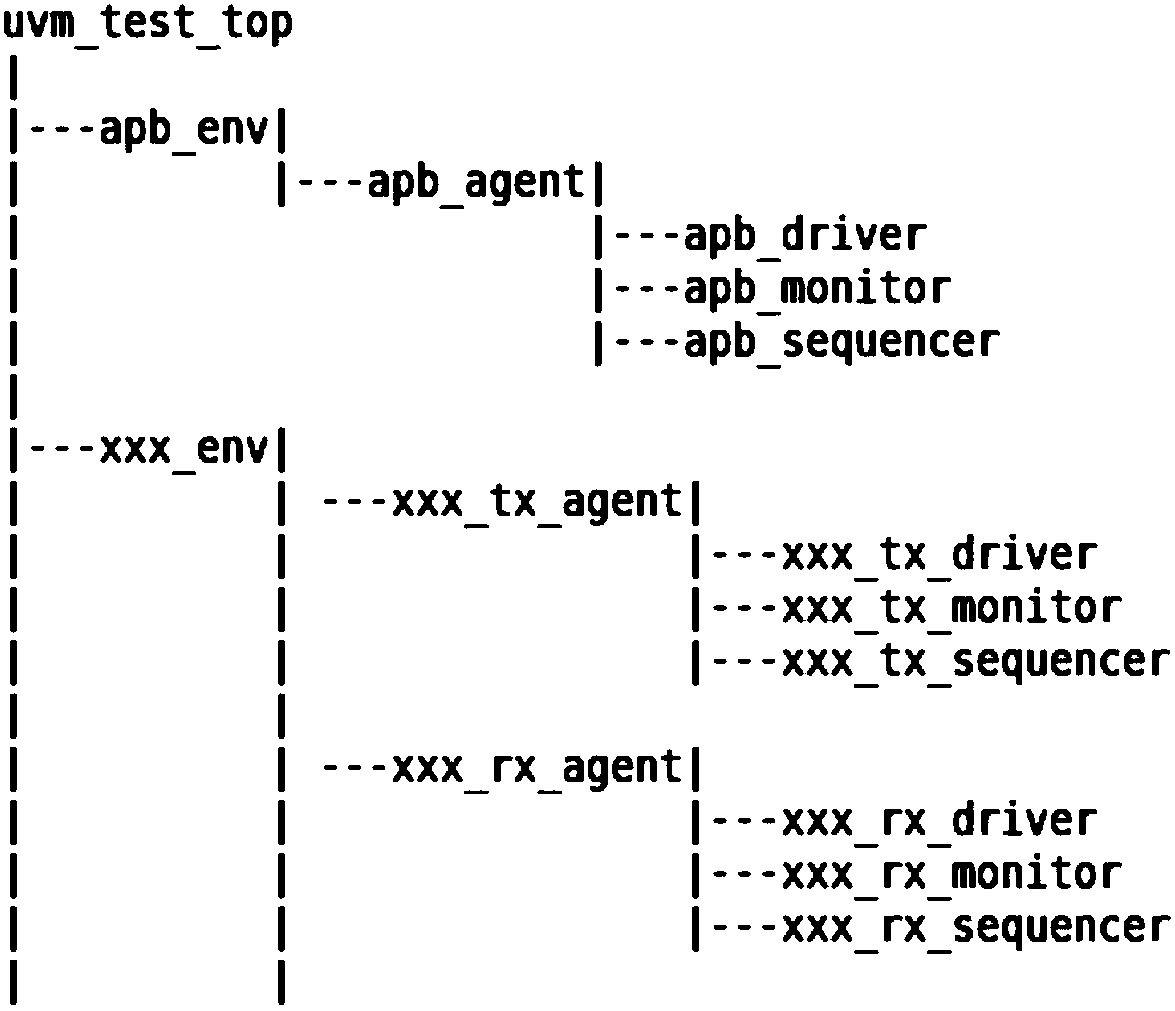

[0066] Step S1, according to the interface type of the module under test, configure the components corresponding to the interface through graphic input, the components include at least sequencer, driver and detector monitor, and generate a configuration file of graphic structure;

[0067] Step S2, analyzing the configuration file of the graphic structure to obtain the UVM tree structure and the corresponding UVM environment file;

[0068] Step S3, connecting the module under test for establishing a stand...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More