System-level packaging chip and packaging method thereof

A system-in-package and chip technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of poor chip portability and versatility, and achieve the effect of convenient upgrading, reducing package size and saving chip cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

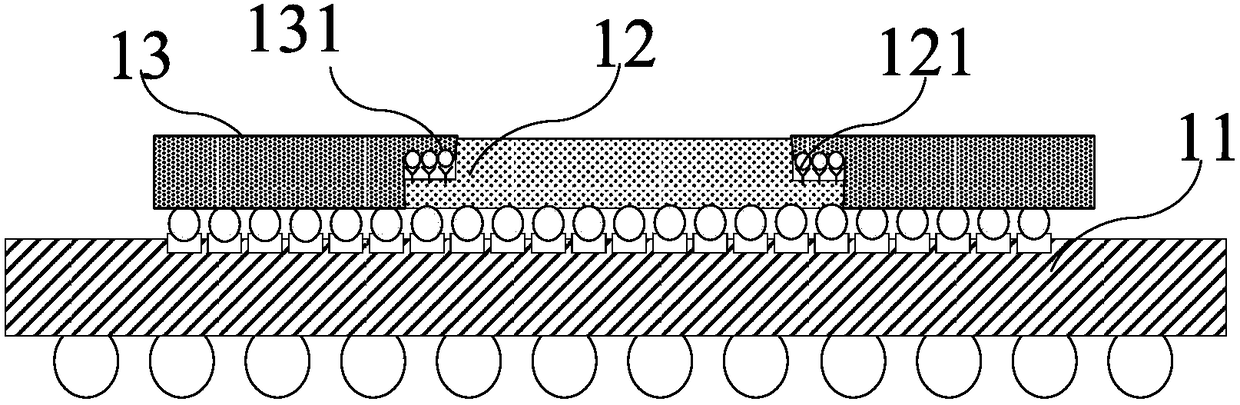

[0052] figure 1 It is a schematic diagram of the composition and structure of the SiP chip in the embodiment of the present invention, such as figure 1 As shown, the composition of the SiP chip in the embodiment of the present invention includes: a packaging substrate 11 and a first chip 12 and at least one second chip 13 located on the packaging substrate; wherein,

[0053]The first chip 12 and the at least one second chip 13 are respectively connected to the package substrate 11 by flip-chip bonding;

[0054] The first chip 12 is provided with a concave undercut interface 121, and the second chip 13 is provided with a convex undercut interface 131;

[0055] The first chip 12 is connected to the at least one second chip 13 through the concave inverted interface 121 and the convex inverted interface 131; here, a plurality of second chips can be located around the first chip, It is electrically connected with the concave undercut interface around the first chip through its ow...

Embodiment 2

[0067] Figure 6 It is a schematic diagram of the composition and structure of the SiP chip in the embodiment of the present invention, such as Figure 6 As shown, the composition of the SiP chip in the embodiment of the present invention includes: a packaging substrate 61 and a first chip 62 and at least one second chip 63 located on the packaging substrate; wherein,

[0068] The first chip 62 and the at least one second chip 63 are respectively connected to the package substrate 61 by flip-chip bonding;

[0069] The first chip 62 is provided with a concave undercut interface 621, and the second chip 63 is provided with a convex undercut interface 631;

[0070] The first chip 62 is connected to the at least one second chip 63 through the concave inverted interface 621 and the convex inverted interface 631; The undercut interface is electrically connected to the concave undercut interface around the first chip;

[0071] The SiP chip further includes at least one third chip ...

Embodiment 3

[0085] Figure 8 It is a schematic flow diagram of the SiP chip packaging method in the embodiment of the present invention, as Figure 8 As shown, the SiP chip packaging method in the embodiment of the present invention includes:

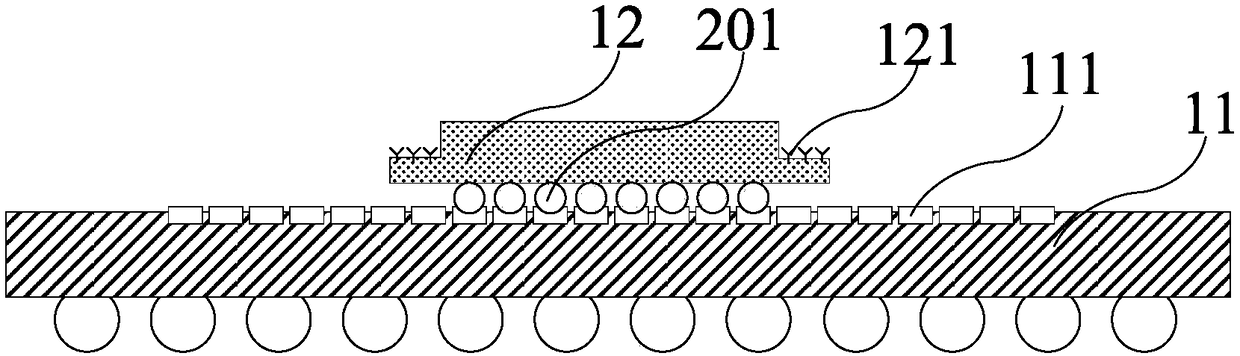

[0086] Step 800: Provide a packaging substrate, a first chip and at least one second chip.

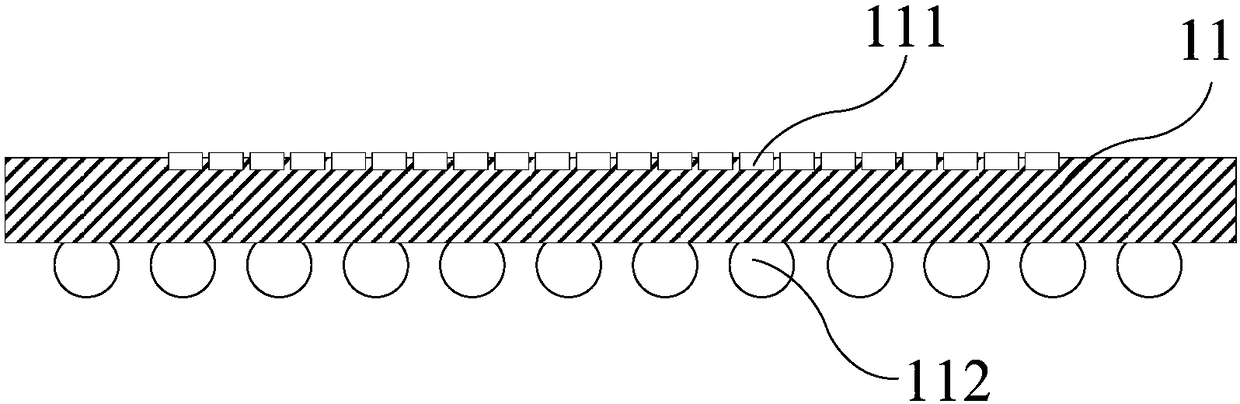

[0087] Here, the upper surface of the packaging substrate can be provided with conductive pads, and the lower surface can be provided with conductive solder balls, such as figure 2 Shown is a schematic diagram of the composition and structure of the packaging substrate. Both the conductive pads and the conductive solder balls are made of conductive metal materials, and the conductive solder balls can be electrically connected to the conductive pads through the metal interconnection structure inside the packaging substrate; The packaging substrate is characterized by mechanical flexibility and high-density interconnects.

[0088] The first chip is provided...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More