A Parallel String Matching Algorithm Based on FPGA

A string matching and pattern string technology, applied in the field of information processing, to achieve the effect of good performance, flexibility and high matching rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

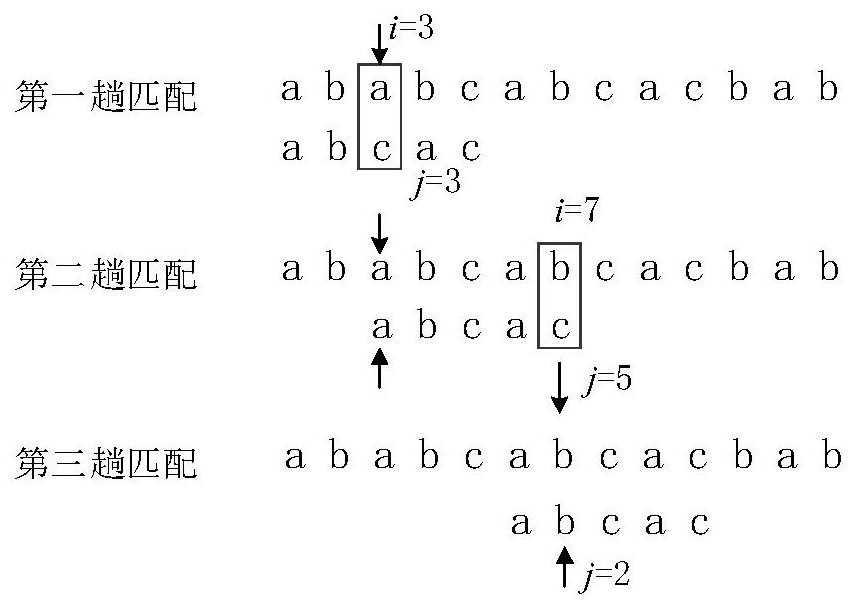

Method used

Image

Examples

Embodiment 1

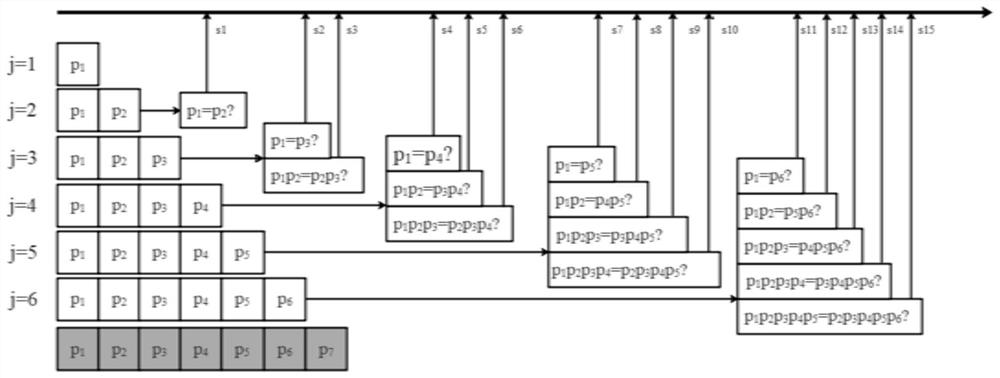

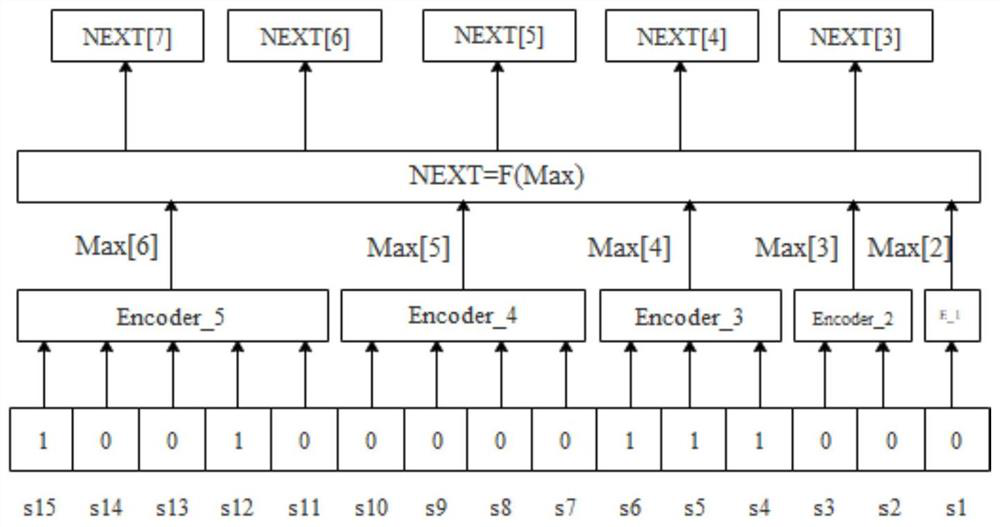

[0113] In order to explain the technical solution in detail, give how to realize the design of this solution in FPGA, and give an example, the pattern string P=abcdabd, the substring of the first j characters has been given in Table 2-2 , along with its prefix and suffix and the maximum common element length. Such as Figure 6 Shown is the parallel processing of this pattern string. The substrings corresponding to j=2 to j=6 are compared respectively, and each is regarded as a module, specifically:

[0114] j=2: compare a and b, if they are equal, output s1=1, otherwise s1=0;

[0115] j=3: compare a and c, ab and bc, if they are equal, output s2=1, s3=1, otherwise s2=0, s3=0;

[0116] j=4: compare a and d, ab and cd, abc and bcd, if they are equal, output s4=1, s5=1, s6=1, otherwise s4=0, s5=0, s6=0;

[0117] j=5: Compare a and a, ab and da, abc and cda, abcd and cdba, if they are equal, output s7=1, s8=1, s9=1, s10=1, otherwise s7=0, s8=0 , s9=0, s10=0;

[0118] j=6: co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More