FPGA implementation method for Cholesky decomposition of positive definite matrix

An implementation method, a positive definite matrix technology, applied in complex mathematical operations, etc., to achieve high data throughput, reduce computational complexity and the effect of gate circuit area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The solution of the present invention will be described in detail below in conjunction with the accompanying drawings.

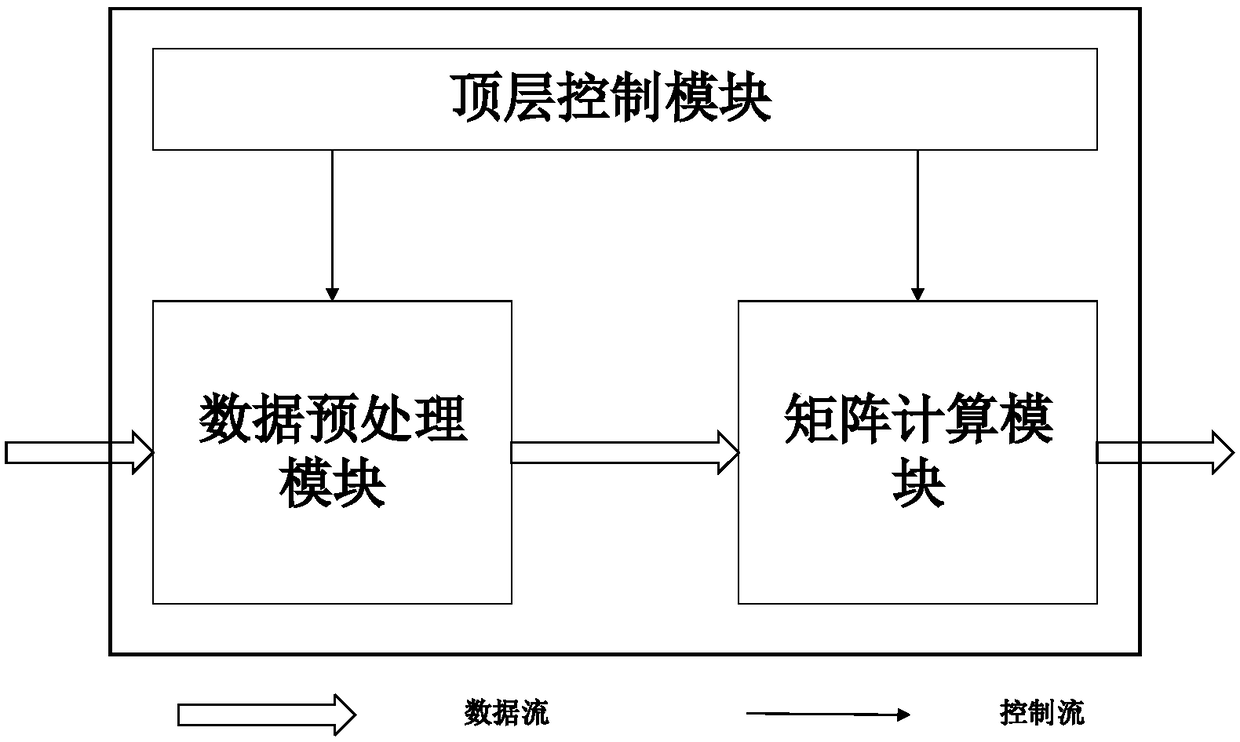

[0037] Such as figure 1 As shown, the FPGA implementation method of Cholesky decomposition of a positive definite matrix in this embodiment is mainly composed of a top-level control module, a data preprocessing module and a matrix calculation module. The data is first input to the data preprocessing module, and the state transition is controlled by the top-level control module. After the data preprocessing is completed, the top-level control module controls the flow of data to the matrix calculation module, and controls the matrix calculation module to process the data. After the matrix Cholesky decomposition is completed , the top-level control block allows output of result data.

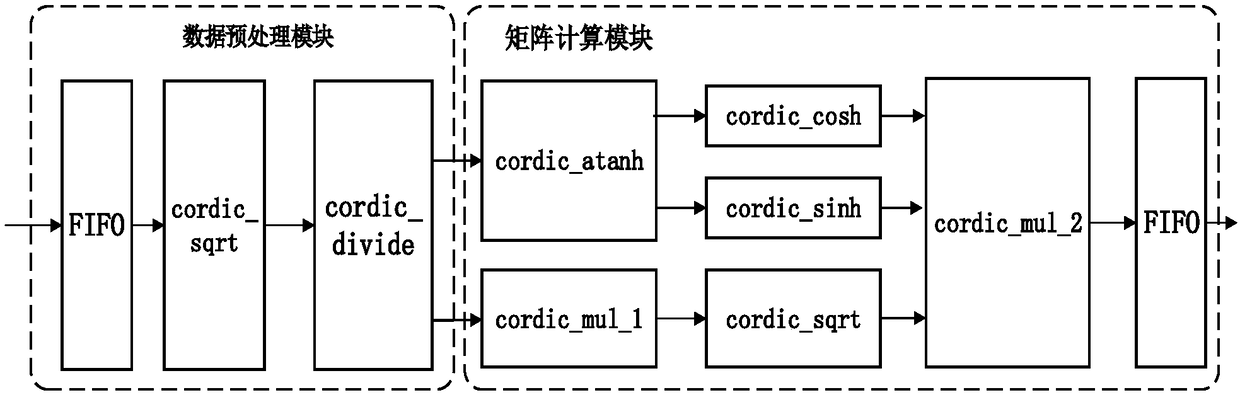

[0038] Such as figure 2 As shown, the data input from the outside world is temporarily stored in the input FIFO, and then sent to the data preprocessing module for proc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More