Hardware acceleration structure device and control method for general character string processing

A technology of hardware acceleration and acceleration structure, applied in electrical digital data processing, machine execution devices, program control design, etc., can solve problems such as low efficiency, and achieve the effects of easy integration, improved processing performance, and effective structural design.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

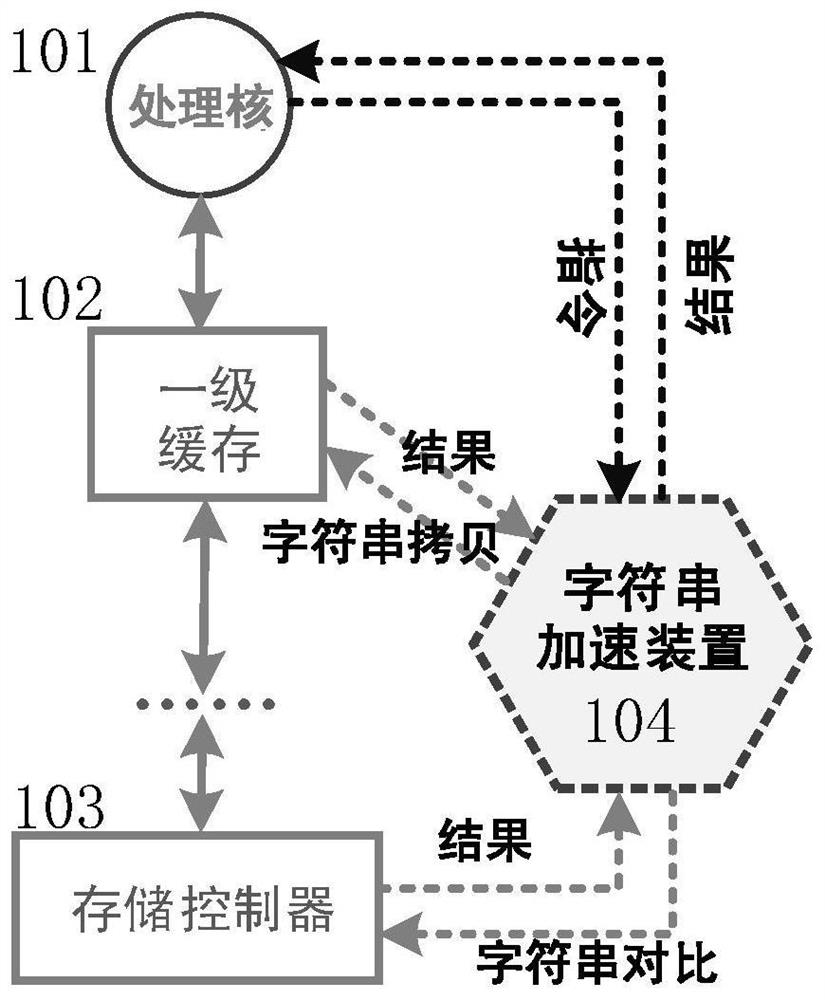

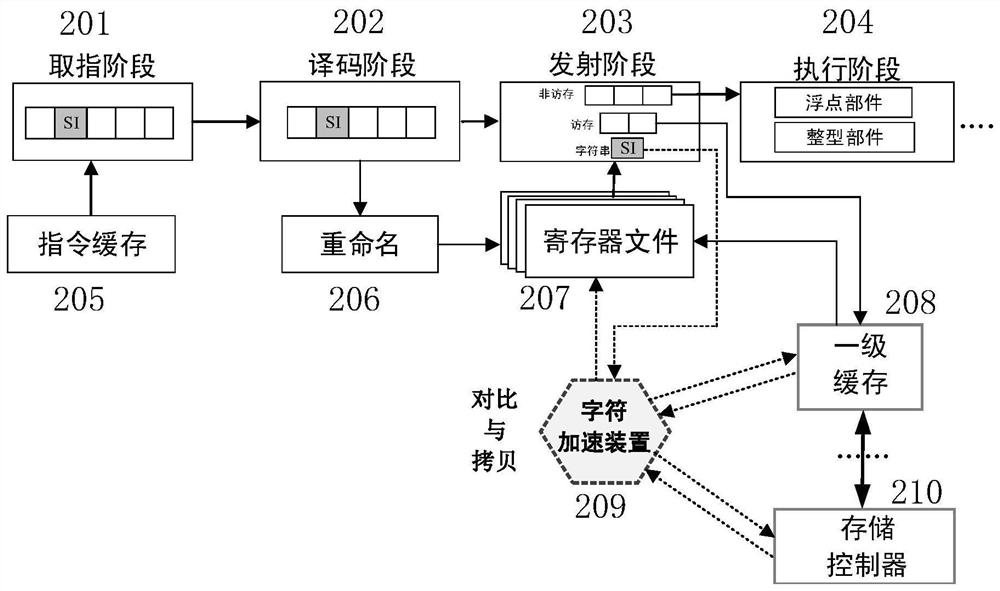

[0046] like figure 1As shown, the string hardware acceleration structure device (Sting Accelerator) is set on the chip, adjacent to the memory controller and the on-chip Cache. For the string comparison operation (string compare), the corresponding acceleration processing structure is set in the adjacent memory controller (DDR Controller). The corresponding accelerated processing structure for string copy is set adjacent to the on-chip first-level Cache. The reason for doing this is: 1) the goal of this device is to design a general-purpose character string processing acceleration structure, which can be integrated in a general-purpose processor, so the structure needs to be integrated on-chip; 2) because this device is aimed at big data applications, The amount of data is huge. For example, Terasort is for terabyte-level data sorting. Therefore, the design principle of this device is to place the processing device as close as possible to the main memory, and the character s...

Embodiment 2

[0053] like figure 1 As shown, the present invention is based on a traditional processor system, and adds a string processing acceleration structure 104. The string comparison operation of the acceleration structure 104 is placed next to the storage controller 103, and by directly requesting data from the storage control 103, character string processing is performed. string processing. The character string copy of the acceleration structure 104 is placed next to the first-level Cache 102, and the character string is copied by reading the Cache line data from the first-level Cache 102. The acceleration structure 104 is controlled by the instructions issued by the pipeline of the processor core 101 , and writes the result of the operation back into the processor core 101 .

[0054] The following are the specific operation steps of each functional module:

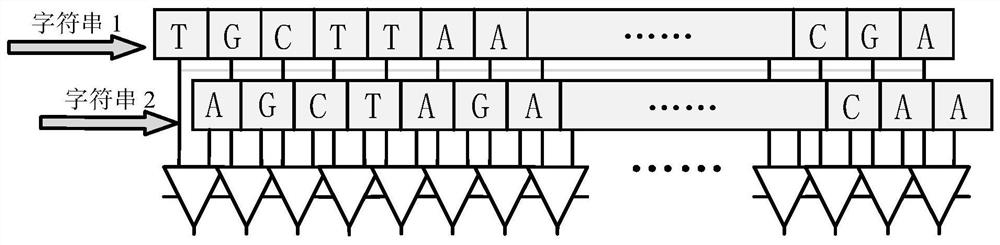

[0055] like Figure 5 As shown, it is a string comparison operation accelerator. Character comparison operation steps: ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More