Method for improving timing margin of NandFlash bus

A bus timing and margin technology, applied in the storage field, can solve the problems of NandFlash bus operating speed, storage performance improvement, signal edge degradation, and low operating speed, so as to improve timing margin, shorten fall time, and increase operating speed. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

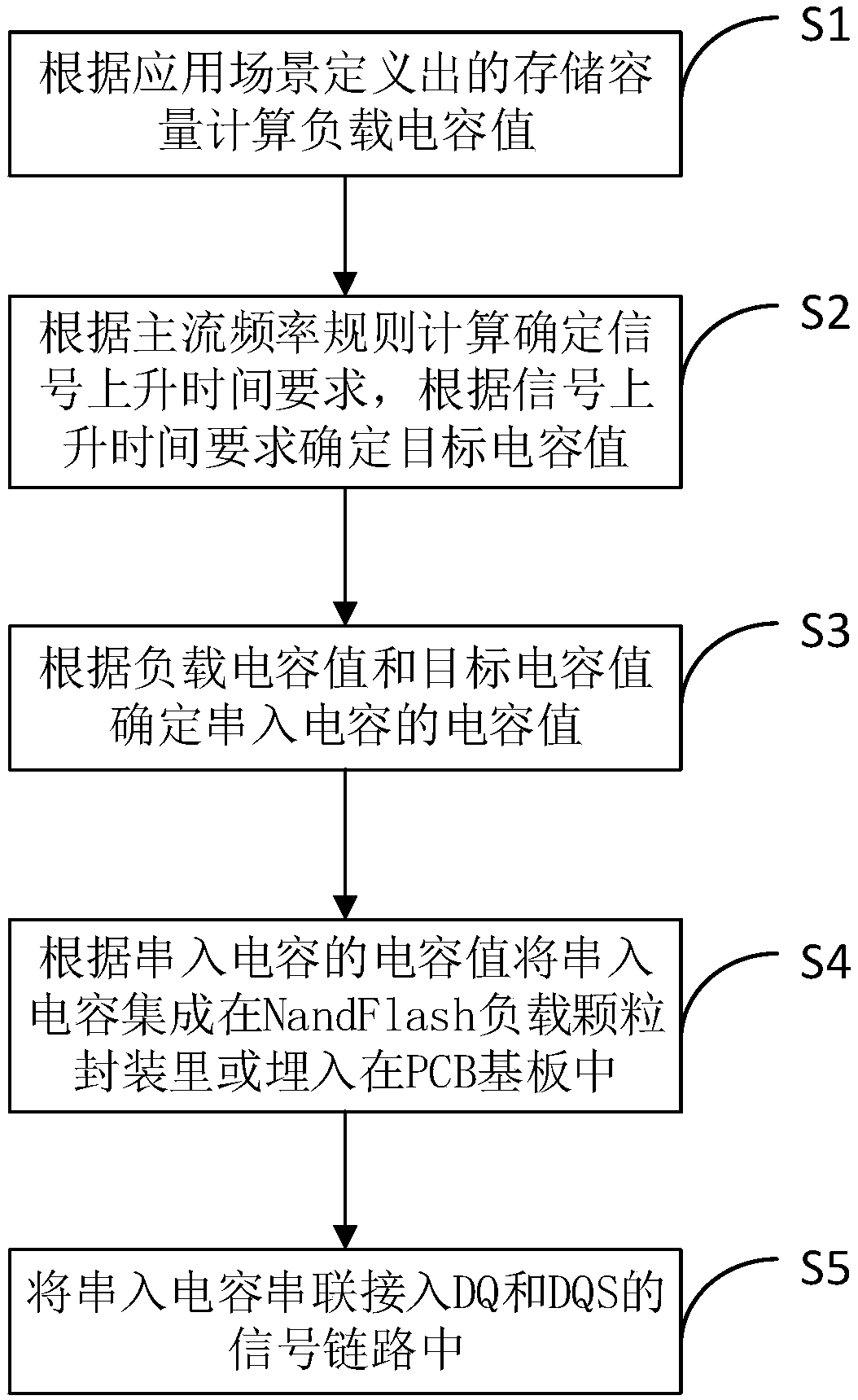

[0018] Such as figure 1 as shown, figure 1 It is a flowchart of a method for improving the timing margin of the NandFlash bus proposed by the present invention.

[0019] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

[0020] A method for improving the timing margin of the NandFlash bus, comprising the following steps:

[0021] S1: Calculate the load capacitance value according to the storage capacity defined by the application scenario;

[0022] S2: Calculate and determine the signal rise time requirement according to the mainstream frequency rule, and determine the target capacitance value according to the signal rise time requirement;

[0023] S3: Determine the capacitance value of the capacitor connected in series according to the load capacitance value and the target capacitance value;

[0024] S4: According to the capacitance value of the serial capacitor, integrate the serial capacitor into the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com