LinkPort communication system and method based on FPGA

A communication method and communication system technology, applied in the field of FPGA-based LinkPort communication system, can solve problems such as not detailed description, high FPGA performance, inability to apply low-end FPGA, etc., to increase timing margin, optimize timing, and facilitate timing Convergence effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0044] ODDR / IDDR: FPGA primitives.

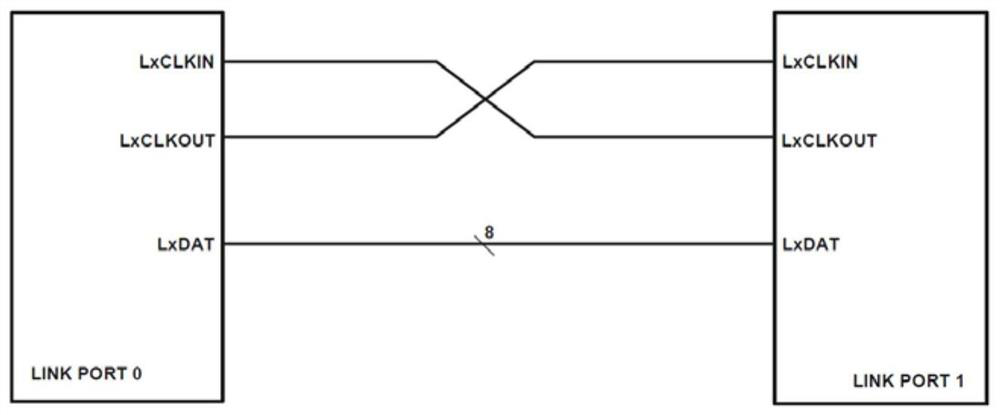

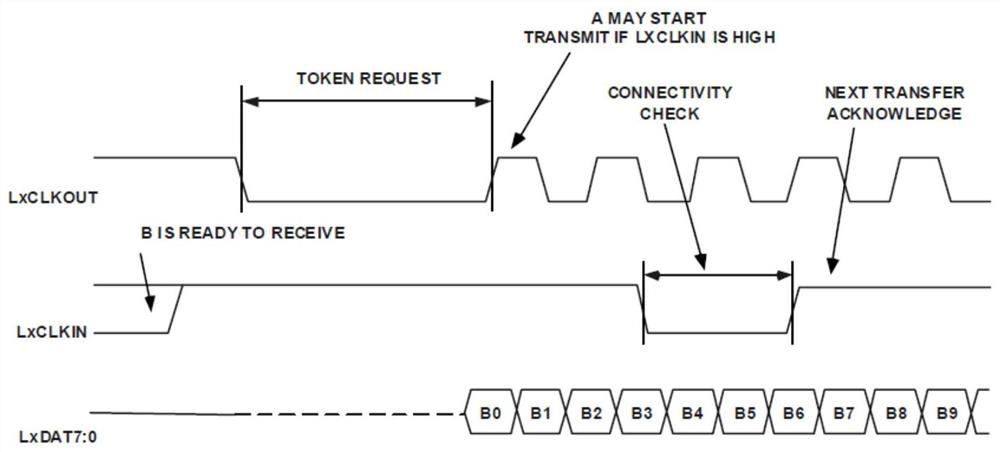

[0045] The present invention provides an FPGA-based LinkPort communication system, comprising: a sending module, a receiving module, a phase-locked loop circuit PLL connected to an external clock source, and the phase-locked loop circuit PLL is used to receive an external clock source and generate a bus input clock The 0° and 270° clocks have the same frequency, the 0° clock is used as the system clock, and the 270° clock is used to drive data output.

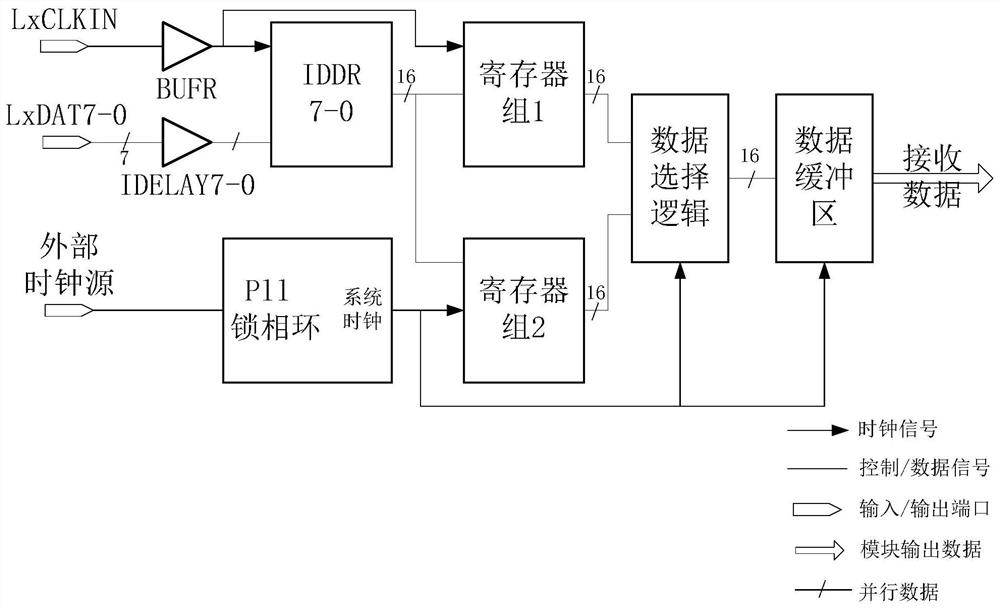

[0046] Such as image 3 As shown, the receiving module includes: a local clock buffer BUFR connected to the bus input clock LxCLKIN, a delay unit IDELAY connected to the bus data LxDAT, an IDDR circuit connected to the bus input clock LxCLKIN and the bus data LxDAT, and a phase-locked loop circuit The register group connected to the PLL and the IDDR circuit, and the data ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More