Current detection error compensation method and circuit in a voltage drop type power level circuit

A power stage circuit, current detection technology, applied in the direction of output power conversion devices, electrical components, etc., can solve the problem of inaccurate detection, and achieve the effect of accurate current excessive signal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

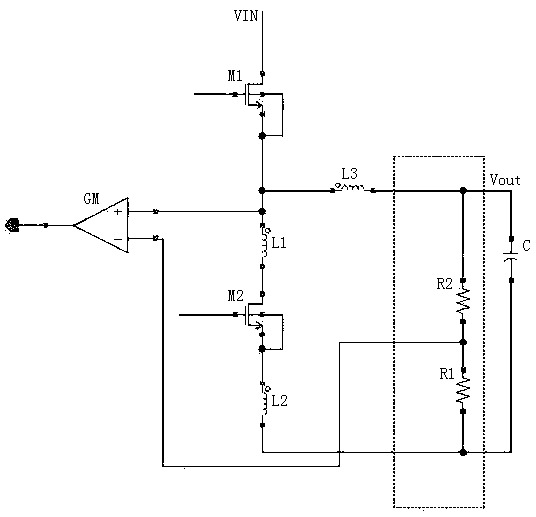

[0025] As an embodiment of the present invention, the offset voltage is the output regulation voltage of the step-down power stage circuit; after the output voltage of the step-down power stage circuit is detected and proportionally adjusted, it is fed back to the current sampling as a feedback signal The module; the proportional adjustment adjusts the sampled output voltage as an input signal to compensate and cancel the interference signal caused by the parasitic inductance on the power MOS device.

[0026] The offset is partial offset or full offset.

[0027] As an embodiment of the present invention, the ratio of the sampled output voltage is adjusted to be the ratio of the parasitic inductance to the sum of the inductances; the parasitic inductance is the sum of the parasitic inductances of the high-side and low-side MOS transistors; the sum of the inductances is high The sum of the parasitic inductance of the side MOS tube, the parasitic inductance of the low side MOS tu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More