Loading circuit and loading method for improving serial passive loading rate of FPGA

A loading circuit and passive loading technology, applied in the direction of electrical digital data processing, instruments, program control devices, etc., can solve time-consuming problems, achieve the effect of shortening loading time, reducing complex control process, and simple control program

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] Below in conjunction with accompanying drawing and specific embodiment the present invention will be described in further detail:

[0047] The invention provides a method suitable for fast loading FPGA by a satellite navigation processor. The satellite navigation processor sends a read command to the serial memory FLASH chip through the SPI interface, and controls the SPI interface to output the clock signal to realize the serial memory FLASH chip directly. Send the loaded data to the FPGA chip to complete the loading.

[0048] Satellite navigation processor is a multi-mode satellite navigation SoC dedicated chip, embedded with SPARC-V8 processor, operating frequency is 62MHz ~ 124MHz, peripheral interface includes chip design 1 I2C interface, 2 SPI interfaces, 1 IC card interface, a 16-bit wide GPIO interface, and 8 general-purpose serial ports, among which, the transmission rate of the SPI interface is 21MHz to 31MHz.

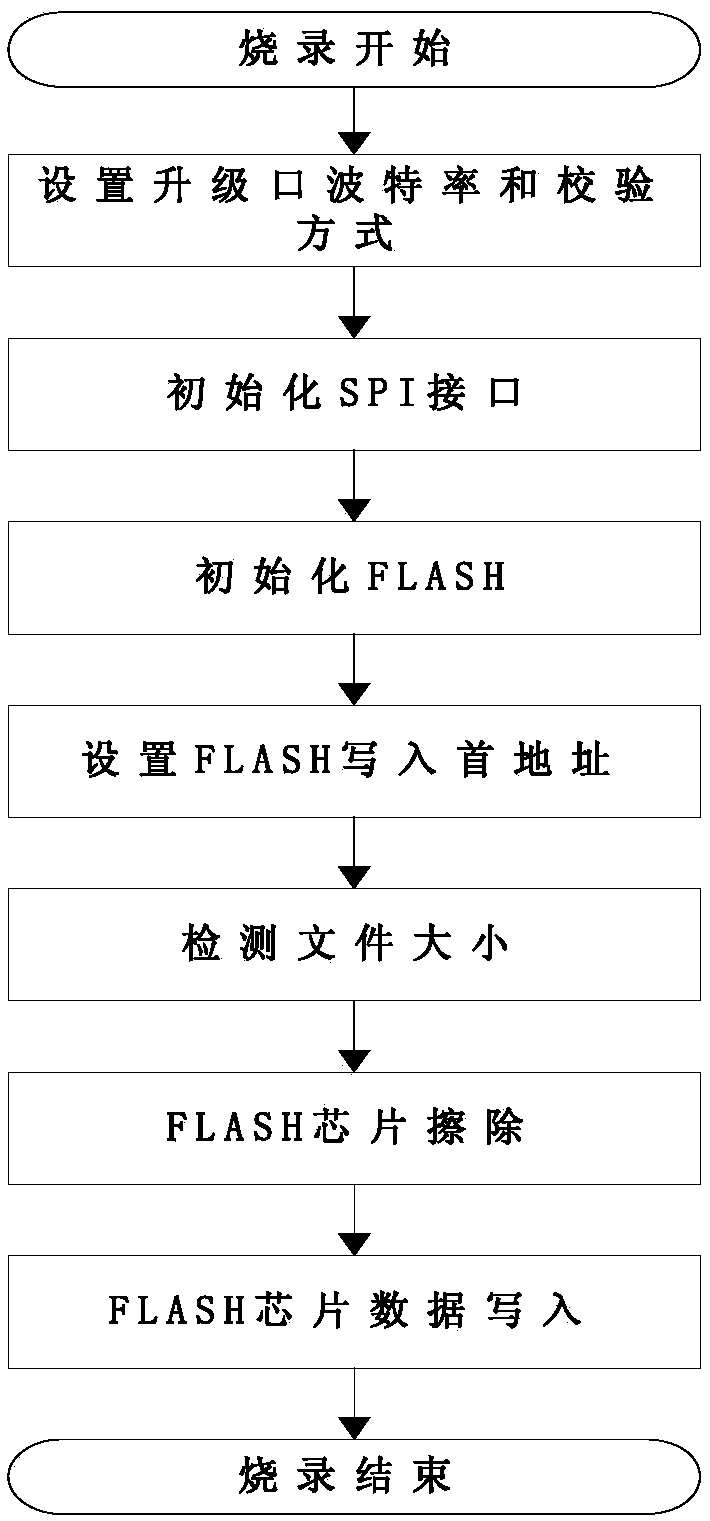

[0049] Such as figure 1 Shown, the present inv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com