Logic level conversion circuit and integrated circuit

A technology for converting circuits and logic levels, applied in the direction of logic circuit connection/interface layout, etc., can solve the problems of IO port damage, increase of bit error rate, communication failure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0022] The embodiment of the present invention proposes a logic level conversion circuit, so that the voltage of the level signal transmitted by the lower-level chip can match the working voltage of the upper-level chip, and the cascaded chips can work normally.

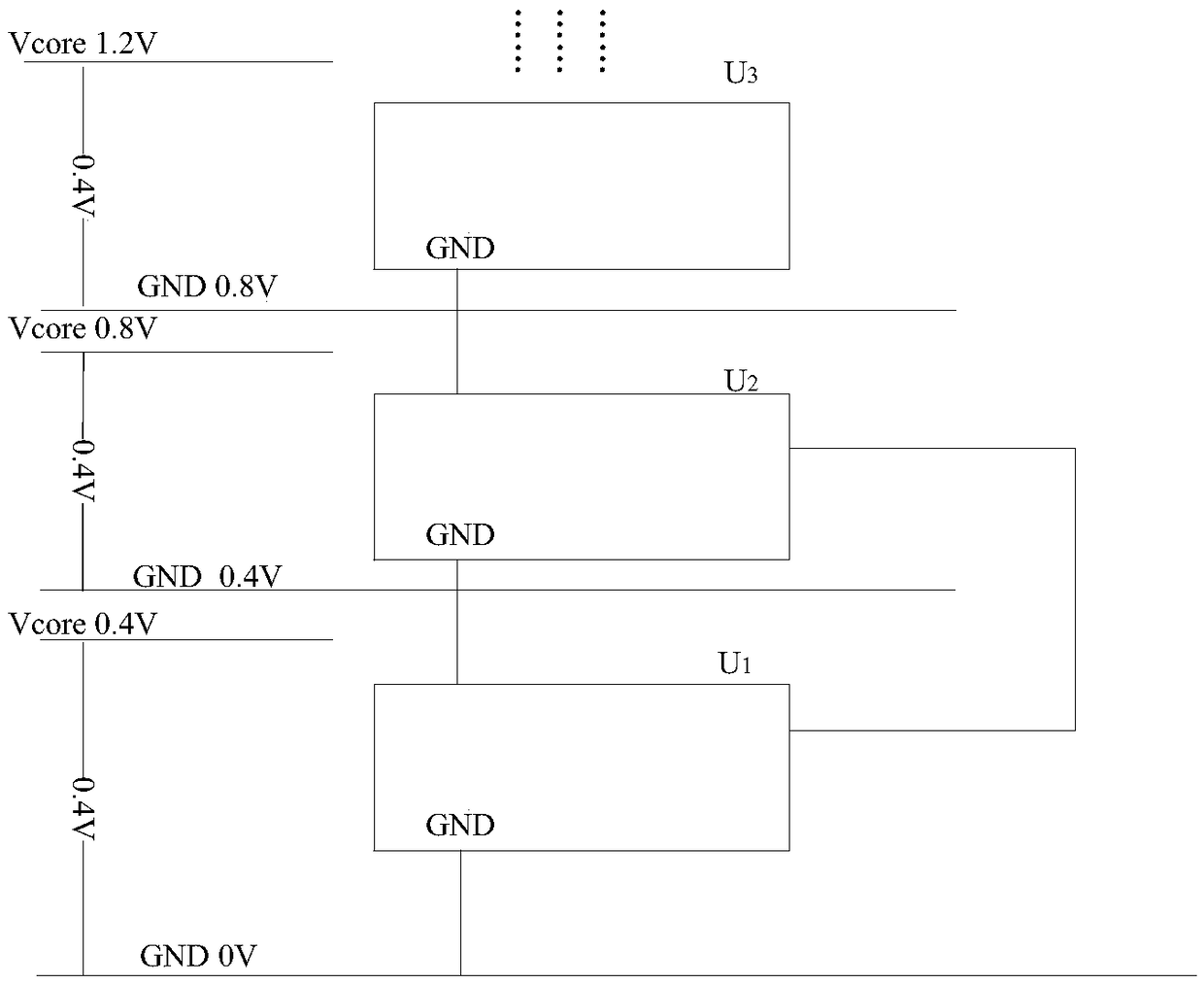

[0023] refer to figure 2 , shows a structural block diagram of an embodiment of a logic level conversion circuit of the present invention, the logic level conversion circuit of the embodiment of the present invention is applied to a cascaded chip, and the cascaded chip may include N-level chips connected in series, where N is an integer greater than 1.

[0024] In the embodiment of the present invention, the logic level conversion circuit is connected between the M-1th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More