A storage synchronization method of multi-channel acquisition system based on multi-FPGA

A multi-channel acquisition and system storage technology, which is applied in the field of high-speed acquisition system storage synchronization, can solve complex synchronization problems, achieve the effect of eliminating trigger shaking and saving pin resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

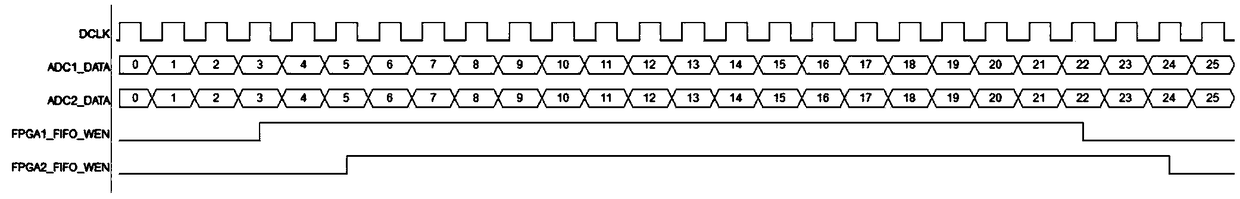

[0047]After the analog signal is quantized into a digital signal by the ADC, the waveform data needs to be stored. Usually, the FIFO (first-in-first-out) resource inside the FPGA is used as the buffer area for collecting data, and the read and write of the FIFO can be phased between different FPGAs. The relationship is random, so when the waveform is stored, due to the inconsistency of the read and write enable, the FIFO storage between different FPGAs is not synchronized.

[0048] The synchronized ADC sampling data is sent to the FPGA, and the asynchronous opening time of the FIFO write enable between different FPGAs will lead to asynchronous waveform storage.

[0049] figure 1 Among them, DCLK is the data clock after ADC synchronization, ADC1_DATA and ADC2_DATA are the sampling data after two ADCs are synchronized respectively, FPGA1_FIFO_WEN and FPGA2_FIFO_WEN are FIFO write enable in two FPGAs respectively, determined by figure 1 It can be seen that the synchronized sampl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More