Chip packaging structure, manufacturing method thereof and electronic equipment

A chip packaging structure and chip technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of large thickness of the chip packaging structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

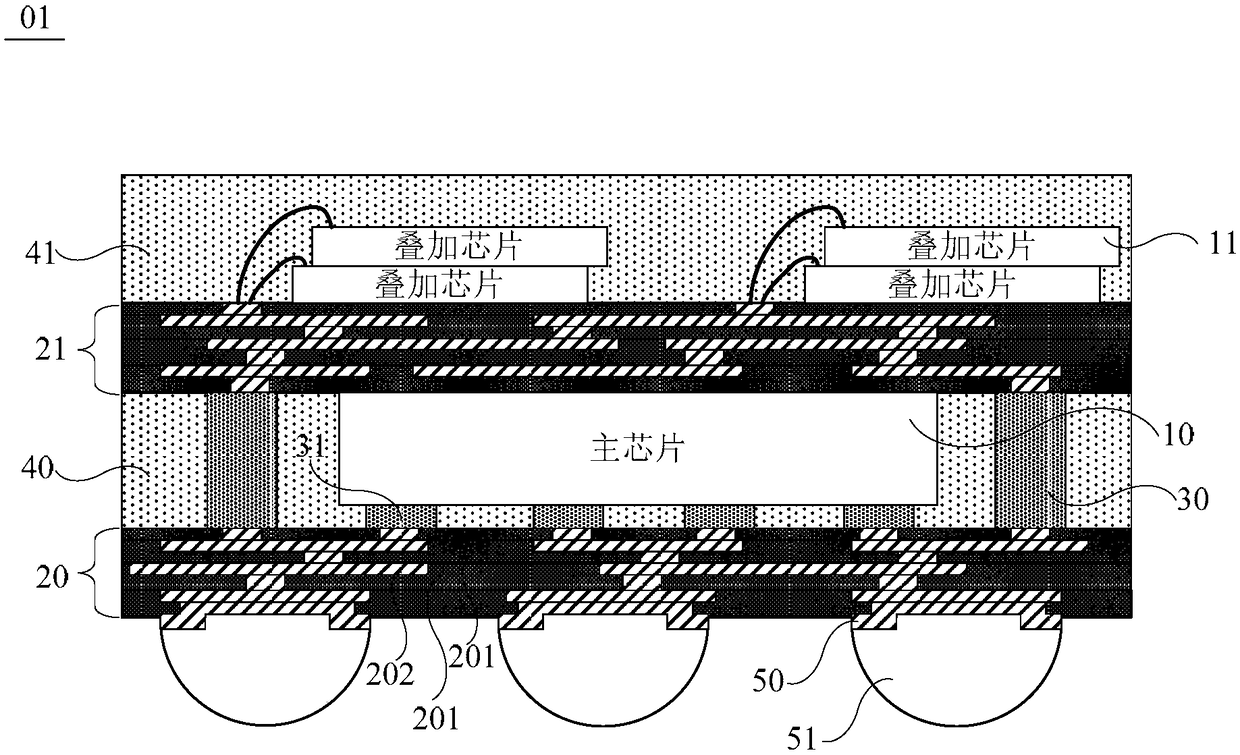

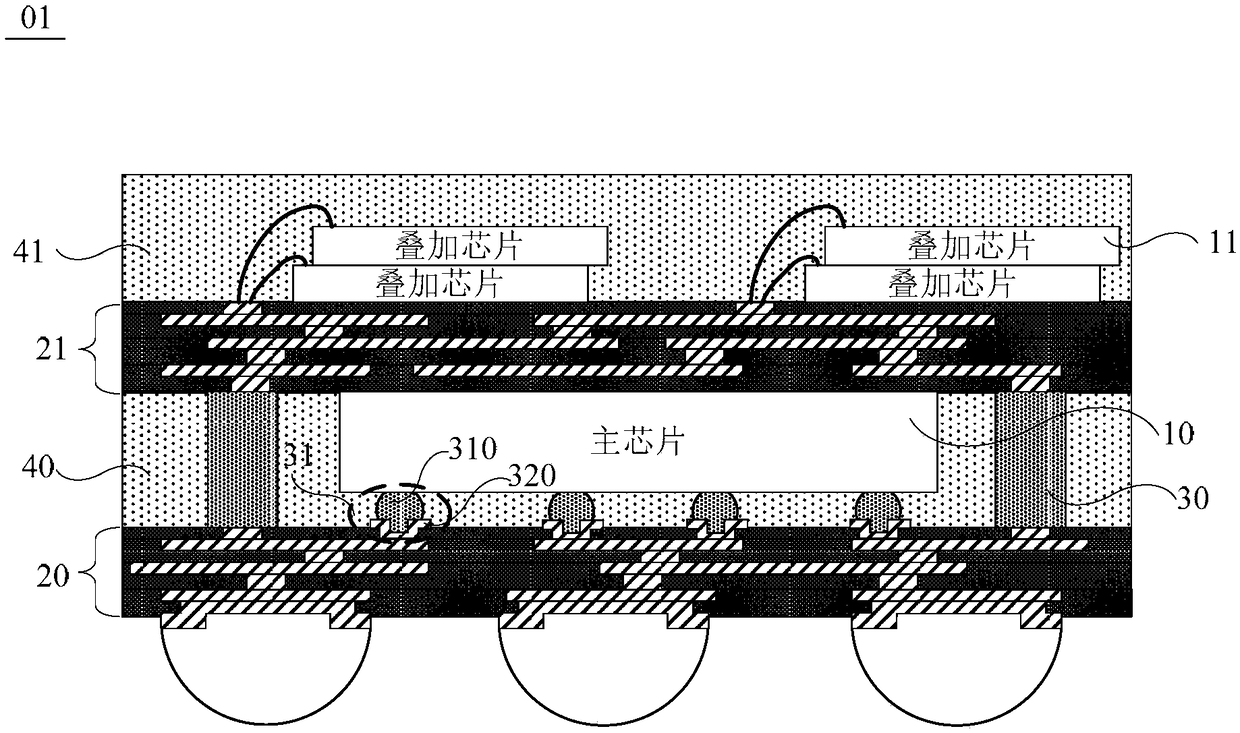

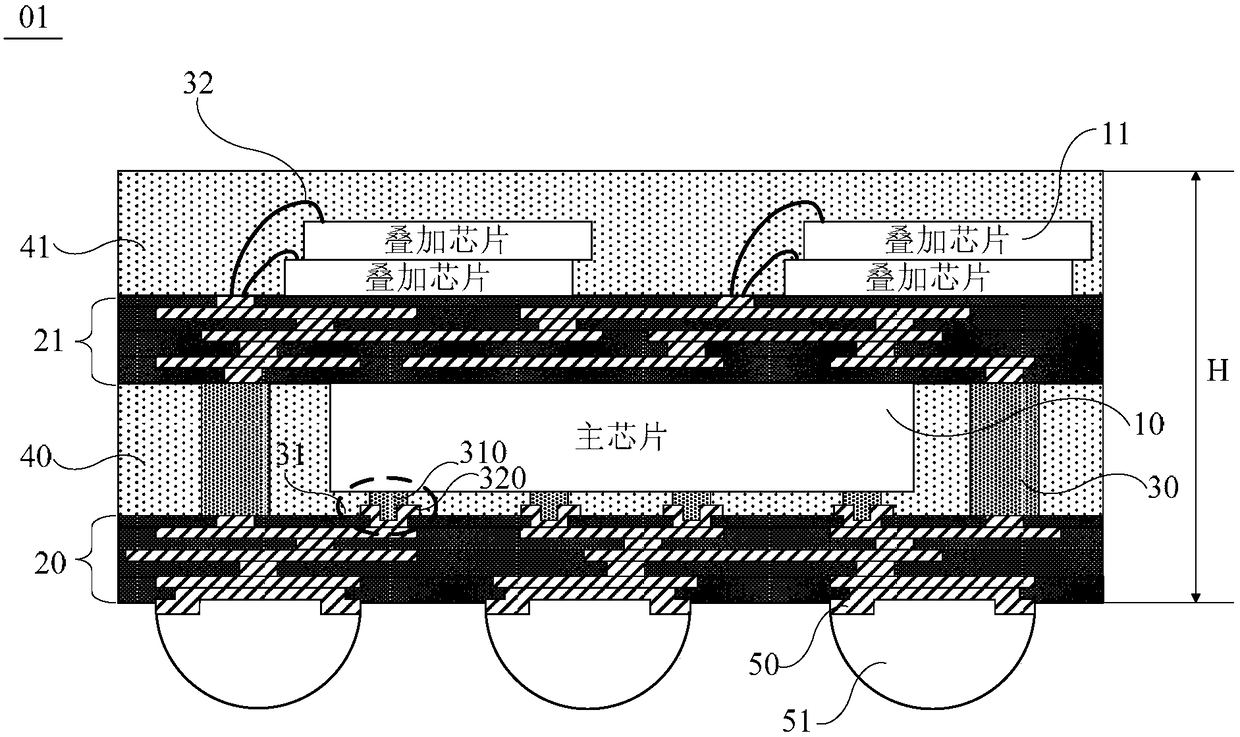

[0031] This application provides a chip packaging structure 01, such as figure 1 As shown, it includes: a main chip 10 , a first redistribution layer 20 , a second redistribution layer 21 , a first electrical connector 30 and an overlay chip 11 .

[0032] It should be noted that the present application does not limit the number of the above-mentioned main chips 10 and stacked chips 11 . In addition, the above-mentioned main chip 10 and stacked chip 11 generally have different functions. For example, the main chip 10 may be a logic chip, and the superimposed chip 11 may be a memory chip. In this case, when the above-mentioned chip package structure 01 has a plurality of logic chips serving as the main chips 10, the above-mentioned multiple main chips 10 may be located on the same plane and arranged at intervals. In this case, the above-mentioned first electrical connecting member 30 may or may not be provided between two adjacent main chips 10 . Those skilled in the art can ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More