Wafer processing method

A processing method and wafer technology, applied in metal processing equipment, manufacturing tools, machine tools suitable for grinding workpiece planes, etc., can solve problems such as poor productivity and time-consuming, and achieve the effect of simple alignment process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

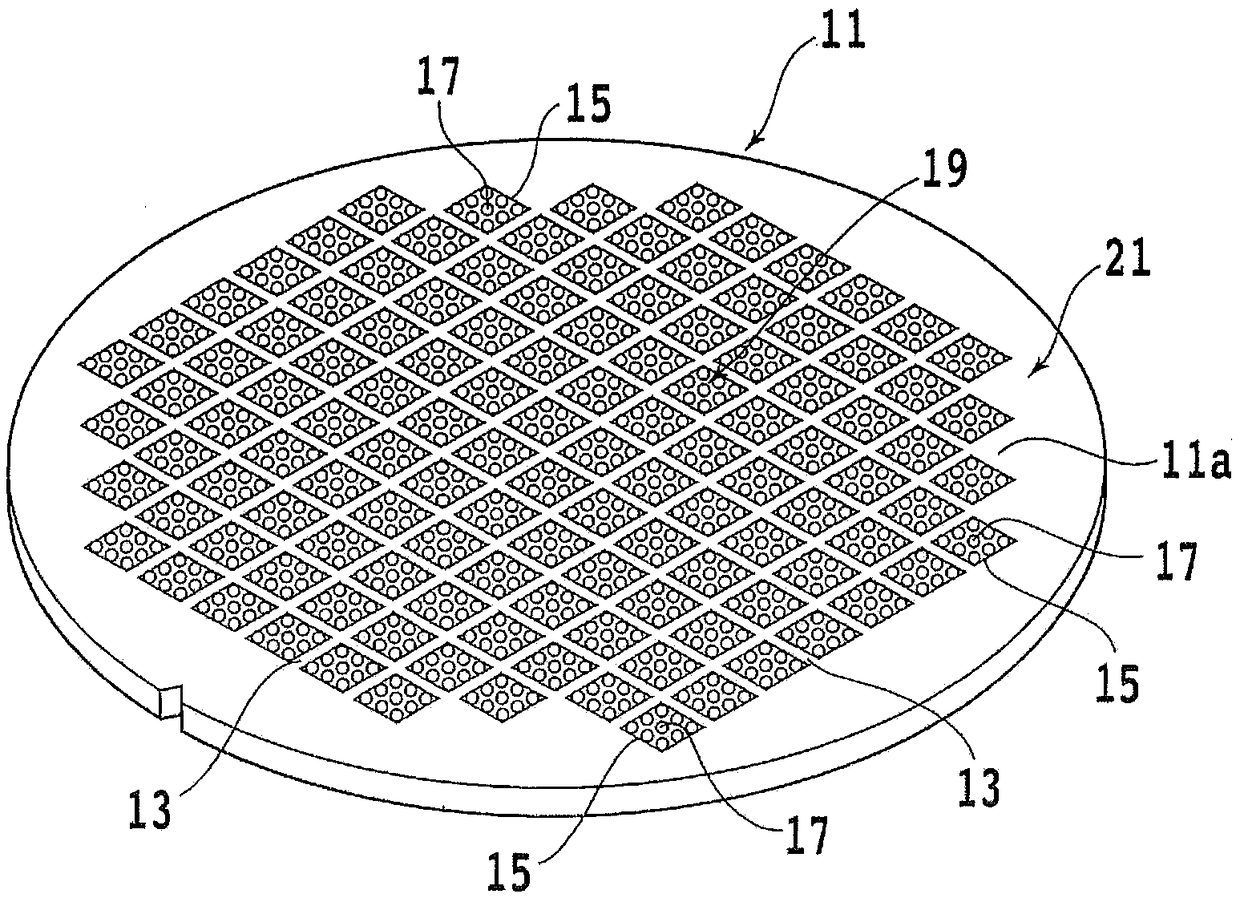

[0025] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. refer to figure 1 , shows a front perspective view of a semiconductor wafer (hereinafter, sometimes simply referred to as a wafer) 11 suitable for processing by the processing method of the present invention.

[0026] On the front surface 11 a of the semiconductor wafer 11 , a plurality of dividing lines (streets) 13 are formed in a grid pattern. Devices 15 such as ICs and LSIs are formed in each region partitioned by vertical dividing lines 13 .

[0027] There are a plurality of electrode bumps (hereinafter, sometimes simply referred to as bumps) 17 on the front surface of each device 15, and the wafer 11 has on its front surface: a device region 19, which is formed with a plurality of devices each having a plurality of bumps 17 15 ; and a peripheral remaining region 21 surrounding the device region 19 .

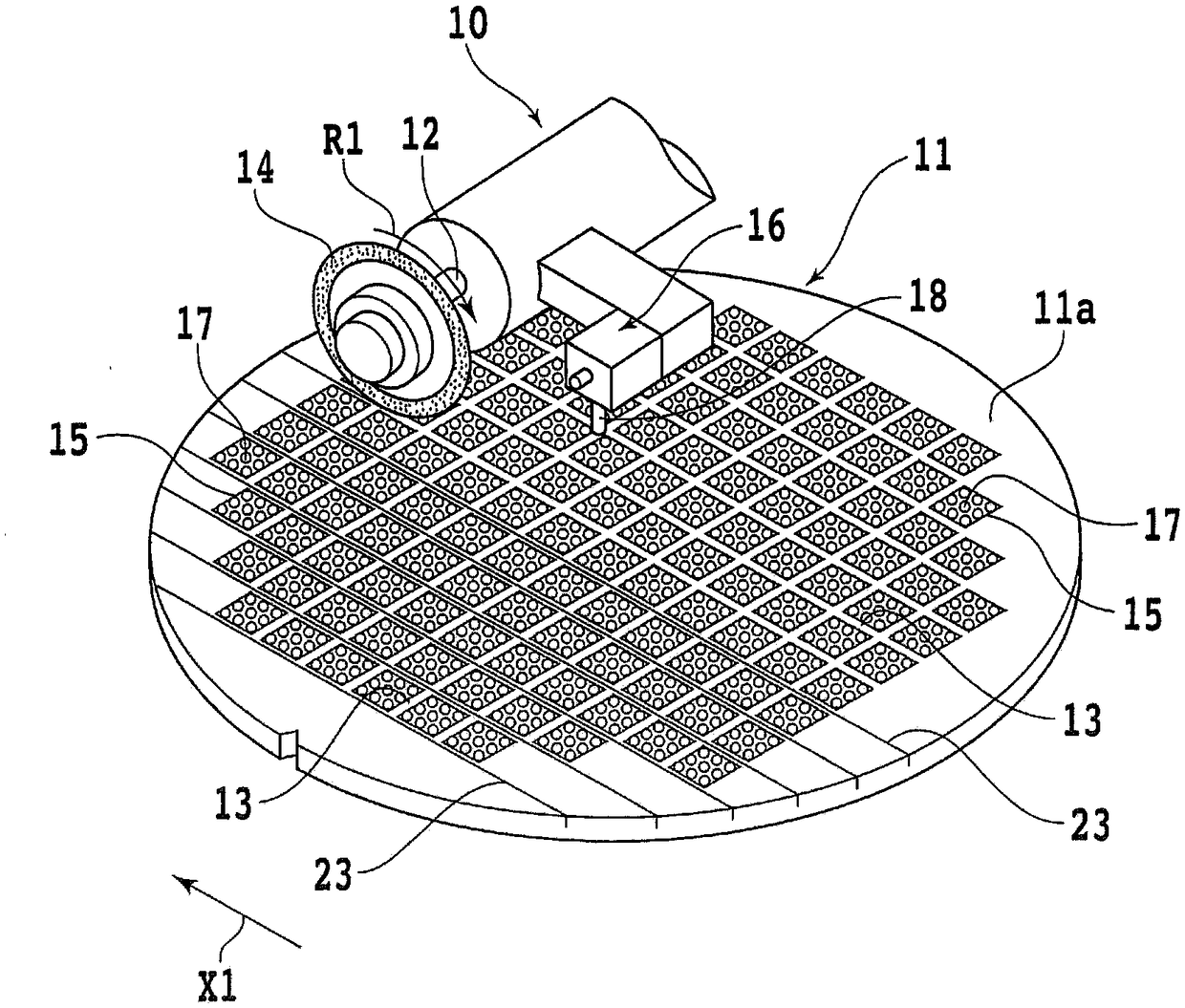

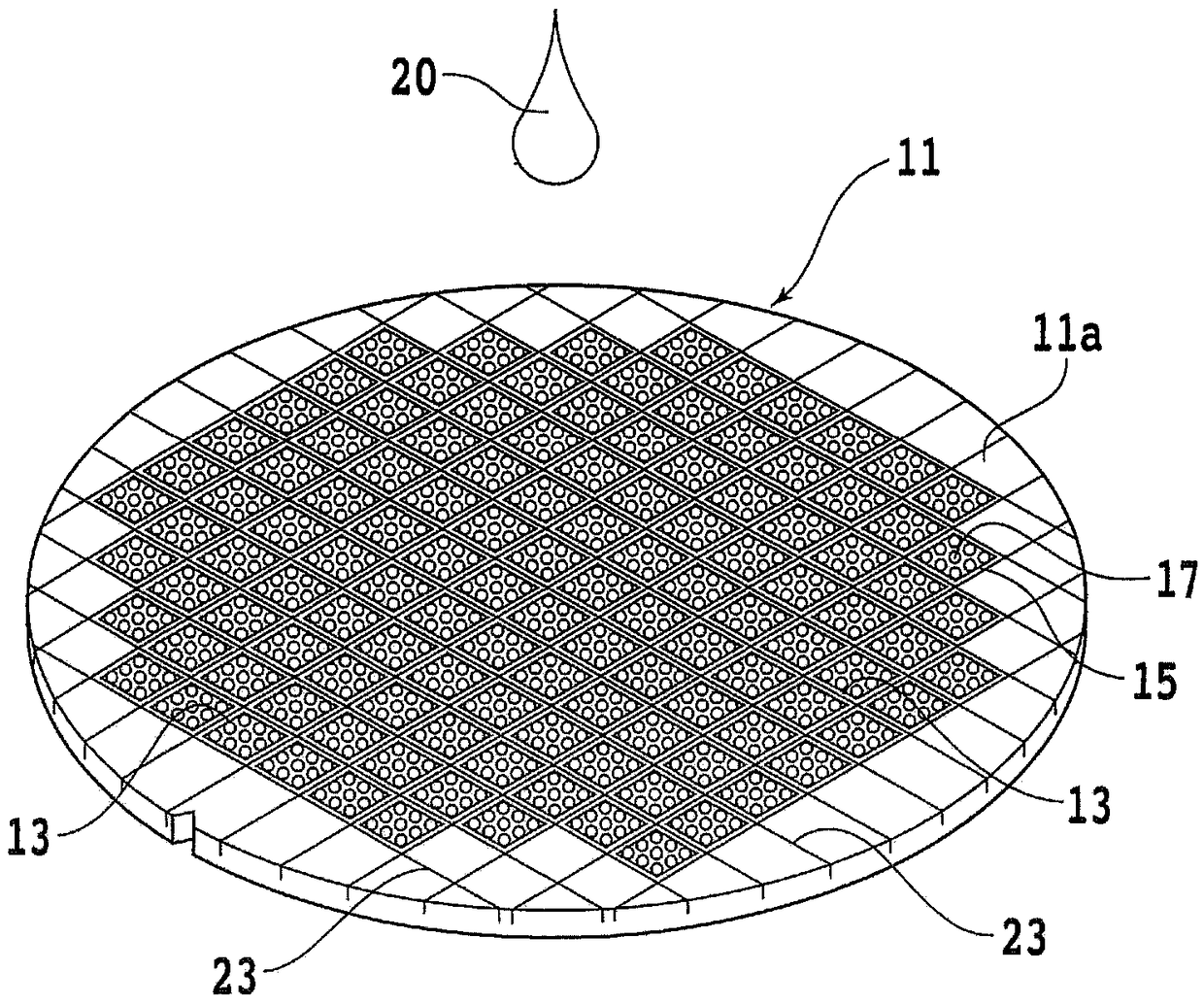

[0028] In the wafer processing method according to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com