Test system for System in Package (SiP) based on JTAG interface

A test system and interface technology, applied in the field of SiP packaging test systems, can solve problems such as high cost, complex test logic, and incompatibility with the JTAG protocol.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

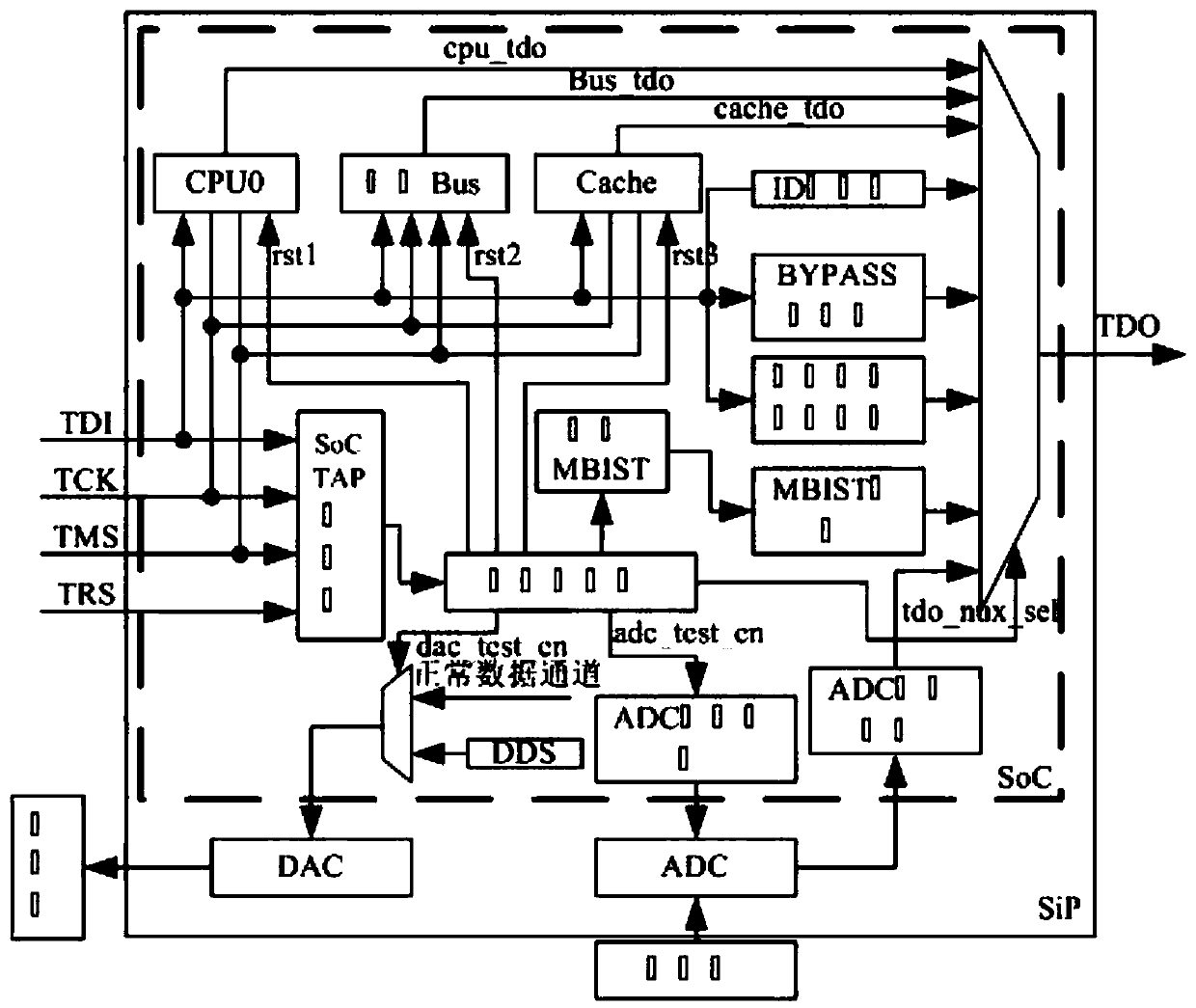

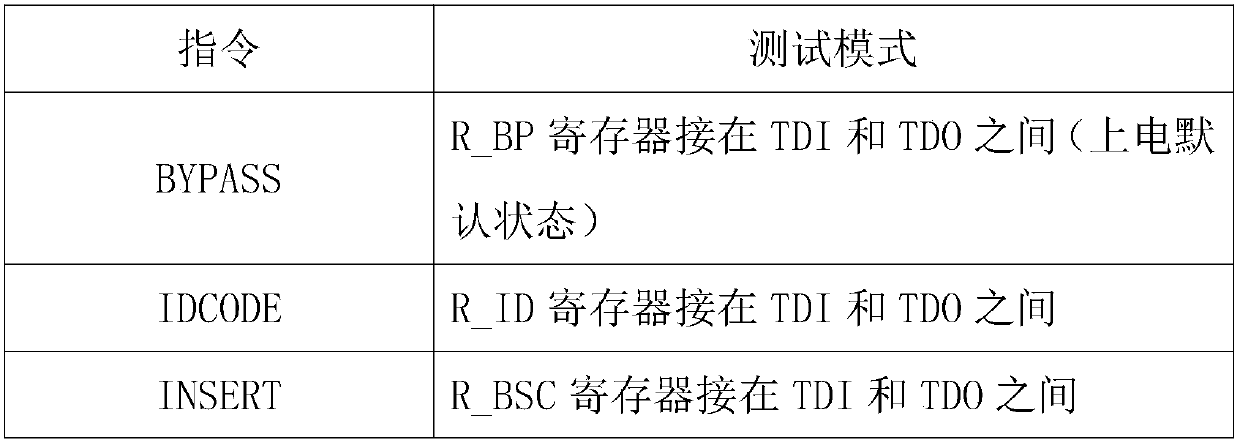

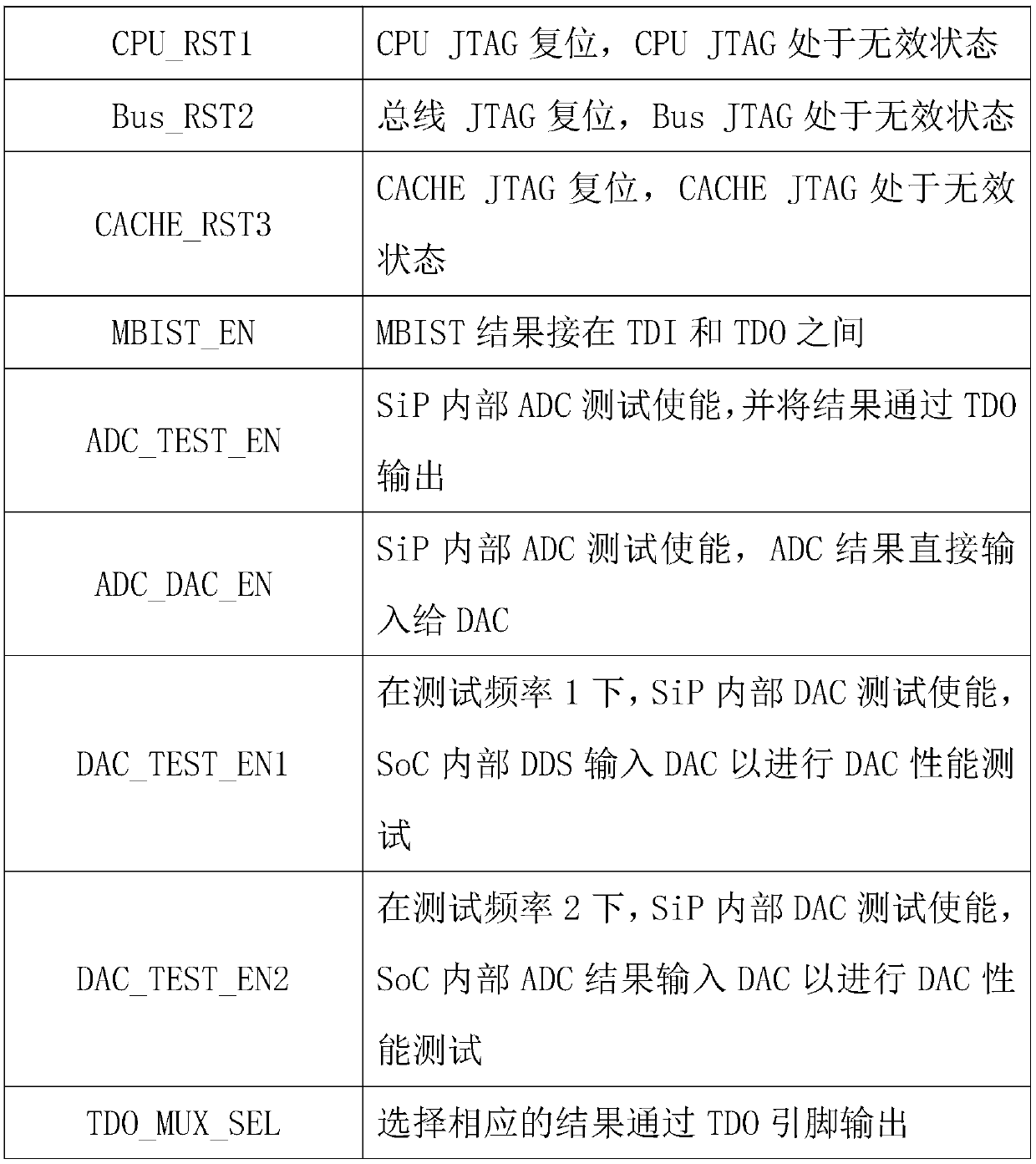

[0024] In order to achieve the purpose of the present invention, as figure 1 As shown, in one of the embodiments of the present invention, a test system for SiP packaging based on the JTAG interface is provided, including a JTAG interface, a SOC TAP controller, an instruction register, and a MUX module for TDO output. The JTAG The interface is electrically connected to the input end of the SOC TAP controller for controlling the SOC TAP controller, and the output end of the SOC TAP controller is electrically connected to the input end of the instruction register for sending the instruction of the SOC TAP controller to the instruction register, the output end of the instruction register is electrically connected to the input end of the MUX module for outputting the control signal of the corresponding test mode according to the instruction recei...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More