A function verification method and system applied to ahb bus matrix design

A functional verification and bus technology, applied in computer-aided design, special data processing applications, computing, etc., can solve the problems of low success rate of one-shot casting and insufficient verification, and achieve the effect of high efficiency and easy functional verification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to make the purpose, content, and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

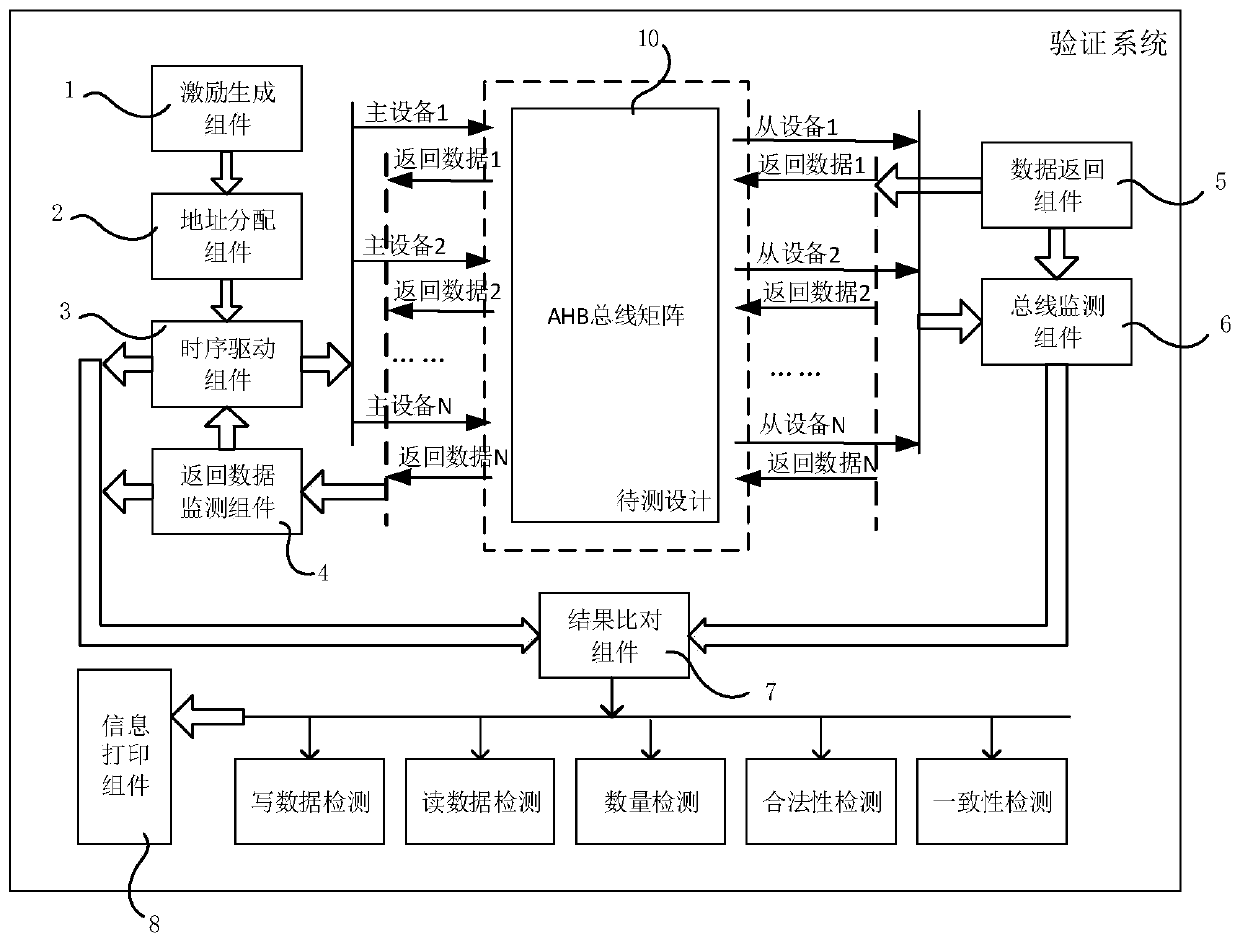

[0017] figure 1 Be applied to the block diagram of the functional verification system of AHB bus matrix design of the present invention, as figure 1 As shown, the functional verification system applied to AHB bus matrix design of the present invention includes: stimulus generation component 1, address assignment component 2, timing drive component 3, return data monitoring component 4, data return component 5, bus monitoring component 6, result Compare component 7 and AHB bus matrix 10.

[0018] Such as figure 1 As shown, the AHB bus matrix 10 is used as the design under test, and the master device is scheduled to access different slave devices in parallel to realize the routing function. The components of the verif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More