A method and a device for constructing an overturning counting model

A model and hierarchical model technology, applied in the field of information security, can solve problems such as inability to obtain intermediate values, characterization of combined circuit power consumption leakage, etc., to achieve the effect of strong pertinence and high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

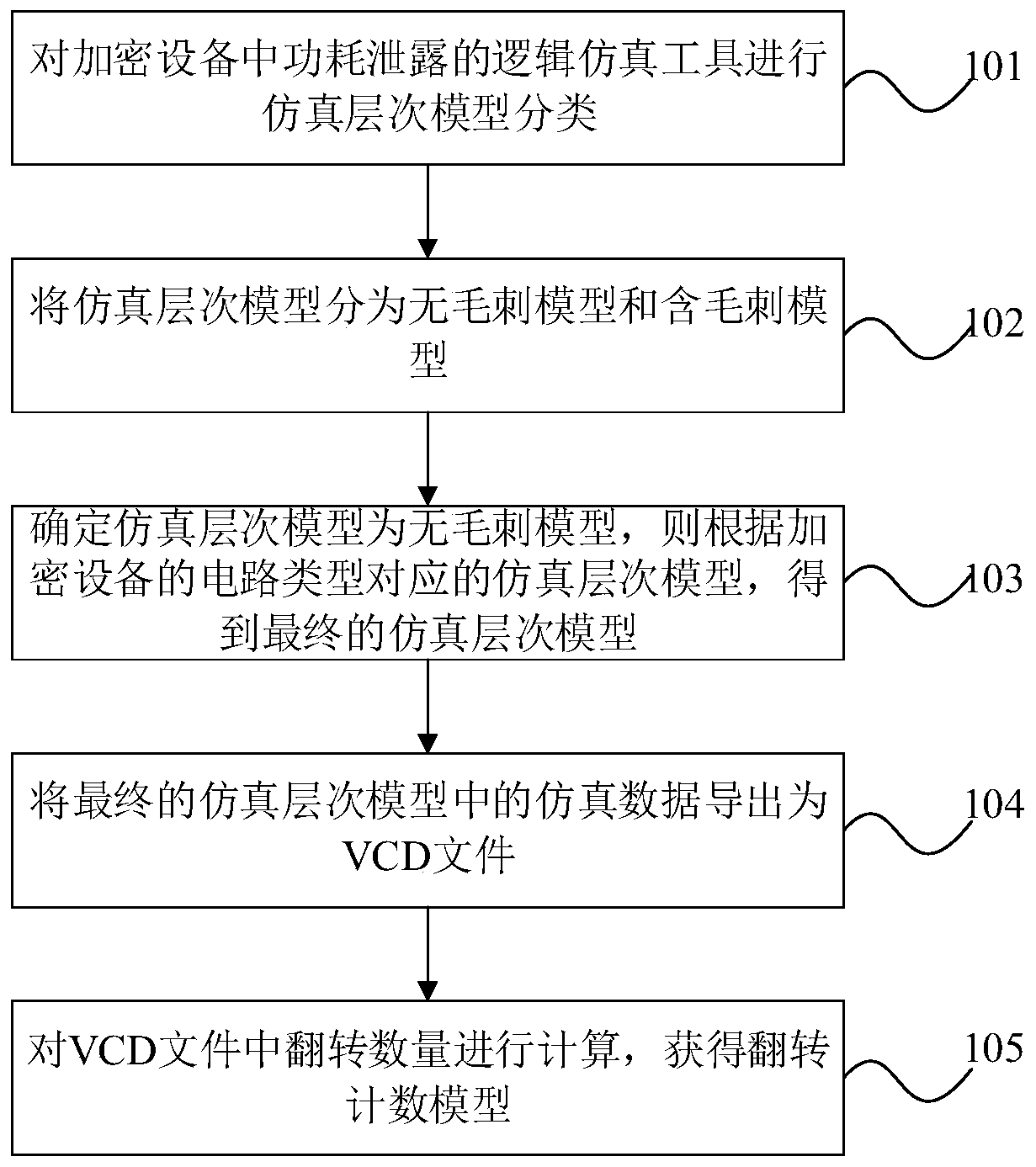

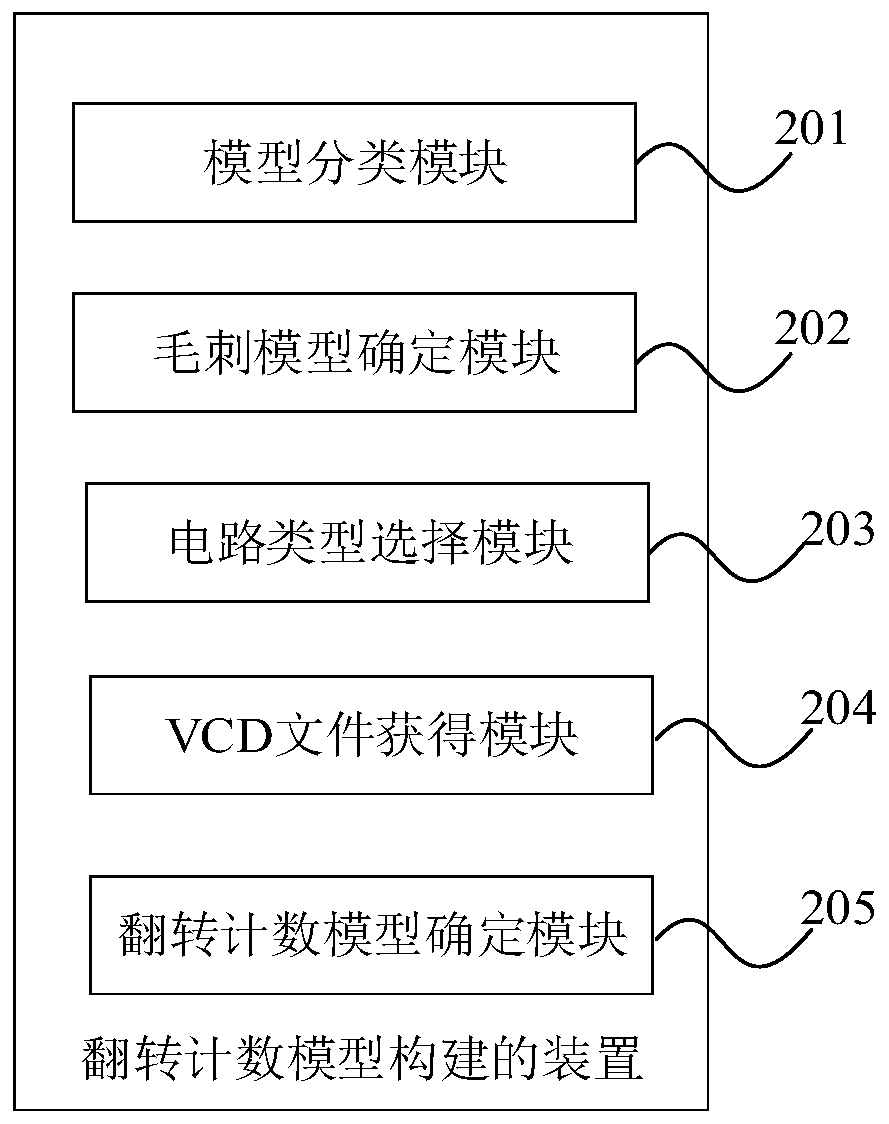

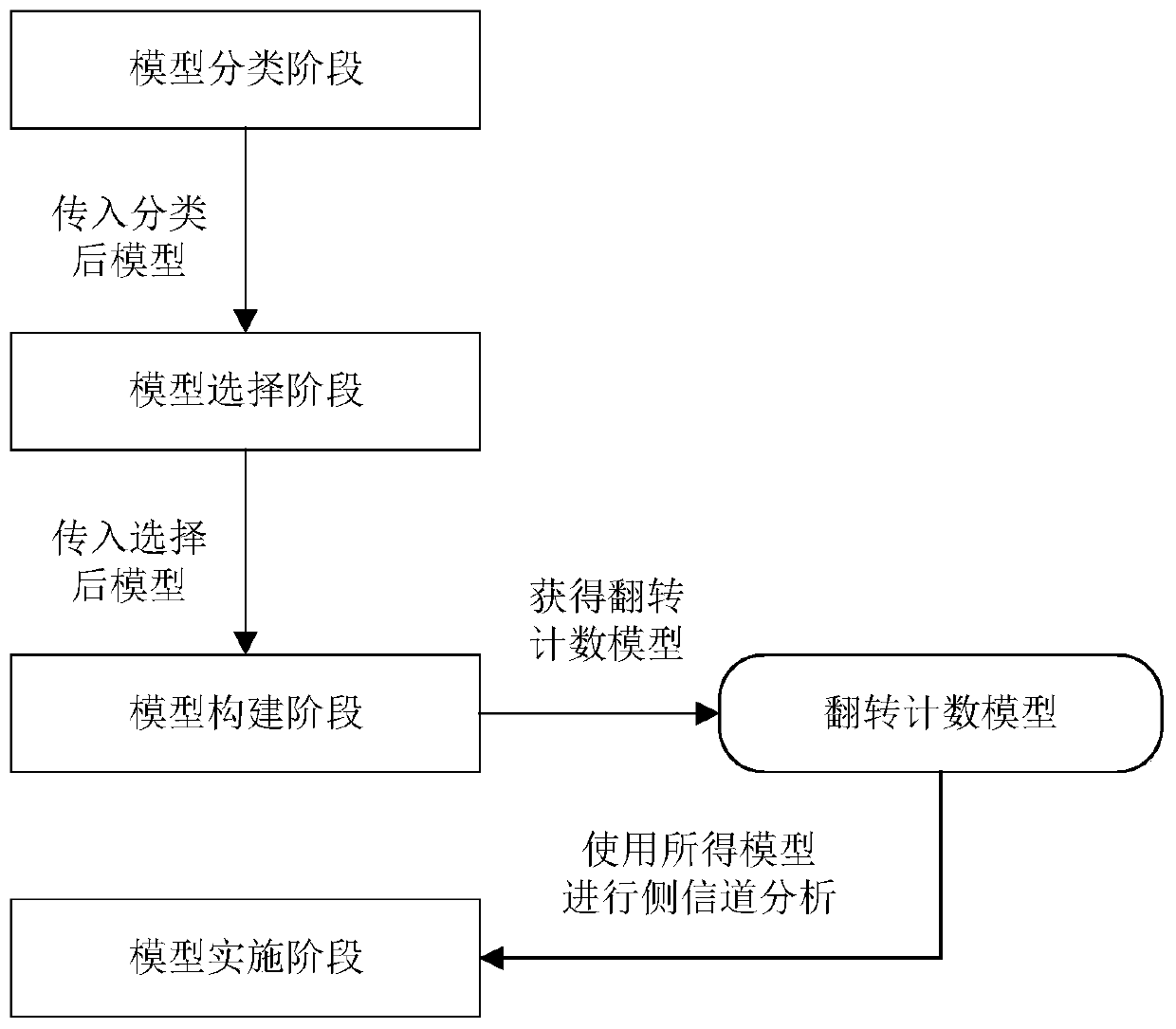

[0032] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0033] With the rapid development of information technology, the role of information security has become more and more important. One of the core technologies in the existing information security field is cryptography. From the various protocols of the computer network application layer to the various hardware devices in the communication system, cryptography plays a very important role. Existing encryption algorithms are mainly divided into two categories: s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More