Performance analysis method, device and equipment and storage medium

An analysis method and performance technology, applied in the field of chip performance analysis, can solve problems such as high professional requirements and the inability of comprehensive analysis by chip performance analyzers, and achieve the effect of comprehensive analysis, rational use, and overcoming single information

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

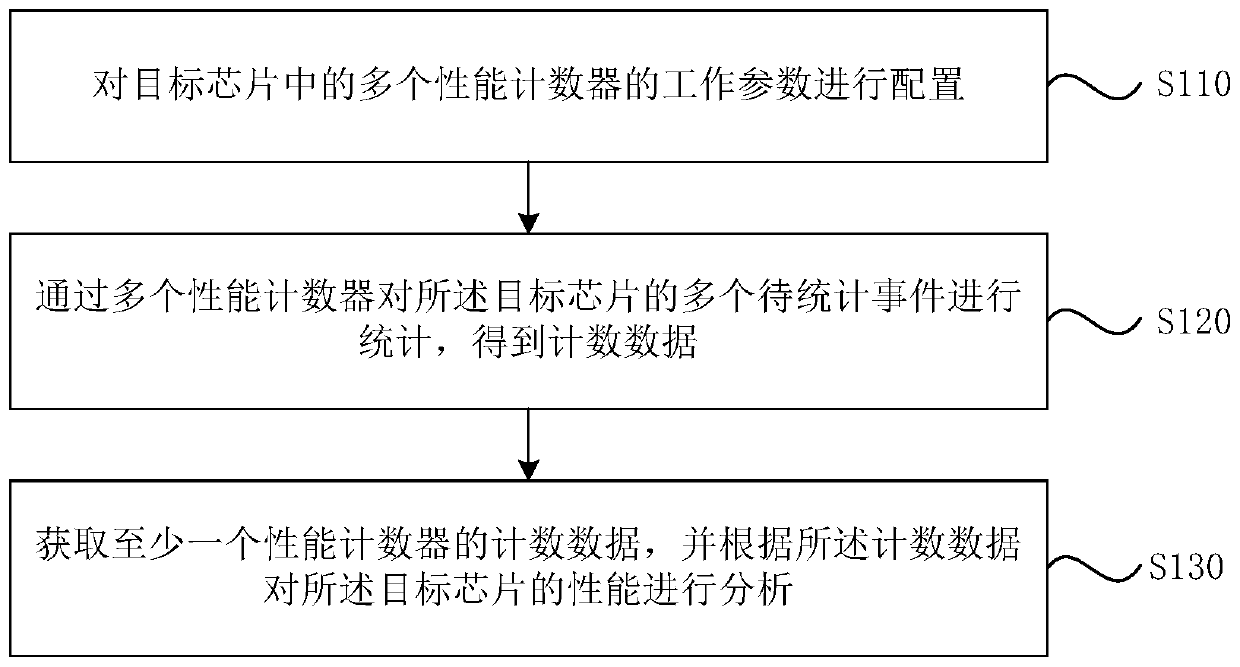

[0038] figure 1 It is a schematic flow chart of a performance analysis method provided by Embodiment 1 of the present invention. This embodiment is especially suitable for situations where a comprehensive analysis of chip performance is required. This method can be performed by a performance analysis device, which can be implemented by software and and / or hardware, and generally can be independently configured in a terminal or a server to implement the method of this embodiment.

[0039] Such as figure 1 As shown, the method in this embodiment may specifically include:

[0040] S110. Configure working parameters of multiple performance counters in the target chip.

[0041] In the embodiment of the present invention, the working parameters may include at least one of parameters such as working mode, counting start time, counting end time, events to be counted, and counting increase mode. Optionally, the working mode may include an independent counting mode or a parallel coun...

Embodiment 2

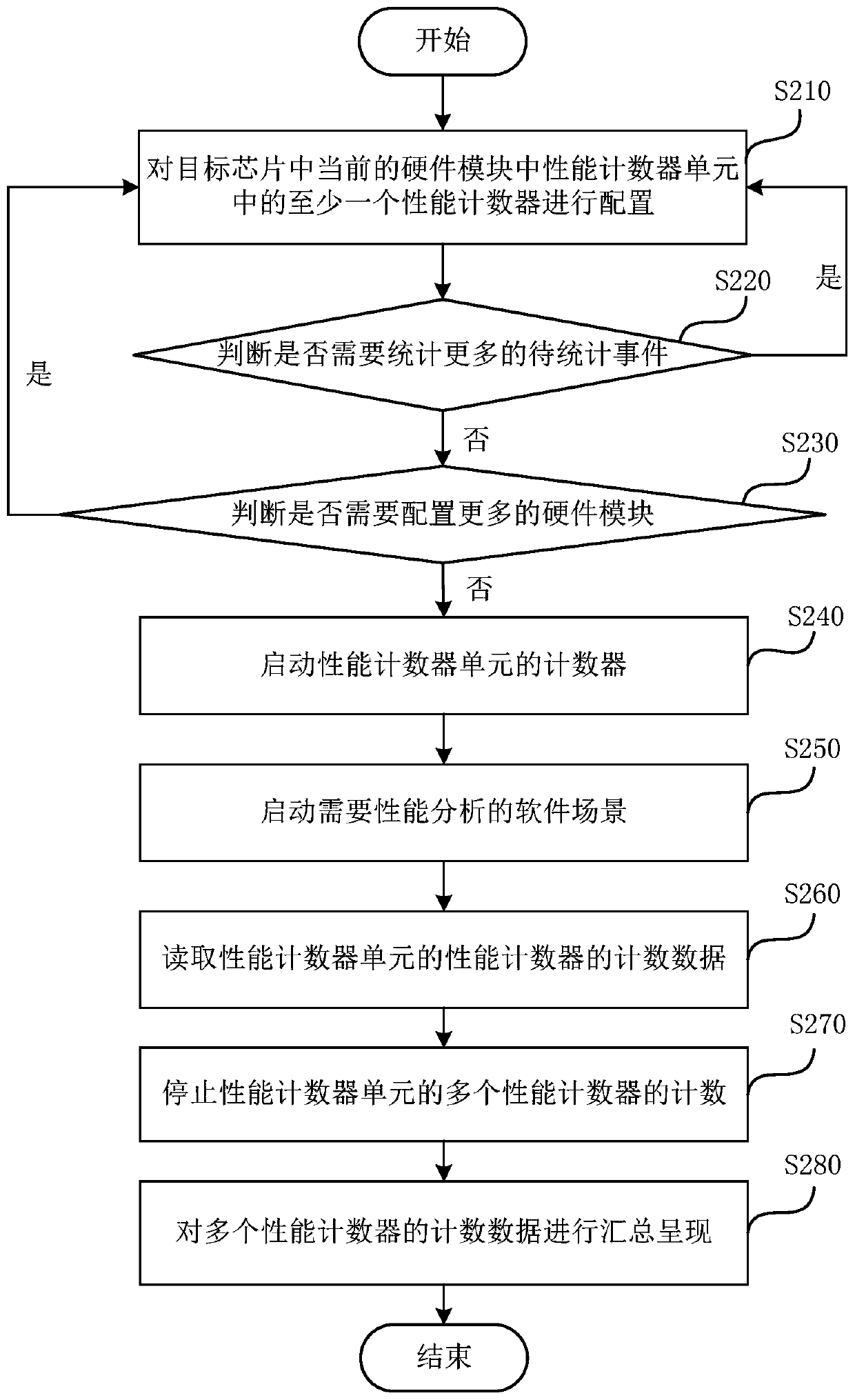

[0061] figure 2 It is a schematic flowchart of an optional example of a performance analysis method provided in Embodiment 2 of the present invention. like figure 2 As shown, the performance analysis method of this embodiment may specifically include:

[0062] S210. Configure at least one performance counter in the performance counter unit of the current hardware module in the target chip.

[0063] Wherein, the target chip includes multiple hardware modules. When configuring the performance counter, the performance counter unit of the hardware module can be used as a unit to configure one or more performance counters in the performance counter unit.

[0064] Configuring at least one performance counter in the performance counter unit in the current hardware module in the target chip includes: configuring the working parameters of each performance counter in the performance counter unit in the hardware module before configuring the hardware module according to the events t...

Embodiment 3

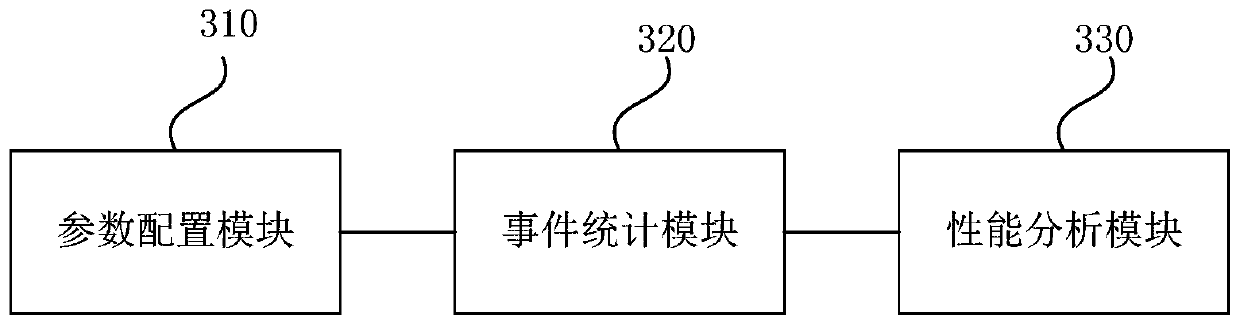

[0083] image 3 It is a schematic structural diagram of a performance analysis device provided in Embodiment 3 of the present invention. The performance analysis device of this embodiment is especially suitable for situations where a comprehensive analysis of chip performance is required. The device can be implemented by means of software and / or hardware. implementation, and generally can be independently configured in a terminal or server to implement the performance analysis method of the embodiment of the present invention. Such as image 3 As shown, the performance analysis device in this embodiment may include: a parameter configuration module 310 , an event statistics module 320 and a performance analysis module 330 .

[0084] Among them, the parameter configuration module 310 is configured to configure the working parameters of multiple performance counters in the target chip, wherein at least two performance counters in the multiple performance counters have a cascading...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More