self-adaptive high-speed SAR-ADC conversion time complete utilization circuit and method

A conversion time, adaptive technology, applied in code conversion, analog-to-digital converter, analog-to-digital conversion, etc., can solve the problems of reducing ADC speed and accuracy, short time, wasting area and power consumption, and reducing conversion errors. , high reliability, the effect of improving the conversion rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

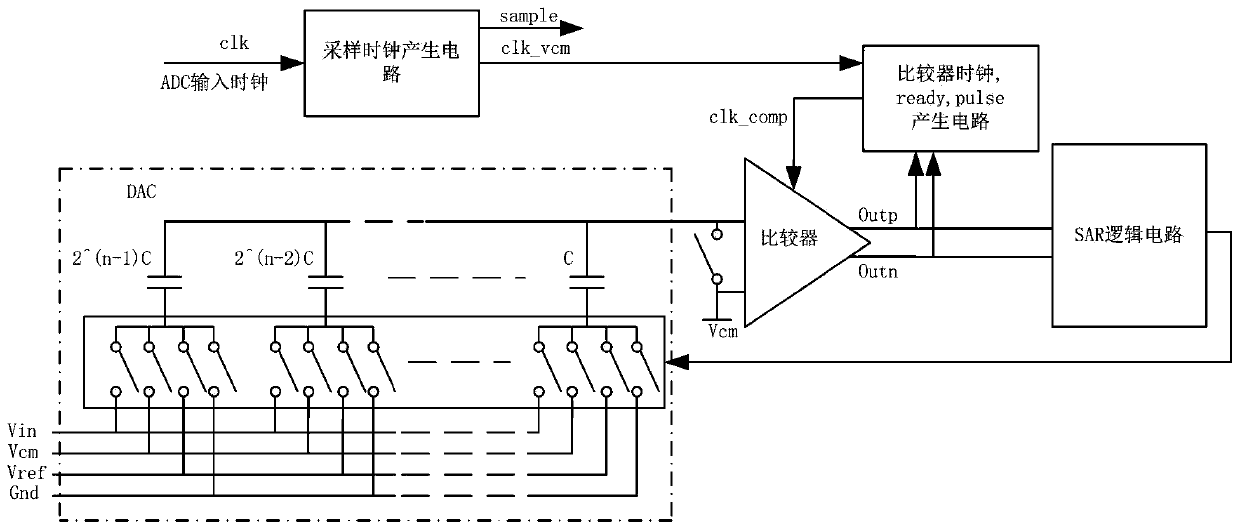

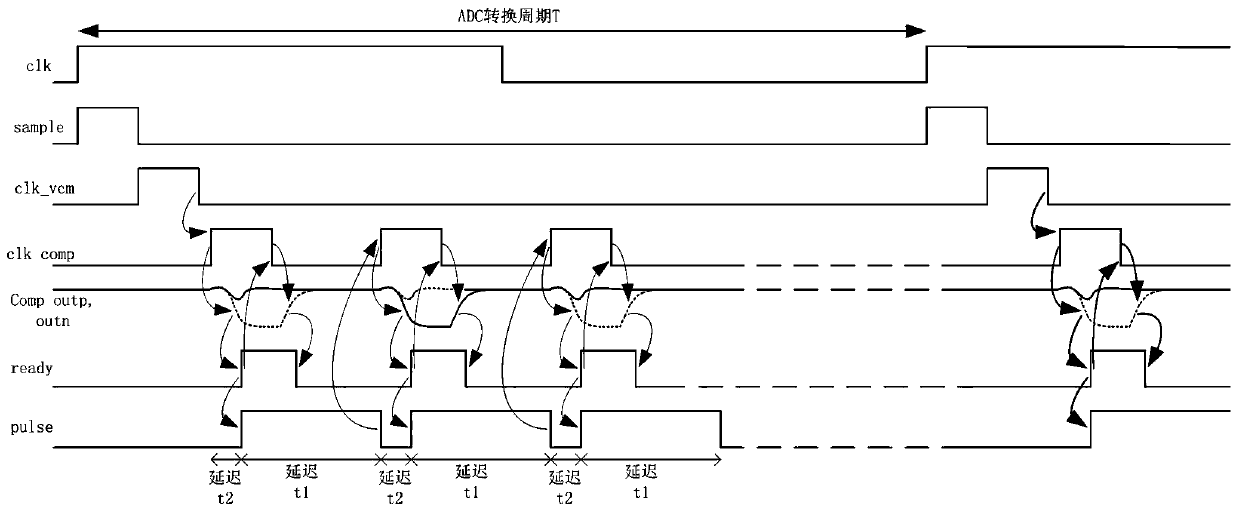

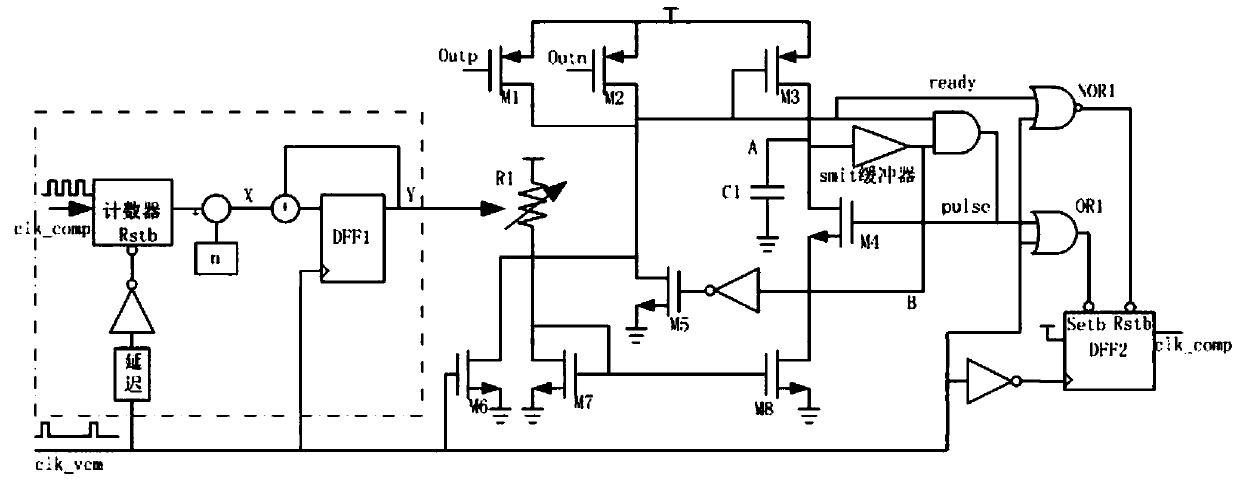

[0014] Common high-speed ADCs such as figure 1 As shown, the ADC is composed of DAC, comparator, SAR logic circuit, and clock generation circuit. The conversion process of the ADC is roughly divided into three steps. The first step is the sampling mode. After the ADC input clock clk arrives, when the sample is at a high level , the input signal is sampled to the lower plate of the capacitor array of the DAC, and the upper plate of the capacitor is connected to Vcm; the second step is to hold the mode, when clk_vcm is high, the upper plate is disconnected from Vcm, and the lower plate of the capacitor is connected to Vcm; The third step is the charge redistribution mode (comparison mode), the falling edge of clk_vcm generates the rising edge of the first comparison, such as figure 2 As shown in the ADC conversion timing of the comparator, the comparator starts to compare. According to the comparison result, Outp or Outn starts to fall, the clock generation circuit makes the re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More