Method for designing chip using embedded command

An embedded and embedded control technology, applied in computer-aided design, CAD circuit design, calculation, etc., can solve problems such as not allowing modification, achieve good practical performance, and save communication time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

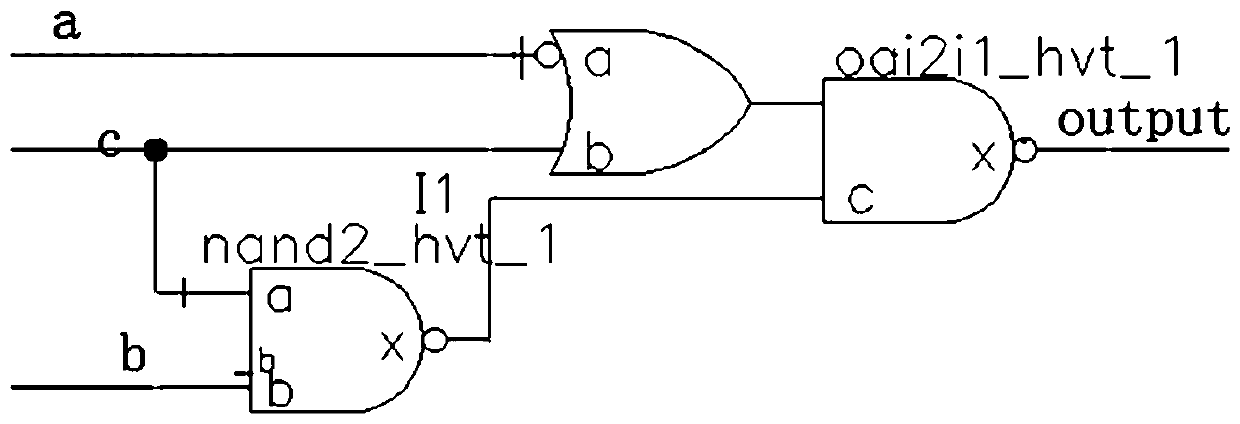

Image

Examples

Embodiment 1

[0047] A method for designing a chip using embedded commands. The method for designing a chip using embedded commands includes the following steps:

[0048] S1: Determine the code in top module1.rest_wrapper that needs to control the logic synthesis result;

[0049] S2: Add the embedded command to the top-level module, the embedded command contains the code label determined in S1, so as to achieve the purpose of controlling the logic synthesis tool;

[0050] S3: Read the code and design code containing embedded commands into CAD / EDA software;

[0051] S4: When the CAD / EDA software compiles embedded control statements, if you see the embedded control statements in the top-level module, it will automatically map the embedded control statements at the top-level to the modules that need to be controlled inside the module to control The synthesis tool completes the internal logic synthesis tool of the module according to the embedded control sentence.

Embodiment 2

[0053] A method for designing a chip using embedded commands. The method for designing a chip using embedded commands includes the following steps:

[0054] S1: Determine the code in top module1.rest_wrapper that needs to control the logic synthesis result;

[0055] S2: Add the embedded command to the top-level module, the embedded command contains the code label determined in S1, so as to achieve the purpose of controlling the logic synthesis tool;

[0056] S3: Read the code and design code containing embedded commands into CAD / EDA software;

[0057] S4: When the CAD / EDA software compiles embedded control statements, if you see the embedded control statements in the top-level module, it will automatically map the embedded control statements at the top-level to the modules that need to be controlled inside the module to control The synthesis tool completes the internal logic synthesis tool of the module according to the embedded control sentence. In step S3, the CAD / EDA software adds...

Embodiment 3

[0059] A method for designing a chip using embedded commands. The method for designing a chip using embedded commands includes the following steps:

[0060] S1: Determine the code in top module1.rest_wrapper that needs to control the logic synthesis result;

[0061] S2: Add the embedded command to the top-level module, the embedded command contains the code label determined in S1, so as to achieve the purpose of controlling the logic synthesis tool;

[0062] S3: Read the code and design code containing embedded commands into CAD / EDA software;

[0063] S4: When the CAD / EDA software compiles embedded control statements, if you see the embedded control statements in the top-level module, it will automatically map the embedded control statements at the top-level to the modules that need to be controlled inside the module to control The synthesis tool completes the internal logic synthesis tool of the module according to the embedded control sentence. In step S3, the CAD / EDA software adds...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com