Hardware acceleration method

A hardware acceleration and addition technology, applied in digital data processing components, instruments, electrical digital data processing, etc., can solve the problems of long task time, affecting the data transmission rate of the upper computer, and increasing the task cycle time of the airborne software. The effect of reducing task cycle time and resource overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

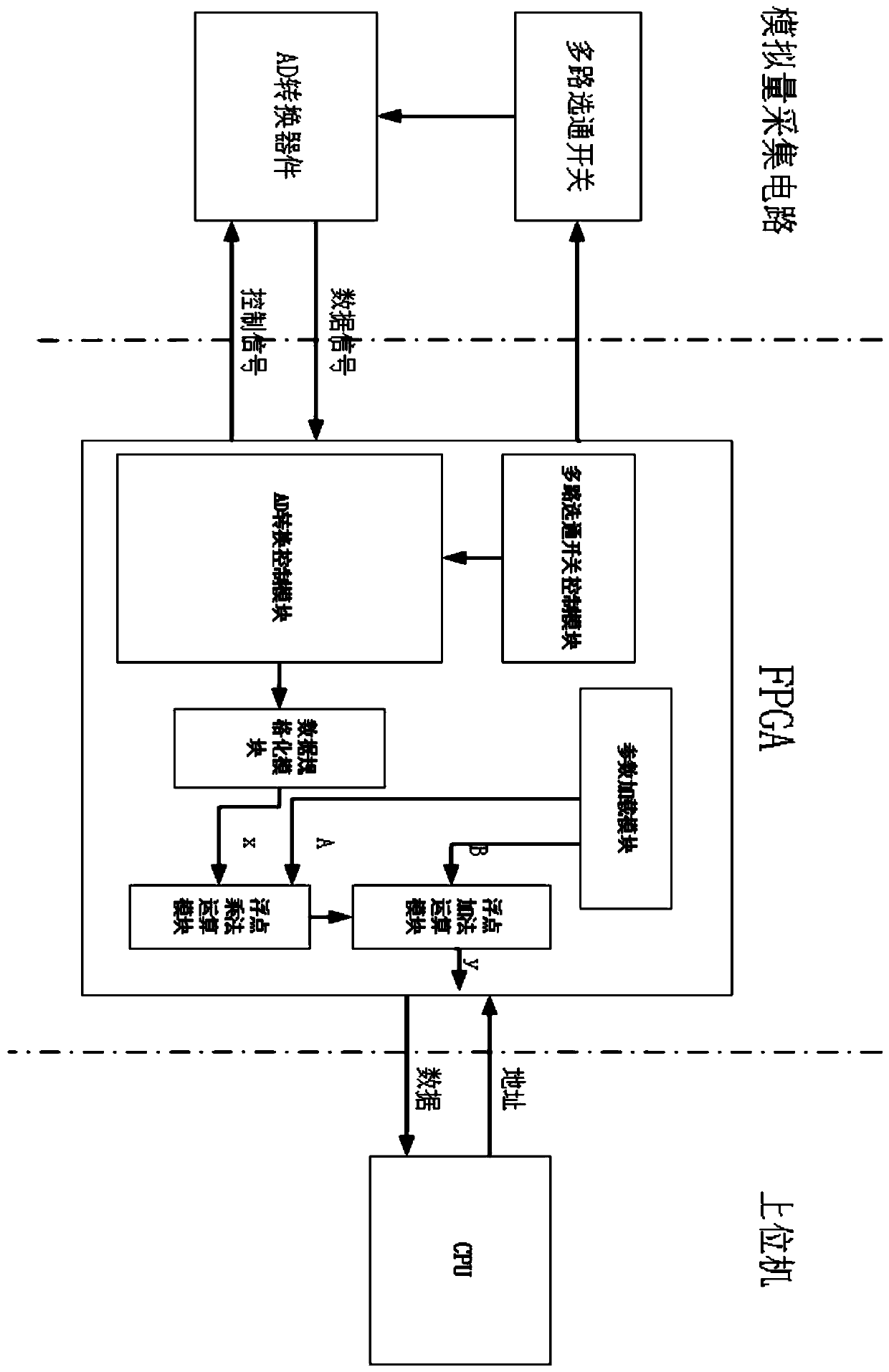

[0026] The technical solution of the present invention: a hardware acceleration method suitable for linear fitting of airborne products with more analog quantity acquisition, characterized in that: the method is implemented based on the architecture of FPGA+AD, specifically including analog quantity acquisition, Floating-point data normalization, linear fitting parameter loading, floating-point number multiplication and floating-point number addition are five parts. The five parts in the method are all implemented based on FPGA, and the purpose is to take advantage of the advantages that FPGA logic can perform parallel operations. Complete all analog acquisition results in the airborne product in an automatic cycle, and store the results in registers. The host computer software does not need to participate in the process of analog quantity acquisition and linear fitting operation, it only needs to read the data of the corresponding register when the analog quantity acquisition ...

Embodiment 2

[0034] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0035] figure 1 It is a structural block diagram of a linear fitting hardware acceleration method suitable for airborne products with many analog acquisitions. refer to figure 1 As shown, the method is implemented based on the architecture of FPGA+AD, and specifically includes five parts such as analog quantity acquisition, floating-point data normalization, linear fitting parameter loading, floating-point number multiplication and floating-point number addition, and five parts in the method Each part is implemented based on FPGA, the purpose is to take advantage of the parallel operation of FPGA logic, automatically complete all the analog acquisition results in airborne products, and store the results in registers. The host computer software does not need to participate in the process of analog quantity acquisition and linear fitting operat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More