FPGA for high-capacity data and opencl-based FPGA algorithm

A large-capacity, data technology, applied in the field of data computing, can solve problems such as large time resources, inability to calculate algorithms, reduce the utilization rate of kernel algorithms, etc., to achieve the effect of acceleration effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

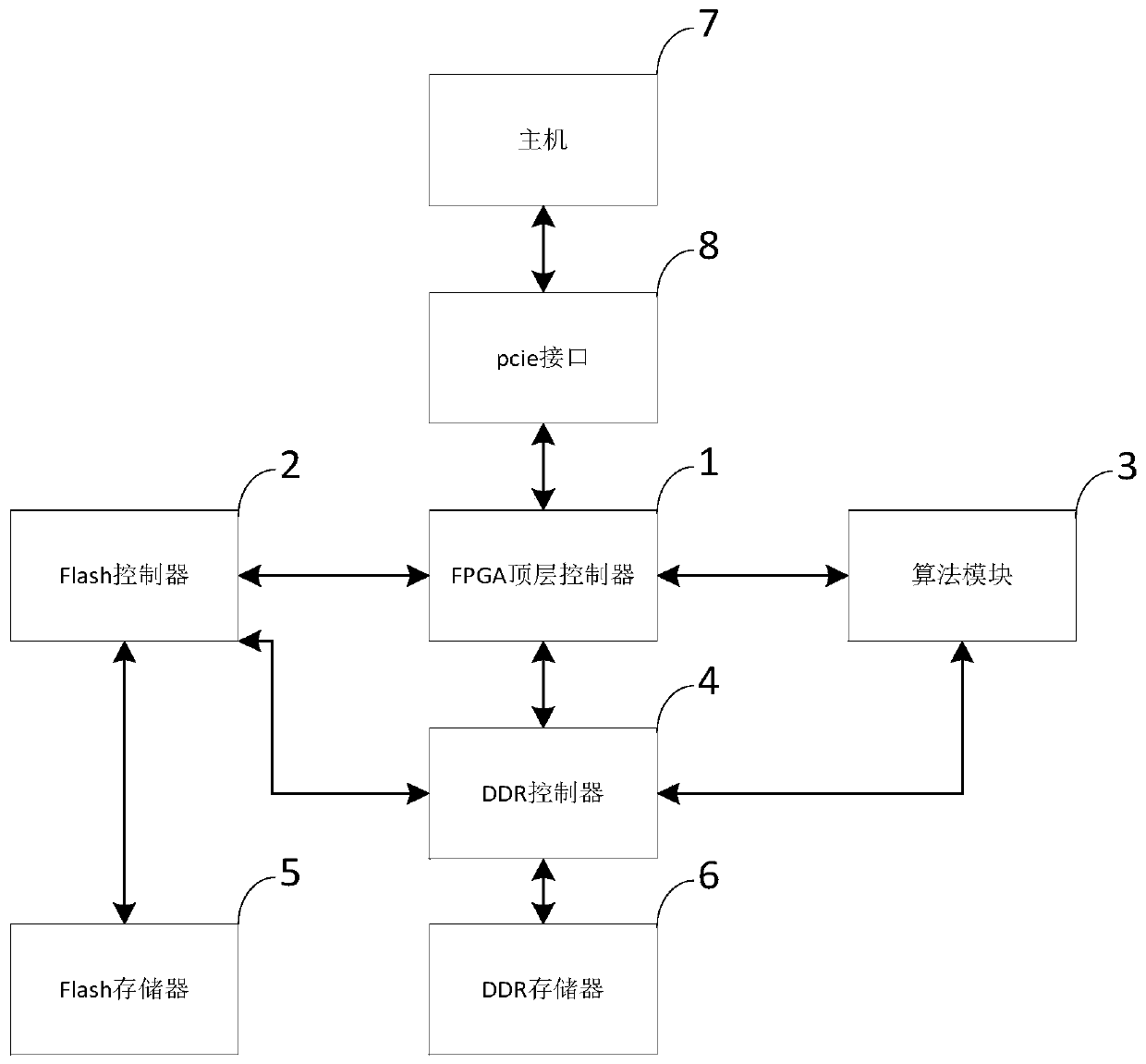

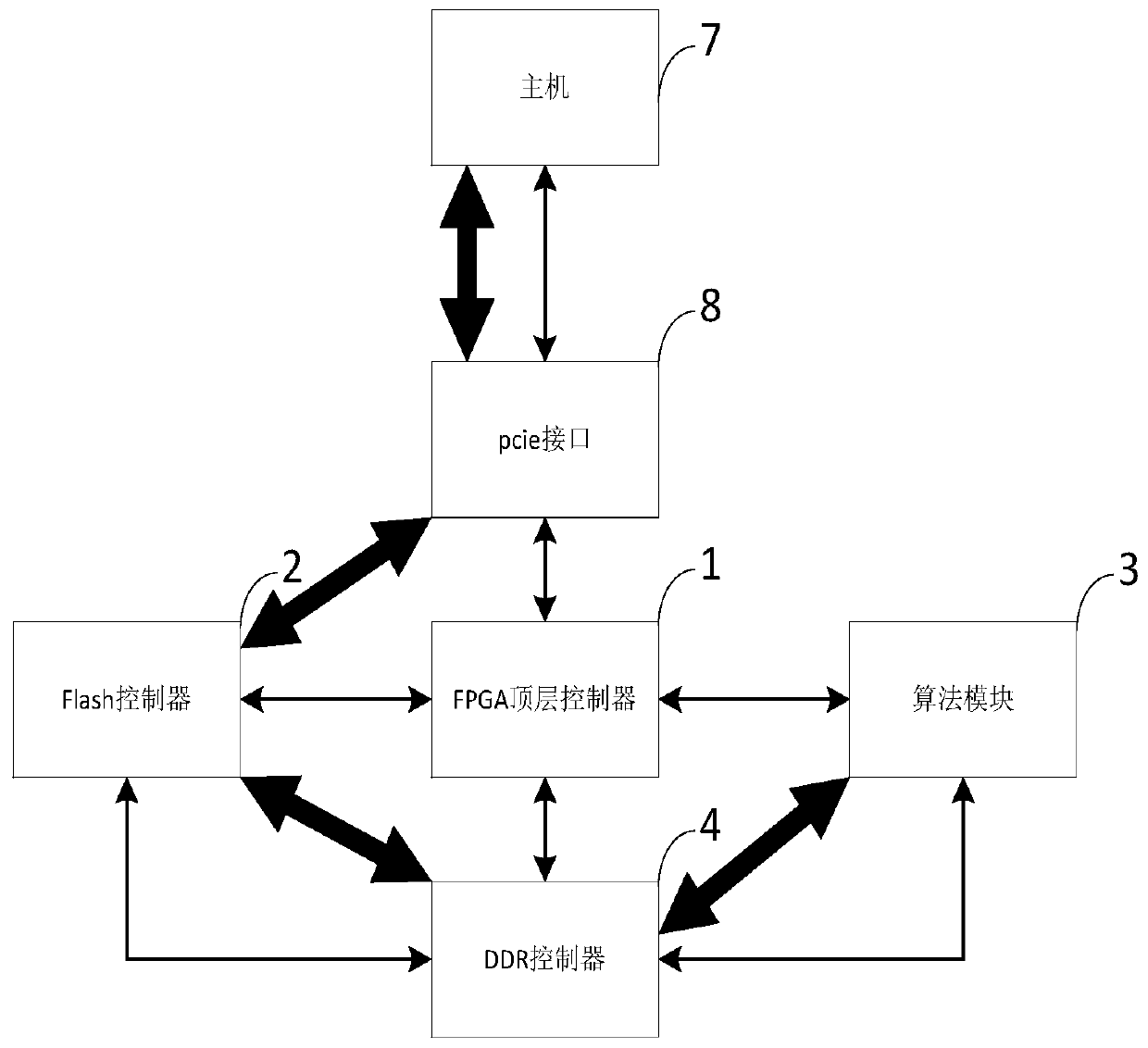

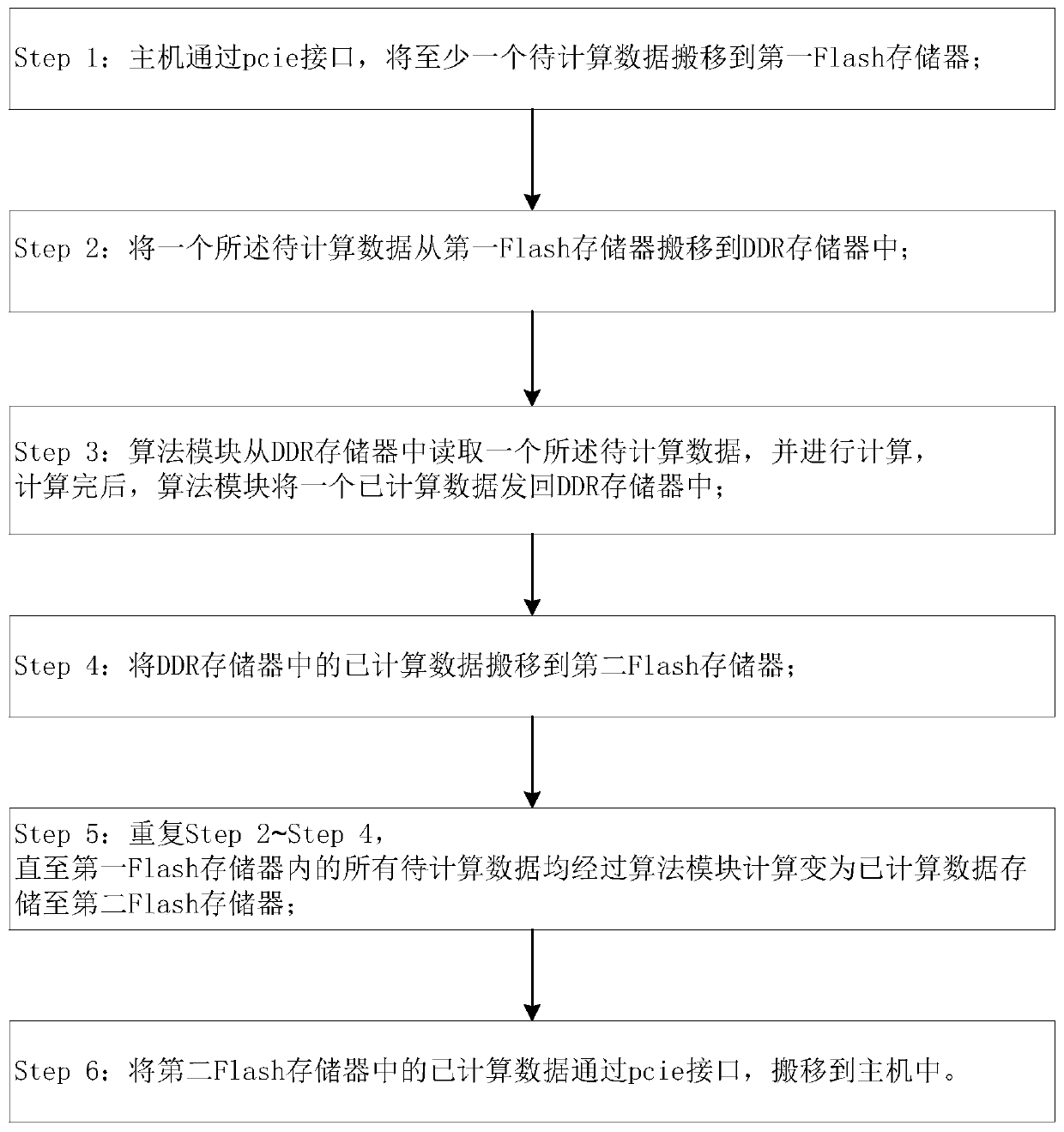

[0039] Such as figure 1 and figure 2 Shown, a kind of FPGA for large-capacity data comprises FPGA controller, and the pcie interface of FPGA controller command communication, Flash controller, DDR controller and algorithm module; Also comprise the Flash memory controlled by described Flash controller and the DDR memory controlled by the DDR controller; the Flash controller communicates with the DDR controller instruction, and the DDR controller communicates with the algorithm module instruction; the data transmission between the pcie interface and the Flash controller, the Data transmission between the Flash controller and the DDR controller, and data transmission between the DDR controller and the algorithm module.

[0040] In the present embodiment, described Flash controller 2 comprises Flash array group A controller and Flash array group B controller; Flash memory 5 has 96 slices, wherein 48 slices of Flash memory 5 connect 12 on the Flash array group A controller For t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More