A sawtooth smoothing method for via array

A technology of via array and hole array, which is applied in the field of PCB simulation, can solve the problems of difficult comparison between test accuracy and simulation accuracy, time rises exponentially, and graphics algorithm redundancy, etc., so as to reduce simulation time, reduce complexity, Reduce the effect of vertices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

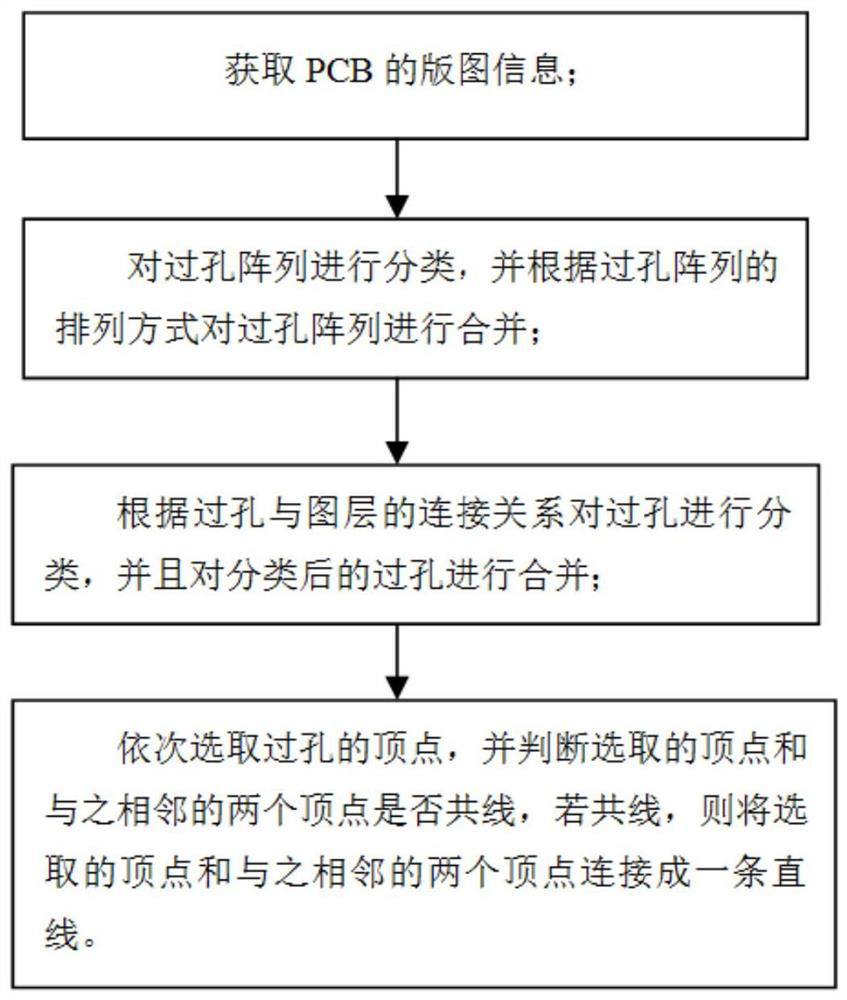

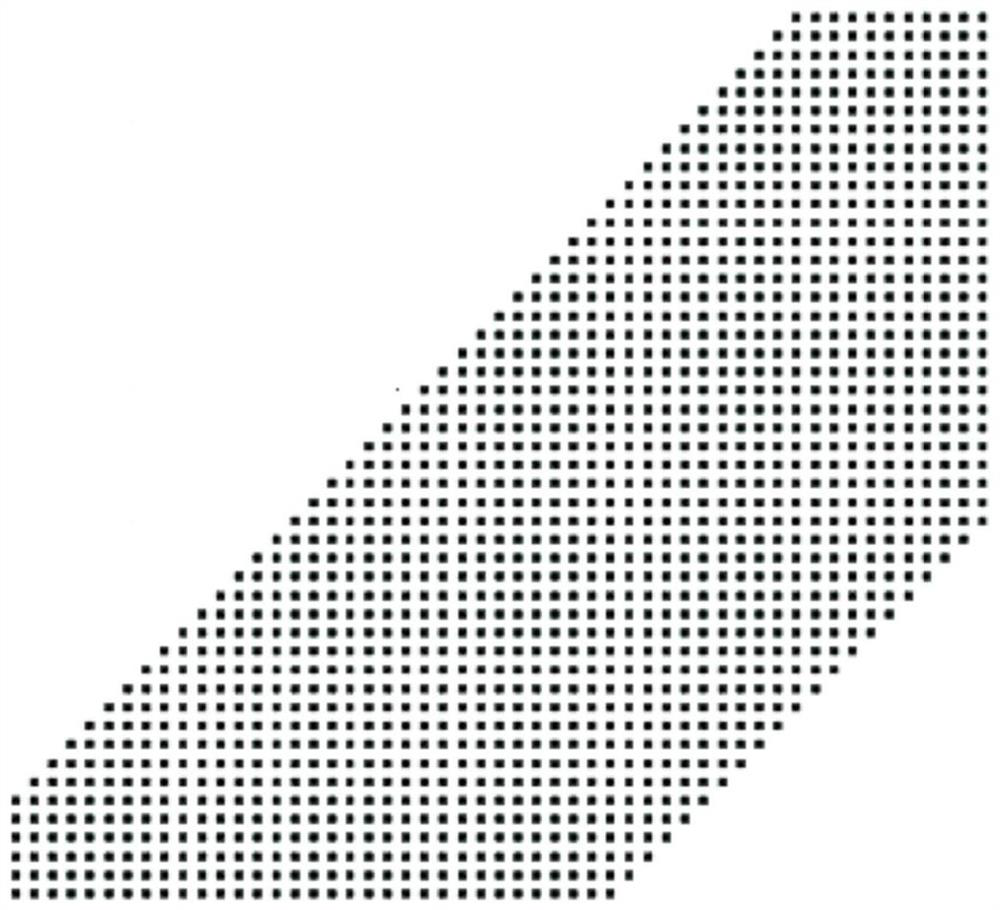

[0029] to combine figure 1 As shown, a zigzag smoothing method for a via array of the present invention first obtains the layout information of the PCB. It is worth noting that the attribute information of all via patterns on the layout can be obtained by scanning the PCB; further, for the via The arrays are classified, and then the via arrays are merged according to the arrangement of the via arrays; then the vias are classified according to the connection relationship between the vias and the layer, and the classified vias are merged; and then sequentially selected The vertex of the via hole, and judge whether the selected vertex is collinear with the two adjacent vertices. If the selected vertex is collinear with the two adjacent vertices, the selected vertex and the adjacent two vertices will be The two vertices are connected into a straight line. It is worth noting that the vertices refer to the small points that form the via hole graphics (such as figure 2 shown).

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More