Message processing method and device

A message processing and message technology, applied in the field of network communication, can solve the problems of extracting quintuple, unable to exert the advantages of multi-core CPU parallel processing, unable to add messages, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

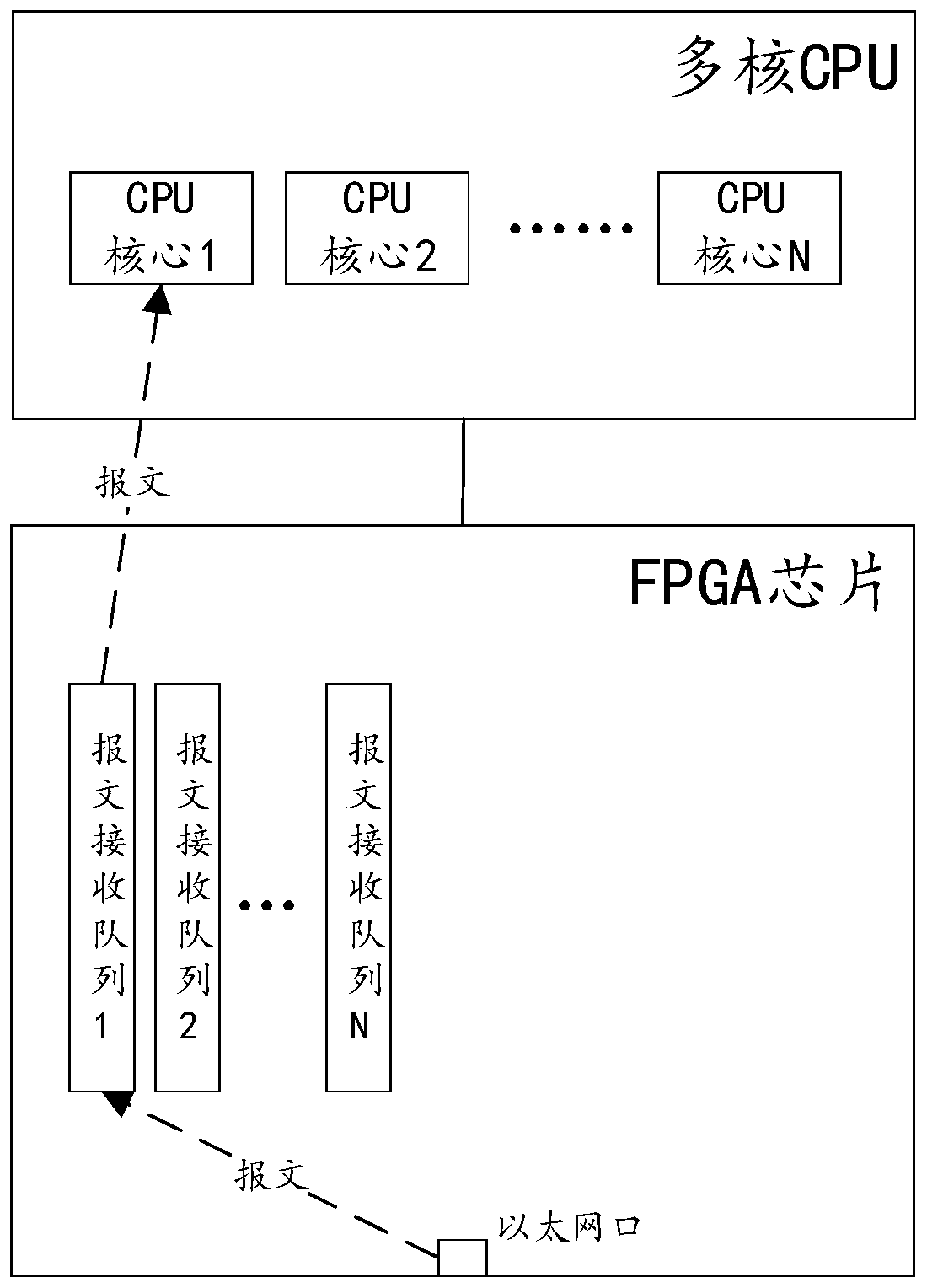

[0037] image 3 It is a schematic diagram of the principle of a multi-core CPU receiving a message through an FPGA chip provided in this embodiment, such as image 3As shown, a multi-core CPU and an FPGA chip are included, wherein the multi-core CPU includes N CPU cores, and N is a natural number greater than 1; the quintuple information contained in the message that different CPU cores of the multi-core CPU are responsible for processing is different; The FPGA chip maintains N message receiving queues; the N message receiving queues are in one-to-one correspondence with the N CPU cores, and the message receiving queues can be allocated by the multi-core CPU according to the number of cores of the multi-core CPU when the device is initialized For the FPGA chip; for each CPU core, the CPU core can obtain a message from the message receiving queue corresponding to the CPU core maintained by the FPGA chip for processing by accessing the FPGA chip; The chip has an Ethernet port a...

Embodiment 2

[0060] Figure 6 It is a schematic diagram of the principle of a multi-core CPU receiving a message through an FPGA chip and sending a message through a network controller provided in this embodiment, as shown in Figure 6 shown in Figure 5 On the basis of the shown architecture, the device also includes a network controller; the switch chip also includes a third-type Ethernet port connected to the Ethernet port of the network controller; the network controller maintains N messages Sending queue; the N message sending queues correspond to N CPU cores one by one, and the message sending queue can be assigned to the network controller by the multi-core CPU according to the number of cores of the multi-core CPU when the device is initialized; each CPU core A network controller may be accessed to insert a message into a message sending queue corresponding to the CPU core in the network controller. After the FPGA chip receives the message from the Ethernet port, it extracts the ...

Embodiment 3

[0077] Figure 8 It is a schematic diagram of the principle of a multi-core CPU receiving and sending messages through an FPGA chip provided in this embodiment. Such as Figure 8 As shown, on the basis of the second embodiment, the network controller is replaced by an FPGA chip, that is, the FPGA chip also maintains N message sending queues. The N message sending queues are in one-to-one correspondence with the N CPU cores, and the message sending queues can be allocated to the FPGA chip by the multi-core CPU according to the number of cores of the multi-core CPU when the device is initialized; each CPU core can access the The FPGA chip inserts a message into the message sending queue corresponding to the CPU core in the FPGA chip. The main difference between Embodiment 3 and Embodiment 2 is that the task of maintaining the message sending queue is also performed by the FPGA chip. Embodiment 3 can be understood by referring to the description of Embodiment 2 above, and will ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com