Rapid method for designing DDR wiring by LAYOUT

A wiring and fast technology, applied in computing, instrumentation, electrical digital data processing, etc., can solve problems such as unstable signals, poor reading and writing quality, and endless repetition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

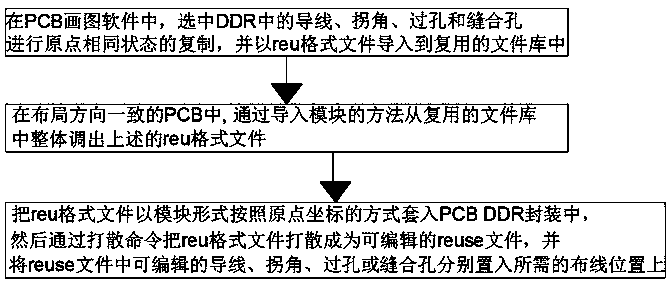

[0012] Example 1. If figure 1 As shown, a quick method for LAYOUT to design DDR wiring, which includes the following steps:

[0013] S1: In the PCB drawing software, select the wires, corners, vias and stitching holes in the DDR to copy the same state of the origin, and import it into the multiplexed file library in the reu format file; S2: PCB with the same layout direction In the method of importing modules, the above-mentioned reu format files are called out from the multiplexed file library as a whole; S3: Insert the reu format files into the PCB DDR package in the form of modules according to the coordinates of the origin, and then use the disperse command to The reu format file is broken up into an editable reuse file, and the editable wires, corners, vias or stitching holes in the reuse file are respectively placed on the required wiring positions. The PCB drawing software is PADS software.

[0014] Through this method: improve the improper mistakes in the design, and ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap