Dynamic latch, data arithmetic unit, chip, computing power board and computing equipment

A dynamic latch and data technology, applied in the direction of voltage/temperature change compensation, reliability improvement and modification, etc., can solve the problems of data loss, data dynamic leakage, etc., and achieve the effect of improving stability, enhancing security and accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

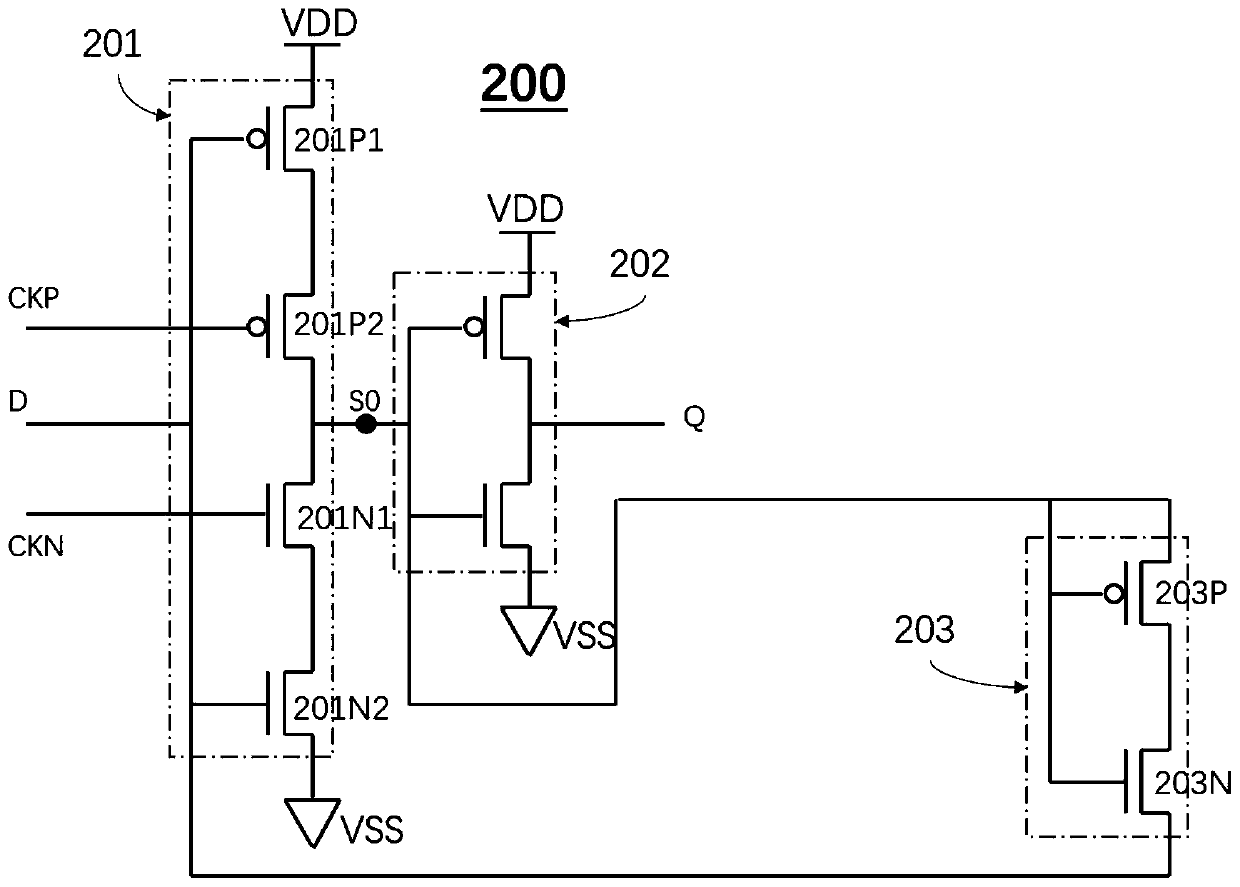

[0063] figure 2 It is a schematic diagram of a circuit structure of a dynamic latch according to an embodiment of the present invention. Such as figure 2 As shown, the dynamic latch 200 includes an input terminal D, an output terminal Q, a clock signal terminal CKN, a clock signal terminal CKP, a data latch unit 201 , a data holding unit 202 and a leakage compensation unit 203 . The data latch unit 201 and the data holding unit 202 are connected in series between the input terminal D and the output terminal Q, and a node S0 is formed between the data latch unit 201 and the data holding unit 202 . The leakage compensation unit 203 is electrically connected between the node S0 and the input terminal D. As shown in FIG. Among them, the input terminal D is used to input data, the output terminal Q is used to output the data input by the input terminal D, the clock signal terminal CKN and the clock signal terminal CKP are used to provide the clock signal CKN and the clock signa...

Embodiment 2

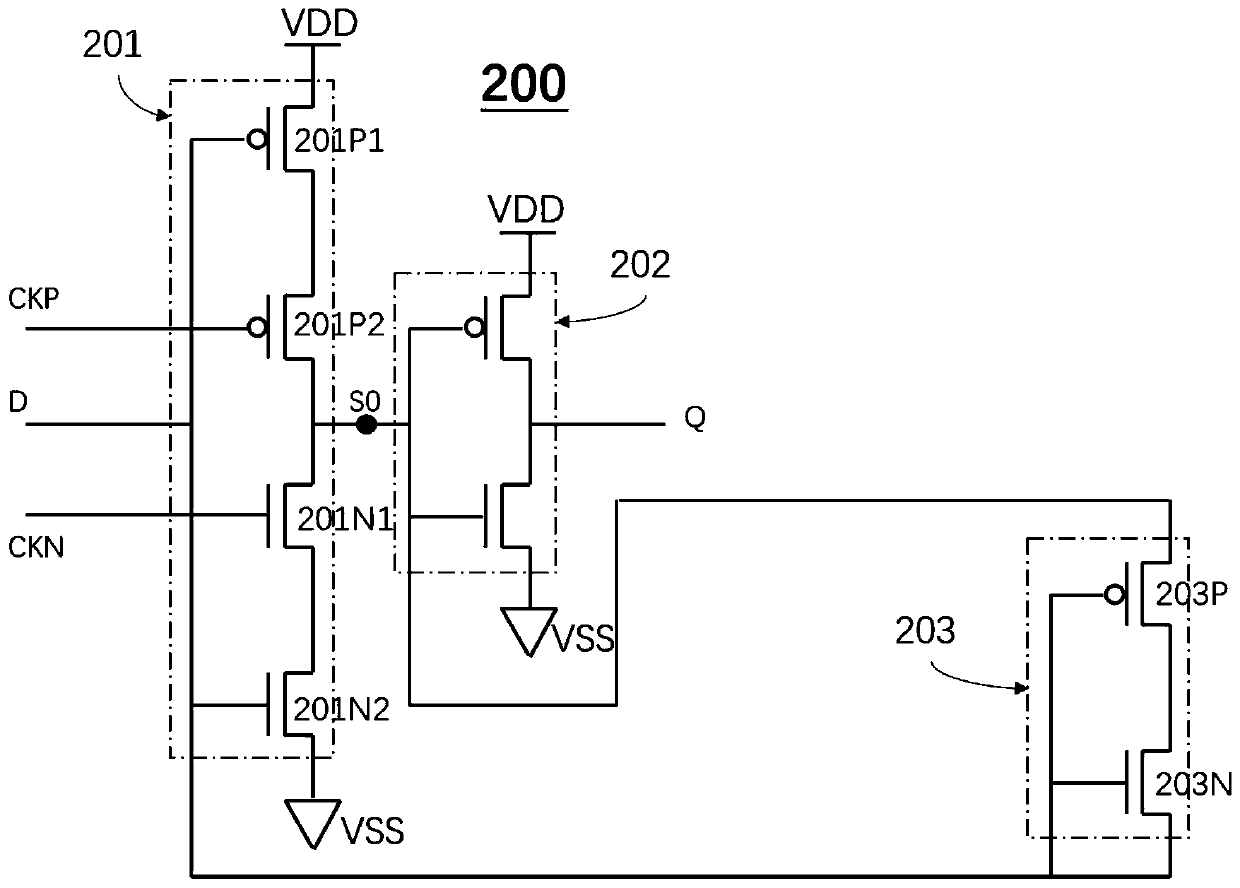

[0076] image 3 It is a schematic diagram of a circuit structure of a dynamic latch according to another embodiment of the present invention. Such as image 3 shown, with figure 2 The difference of the illustrated embodiment is that in this embodiment, in the leakage compensation unit 203 , the gate terminals of the PMOS transistor 203P and the NMOS transistor 203N are connected in parallel and electrically connected to the input terminal D. As shown in FIG.

[0077] Since the gate terminals of the PMOS transistor 203P and the NMOS transistor 203N are also electrically connected to the input terminal D, driven by a signal of the same level, the PMOS transistor 203P and the NMOS transistor 203N will not be turned on at the same time, and only one of them will be turned on. state, the other is in cutoff state. For example, when the potential of the input terminal D is at a high level, the PMOS transistor 203P is in an off state, and the NMOS transistor 203N is in a conductiv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com