Method for packaging densely-arranged semiconductor chips for Internet of Things terminal

A technology of IoT terminal and packaging method, which is applied in the direction of semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., and can solve the problems that the connection between the chip and the pin is easy to be torn off, the chip is damaged, and the chip is pulled. , to achieve the effect of good fixing effect, simple structure and good bonding performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

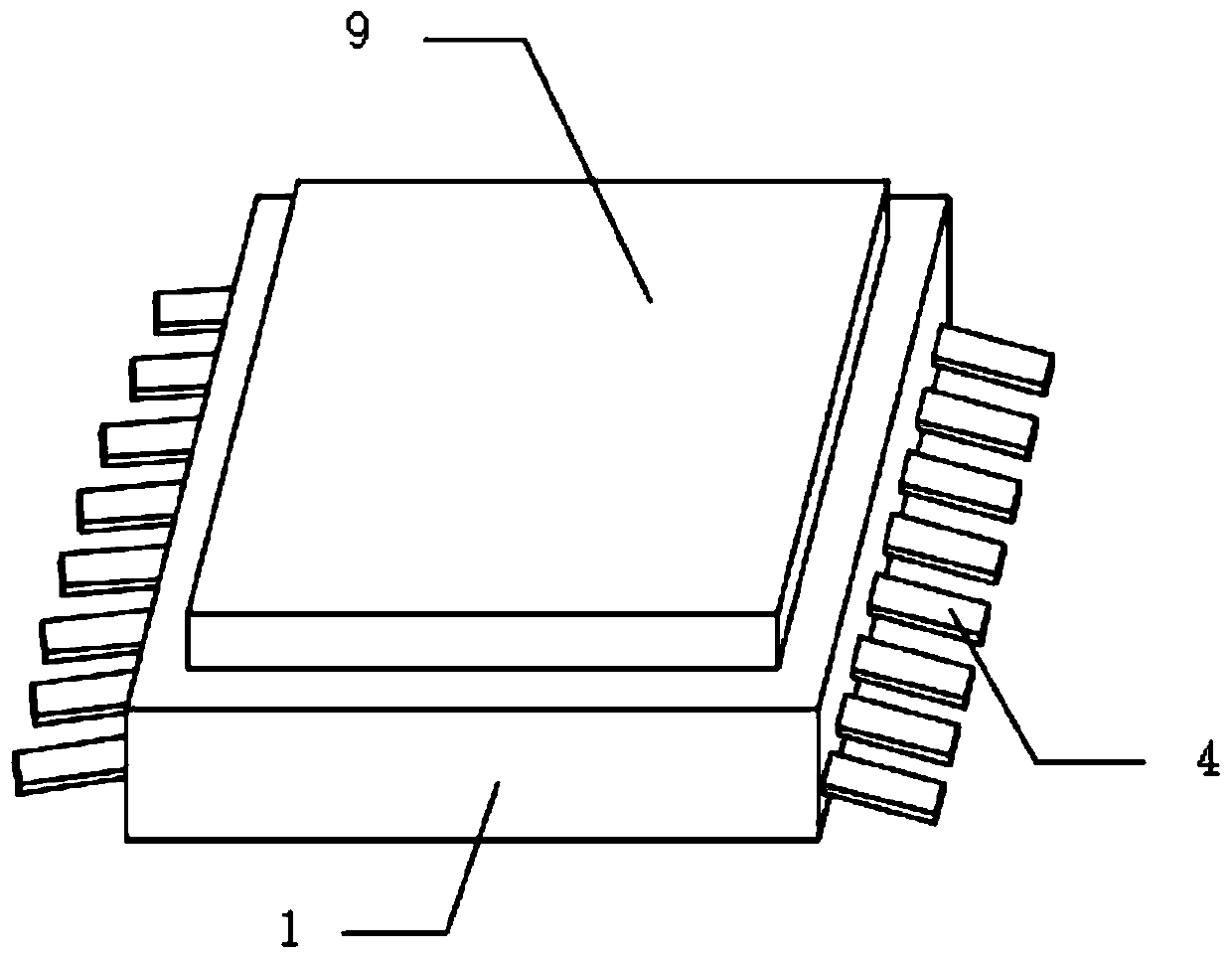

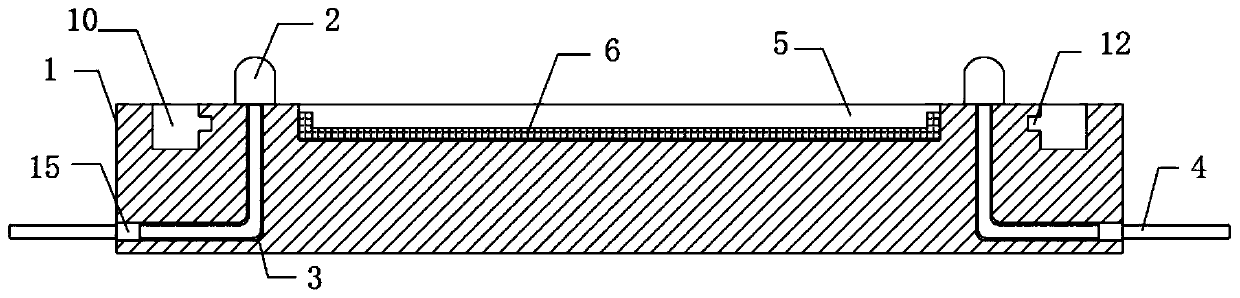

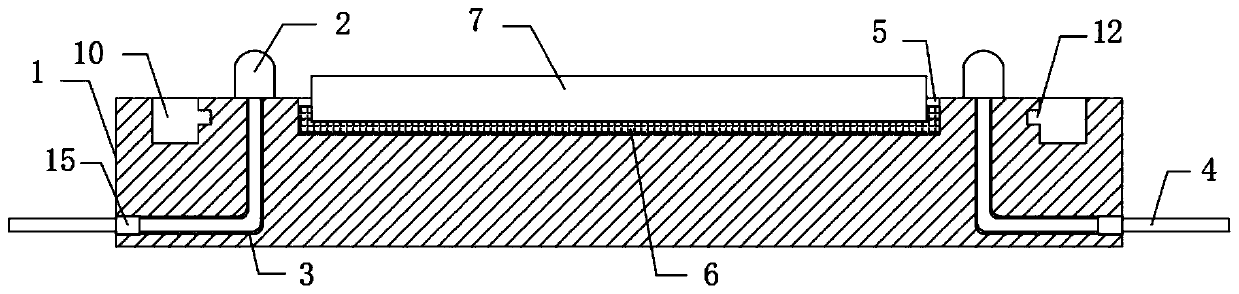

[0044] see Figure 1-7 , a packaging method for densely arranging semiconductor chips for Internet of Things terminals, including a lower housing 1, see figure 1 , the upper surface of the lower casing 1 is provided with a placement groove 5, and the upper surface of the lower casing 1 is fixedly connected with two sets of conductive columns 2, and the two sets of conductive columns 2 are respectively located on both sides of the placement groove 5, and the lower casing 1 There is a perforation 3 inside, the shape of the perforation 3 is L-shaped, and the lower opening of the perforation 3 is filled with insulating glue 15, because there is a corner on the L-shaped perforation 3, so that when the leaked pin 4 is involved At this time, the hole wall at the corner can play a counterweight role to prevent the conductive column 2 from being affected, the insulating glue 15 plays the role of insulation, and also plays the role of sealing, and the perforation 3 is located below the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More