Edge defect inspection method

An inspection method and edge defect technology, applied in the field of inspection, can solve problems such as failure of protective structure or undetected cracks, distortion of grain edge search, undetected cracks of protective structure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

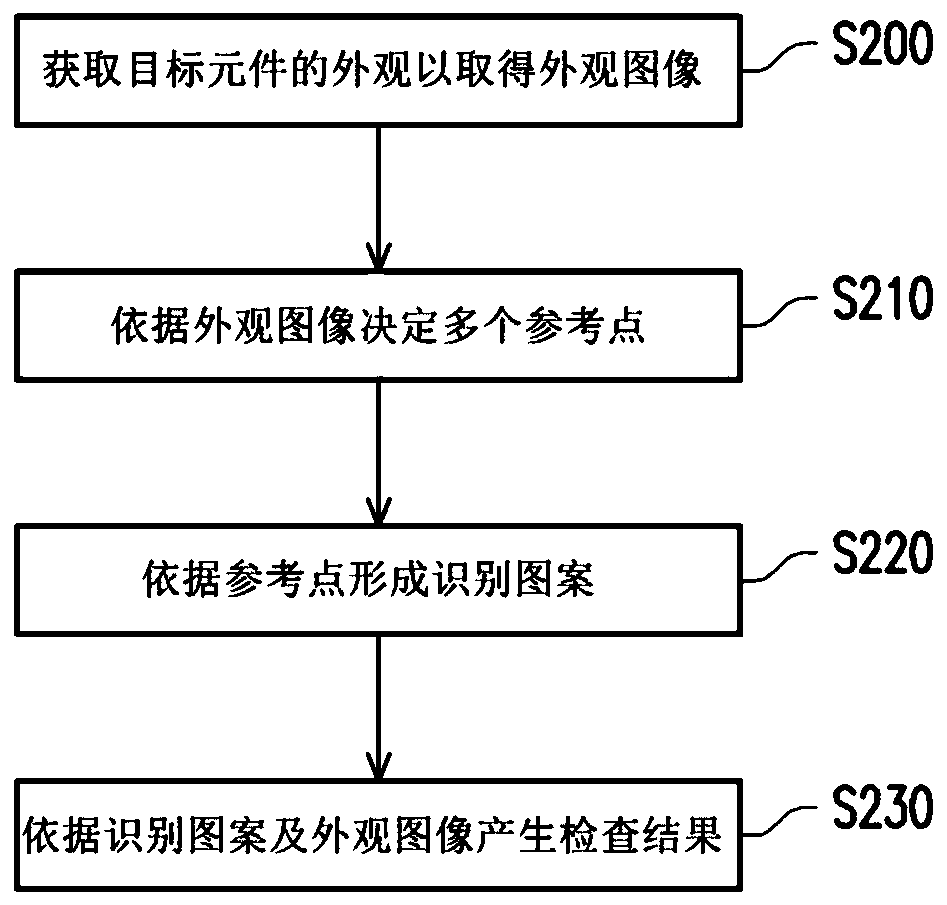

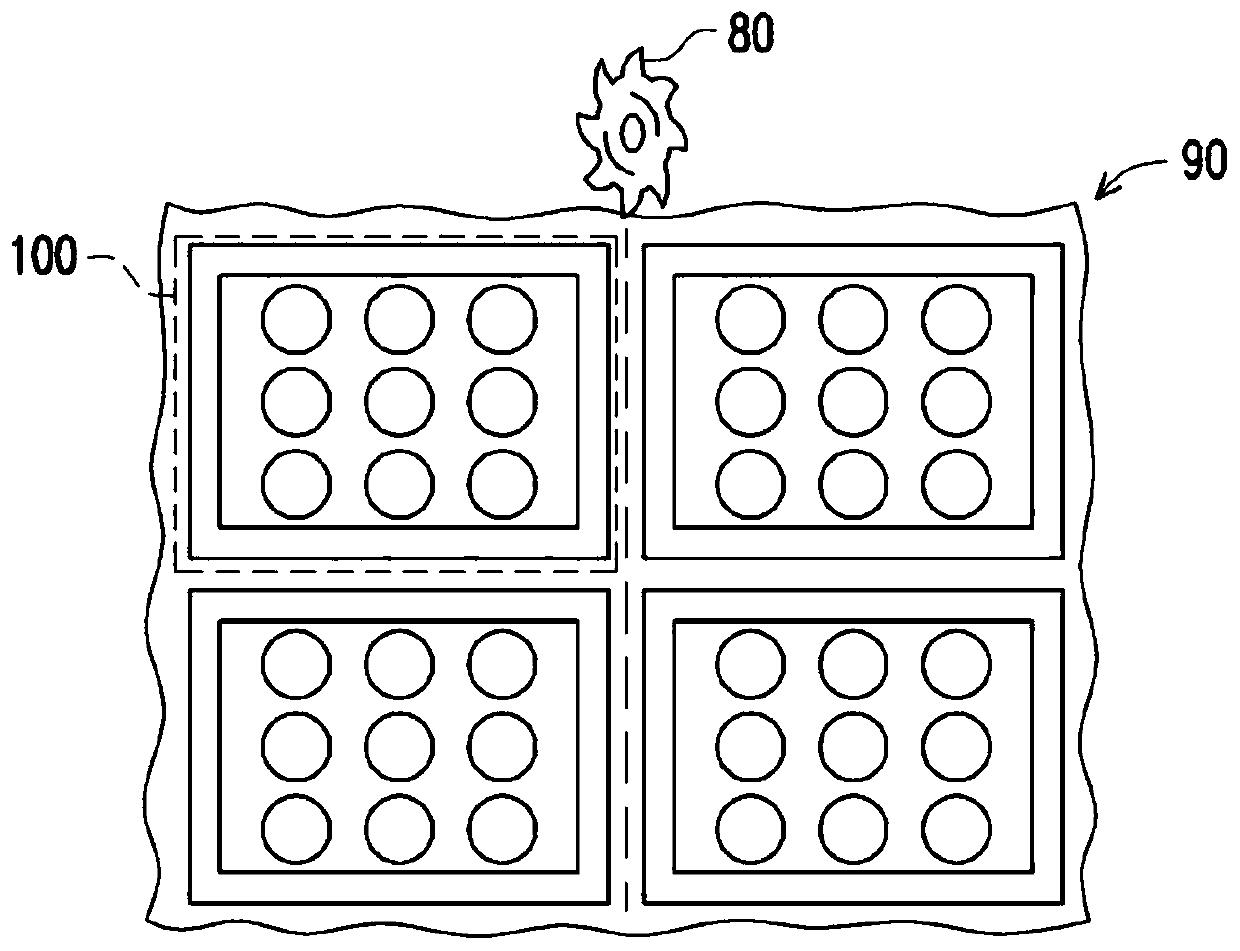

[0036] figure 1 It is a flow chart of steps of an edge defect inspection method according to an embodiment of the present invention. figure 2 It is a schematic diagram of cutting out target elements in an embodiment of the present invention. Please refer to figure 1 and figure 2 . The present embodiment provides an edge defect inspection method, and the edge defect inspection method is suitable for inspecting a target device 100 , such as a die or a WLC package separated from a wafer dicing unit. In this embodiment, the target component 100 is a wafer-level chip package cut out of a wafer 90 by the dicing device 80, such as figure 2 shown, but the present invention is not limited thereto.

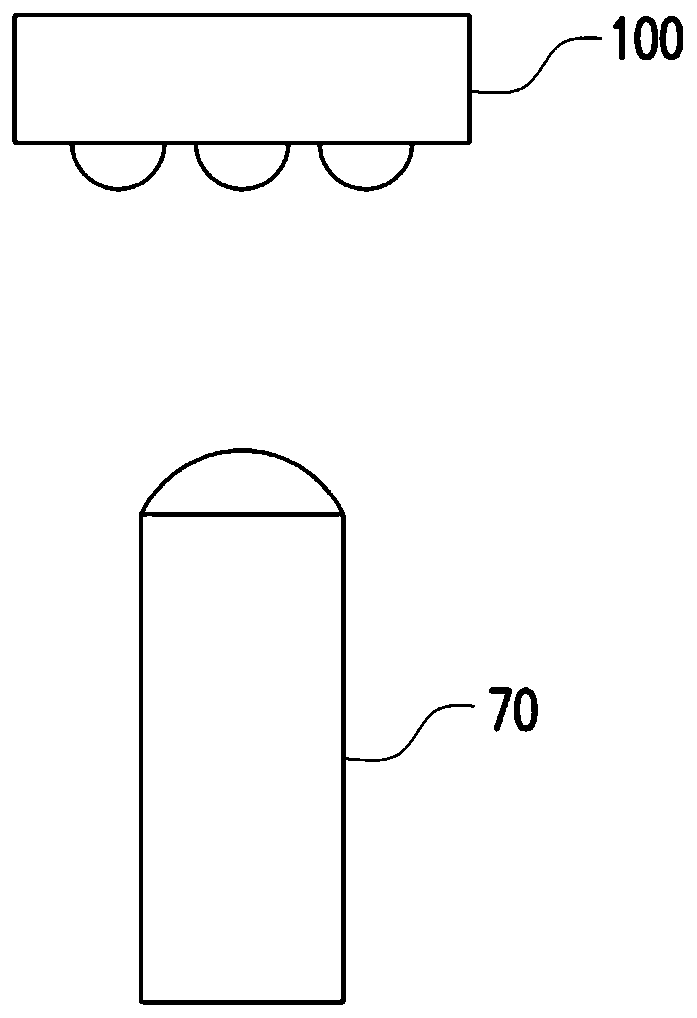

[0037] image 3 It is a schematic diagram of the appearance of the acquired target element in an embodiment of the present invention. Figure 4A to Figure 4D It is a top view of an edge defect inspection method of a target component in an embodiment of the present invention. Plea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More