ADC sampling data recognition method and system, integrated circuit and decoding device

A technology of sampling data and identification method, applied in the direction of code conversion, electrical components, analog/digital conversion, etc., can solve the problem of unidentifiable starting position and synchronization state of sampling data, and achieve real-time synchronization, simplify synchronization and post-calibration steps, the effect of eliminating synchronization errors and data jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

other Embodiment approach

[0053] In other implementation manners, step 130 combines the serial data and the generated preamble sequence to obtain new serial data, including:

[0054] If the number of preambles in the preamble sequence has been limited when the preamble sequence is generated, the generated preamble sequence is added before the serial data or replaces the serial data to obtain new serial data, or each time a preamble is generated, The generated preambles are added before or replace the serial data until a predetermined number of preambles are generated.

[0055] This embodiment can reduce the power consumption of the preamble sequence generation device.

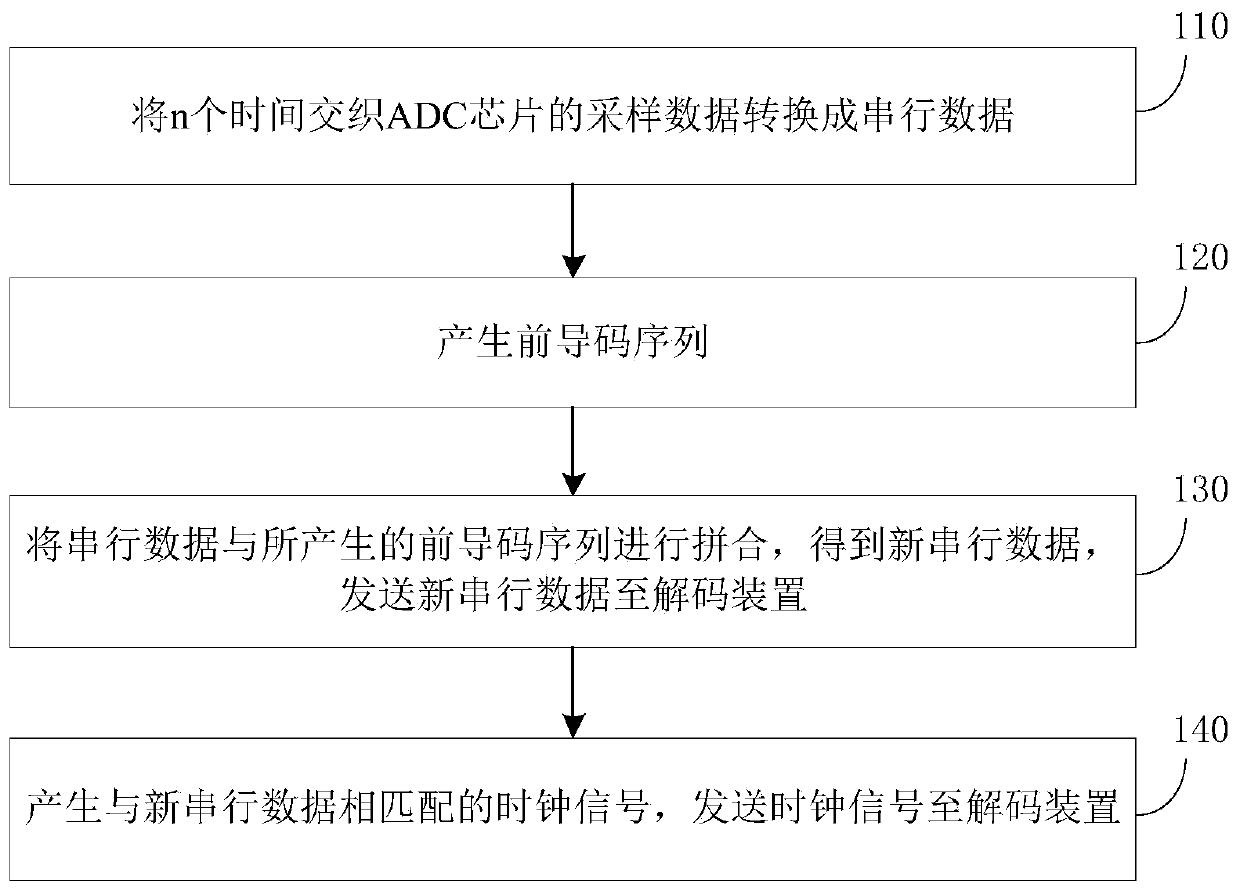

[0056] Step 140, generating a clock signal matching the new serial data, sending the clock signal to the decoding device, and the decoding device identifies the sampling data according to the new serial data and the clock signal. The splicing process changes the start and end positions of the data, which will lead to changes in the tim...

other Embodiment approach

[0058] In other embodiments, in order to support a common decoding device and facilitate decoding, the rising and falling edges of the clock signal are aligned with the data center of the new serial data.

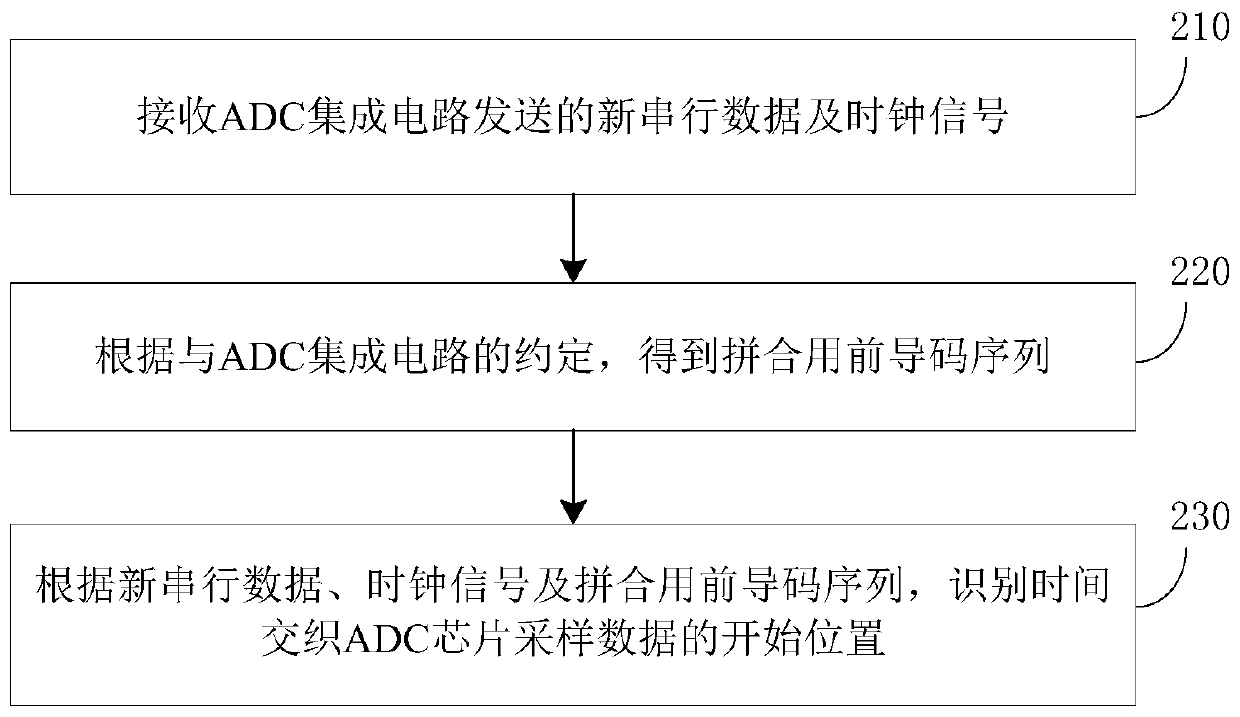

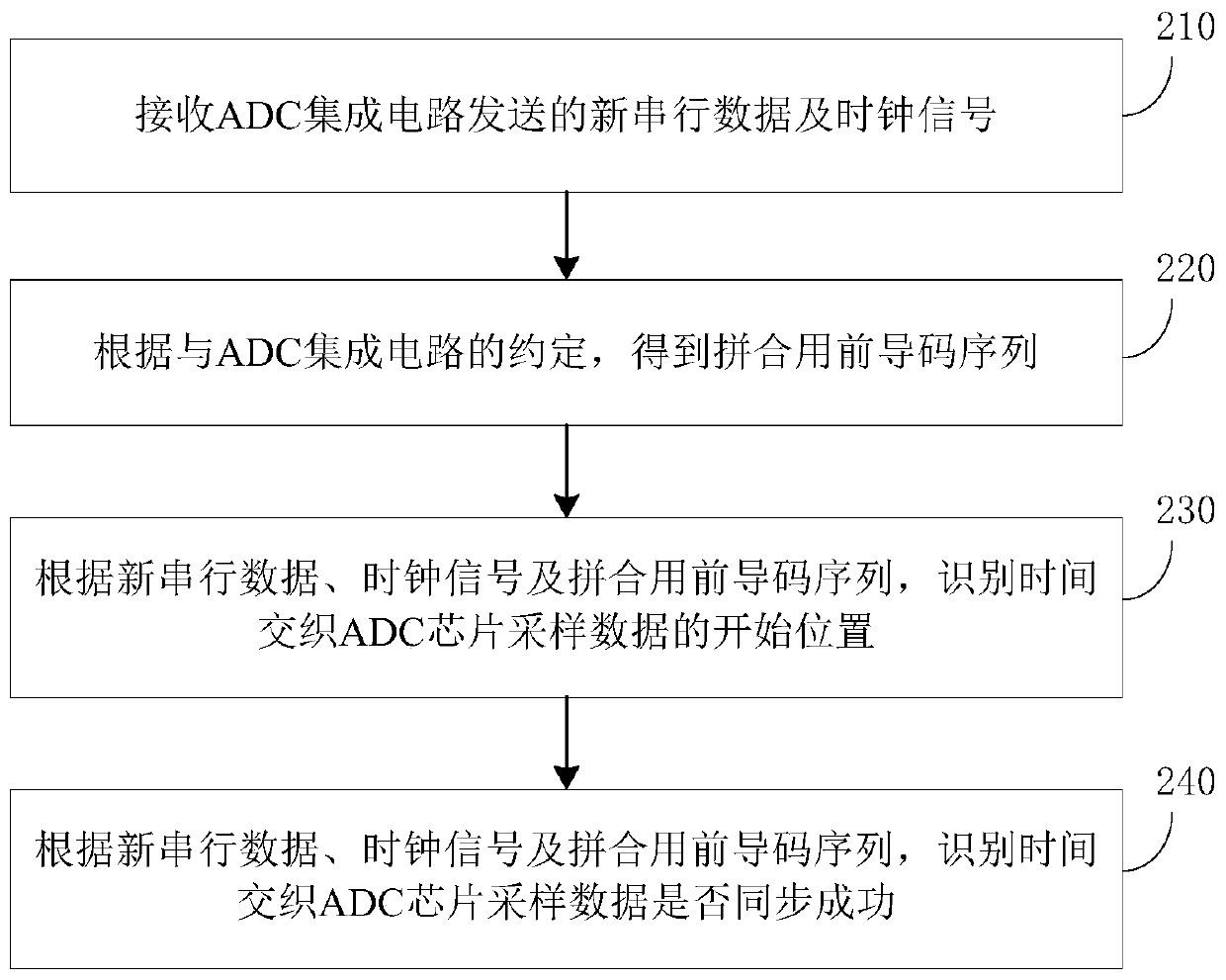

[0059] Correspondingly, in one embodiment of the present invention, there is also provided a figure 1 The ADC sampling data identification method applicable to the decoding device used in conjunction, such as figure 2 shown, including:

[0060] Step 210, receiving the new serial data and clock signal sent by the ADC integrated circuit, wherein the new serial data is formed by combining the serial data and the preamble sequence, and the serial data is converted from the sampling data of n time-interleaved ADC chips Yes, the clock signal matches the new serial data.

[0061] Step 220, according to the agreement with the ADC integrated circuit, obtain the preamble sequence for splicing.

[0062] Step 230, according to the new serial data, the clock signal and the preamble ...

other Embodiment approach

[0082] In other embodiments, the combination module 430 combines the serial data and the generated preamble sequence to obtain new serial data, including: if the number of preambles in the preamble sequence has been limited when the preamble sequence is generated, then Add the generated preamble sequence to the serial data or replace the serial data to obtain new serial data, or each time a preamble is generated, add the generated preamble to the serial data or replace the serial data until a predetermined number of preambles.

[0083] The supporting clock generation module 440 is used to generate a clock signal matching the new serial data, and send the clock signal to the decoding device. In some embodiments, in order to support a general-purpose decoding device and facilitate decoding, the clock signal generated by the supporting clock generation module is a DDR clock signal (that is, the clock frequency is half of the data frequency), and the rising and falling edges of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More